本文將對(duì)源同步定時(shí)如何優(yōu)化高速接口時(shí)序裕量進(jìn)行討論。時(shí)序預(yù)算是對(duì)系統(tǒng)正常工作所需時(shí)序參數(shù)或時(shí)序要求的計(jì)算。

2012-03-20 10:46:32 2443

2443

靜態(tài)時(shí)序分析是檢查IC系統(tǒng)時(shí)序是否滿足要求的主要手段。以往時(shí)序的驗(yàn)證依賴于仿真,采用仿真的方法,覆蓋率跟所施加的激勵(lì)有關(guān),有些時(shí)序違例會(huì)被忽略。此外,仿真方法效率非常的低,會(huì)大大延長(zhǎng)產(chǎn)品的開發(fā)周期

2020-11-25 11:03:09 8918

8918

時(shí)序分析是FPGA設(shè)計(jì)中永恒的話題,也是FPGA開發(fā)人員設(shè)計(jì)進(jìn)階的必由之路。慢慢來,先介紹時(shí)序分析中的一些基本概念。

2022-10-21 09:28:58 1283

1283 同步電路設(shè)計(jì)中,時(shí)序是一個(gè)主要的考慮因素,它影響了電路的性能和功能。為了驗(yàn)證電路是否能在最壞情況下滿足時(shí)序要求,我們需要進(jìn)行靜態(tài)時(shí)序分析,即不依賴于測(cè)試向量和動(dòng)態(tài)仿真,而只根據(jù)每個(gè)邏輯門的最大延遲來檢查所有可能的時(shí)序違規(guī)路徑。

2023-06-28 09:35:37 490

490

時(shí)序路徑作為時(shí)序約束和時(shí)序分析的物理連接關(guān)系,可分為片間路徑和片內(nèi)路徑。

2023-08-14 17:50:02 452

452

1。時(shí)序分析就是分析前級(jí)的數(shù)據(jù)是否在后一個(gè)時(shí)鐘沿的數(shù)據(jù)有效窗口里面,就是說在整個(gè)窗口內(nèi)部,數(shù)據(jù)都應(yīng)該保持有效,如果不滿足時(shí)間窗的前端,就是setup違例,如果不滿足時(shí)間窗的后端,那么就是hold違例

2014-12-29 14:53:00

邏輯電路分為組合邏輯電路和時(shí)序邏輯電路。第四章已經(jīng)學(xué)習(xí)了組合邏輯電路的分析與設(shè)計(jì)的方法,這一章我們來學(xué)習(xí)時(shí)序電路的分析與設(shè)計(jì)的方法。在學(xué)習(xí)時(shí)序邏輯電路時(shí)應(yīng)注意的重點(diǎn)是常用時(shí)序部件的分析與設(shè)計(jì)這一

2018-08-23 10:28:59

這種時(shí)序圖第一次見,不會(huì)分析。1.希望技術(shù)支持或者哪位大神從編程的角度分析一下這個(gè)時(shí)序。2.上面的線為什么是曲線,代表什么意思?3.CLK正負(fù)的產(chǎn)生源可否是由DSP的引腳產(chǎn)生,經(jīng)反相器,通過電容,形成兩路互補(bǔ)的信號(hào)?附件圖像 1.png35.7 KB

2018-12-03 09:15:27

1、AHB傳輸?shù)?b class="flag-6" style="color: red">時(shí)序圖分析正文1:AHB章節(jié)最后再復(fù)習(xí)一遍多主機(jī)的概念:總線是被總線上所有的部件所共享的一組通路(連線),對(duì)于支持多主機(jī)的總線,如果某一個(gè)主機(jī)想要與其他的部件進(jìn)行通信(獲得

2022-06-09 17:45:33

DAC時(shí)序分析

2021-07-29 09:14:26

。本次沙龍主要介紹怎樣通過Quartus? II軟件中的TimeQuest時(shí)序分析器來約束并分析單倍數(shù)據(jù)速率源同步接口。會(huì)議焦點(diǎn) 1、源同步接口相對(duì)于公共時(shí)鐘系統(tǒng)接口有何優(yōu)點(diǎn)? 2、怎樣編寫SDC

2014-12-31 14:21:17

FPGA時(shí)序分析系統(tǒng)時(shí)序基礎(chǔ)理論對(duì)于系統(tǒng)設(shè)計(jì)工程師來說,時(shí)序問題在設(shè)計(jì)中是至關(guān)重要的,尤其是隨著時(shí)鐘頻率的提高,留給數(shù)據(jù)傳輸?shù)挠行ёx寫窗口越來越小,要想在很短的時(shí)間限制里,讓數(shù)據(jù)信號(hào)從驅(qū)動(dòng)端完整

2012-08-11 17:55:55

可以分析一下這個(gè)接口的時(shí)序要求,然后對(duì)其進(jìn)行約束。這個(gè)輸出的信號(hào),其實(shí)是很典型的源同步接口,它的時(shí)鐘和數(shù)據(jù)都是由FPGA來驅(qū)動(dòng)產(chǎn)生的。一般的源同步接口的寄存器模型如圖8.25所示。在我們的這個(gè)系統(tǒng)中

2015-07-29 11:19:04

CMOS攝像頭接口時(shí)序設(shè)計(jì)2實(shí)際分析(特權(quán)同學(xué)版權(quán)所有)本文節(jié)選自特權(quán)同學(xué)的圖書《FPGA設(shè)計(jì)實(shí)戰(zhàn)演練(邏輯篇)》(特權(quán)同學(xué)版權(quán)所有)配套例程下載鏈接:http://pan.baidu.com/s

2015-08-14 11:24:01

CMOS攝像頭接口時(shí)序設(shè)計(jì)5時(shí)序報(bào)告(特權(quán)同學(xué)版權(quán)所有)本文節(jié)選自特權(quán)同學(xué)的圖書《FPGA設(shè)計(jì)實(shí)戰(zhàn)演練(邏輯篇)》(特權(quán)同學(xué)版權(quán)所有)配套例程下載鏈接:http://pan.baidu.com/s

2015-08-19 21:58:55

TC1728沒有LIN接口,只有UART接口。可以用UART接口實(shí)現(xiàn)LIN接口嗎?

2024-02-06 06:51:22

自己做了一個(gè)工程,靜態(tài)時(shí)序分析的結(jié)果CLK信號(hào)的SLACK是負(fù)值(-7.399ns),書上說該值是負(fù)值時(shí)說明時(shí)序不對(duì),但是我感覺時(shí)序仿真的結(jié)果是對(duì)的。是不是時(shí)序仿真波形正確就不用管靜態(tài)時(shí)序分析的結(jié)果了?請(qǐng)高手指點(diǎn)

2010-03-03 23:22:24

如題:fpga時(shí)序分析一般都做哪些分析我自己研究時(shí)序分析也有一段時(shí)間了 ,從理論到altera的timequest,差不多都了解了 ,但就是不知道一個(gè)具體的項(xiàng)目都要做哪些約束。求大神知道,或者有沒有這方面的資料(網(wǎng)上資料基本都看過了,沒有說明具體項(xiàng)目的)。

2012-10-22 22:20:32

spi接口和uart接口區(qū)別,一、SPII2C UART通信速率比較:SPI > I2C > UART1、同步通信>異步通信;2、同步通信時(shí)必須有一根時(shí)鐘線連接傳輸?shù)膬啥?3、都是

2021-07-21 06:24:58

嗨,您能告訴我與vivado時(shí)序分析相關(guān)的用戶指南嗎?謝謝

2020-03-16 08:14:45

轉(zhuǎn)自:VIVADO時(shí)序分析練習(xí)時(shí)序分析在FPGA設(shè)計(jì)中是分析工程很重要的手段,時(shí)序分析的原理和相關(guān)的公式小編在這里不再介紹,這篇文章是小編在練習(xí)VIVADO軟件時(shí)序分析的筆記,小編這里

2018-08-22 11:45:54

什么是時(shí)序分析?時(shí)序約束的作用是什么?FPGA組成的三要素分別是哪些?

2021-09-18 06:05:51

光以太網(wǎng)通信不正常。經(jīng)過分析得到是FPGA通MII接口和PHY的時(shí)序不滿足。如圖 9所示為MII接口的時(shí)序圖,時(shí)序不滿足分為TX_CLK和RX_CLK。其一是PHY輸出的TX_CLK和FPGA依據(jù)

2018-04-03 11:19:08

以下針對(duì)目前項(xiàng)目所用到的SRAM時(shí)序進(jìn)行分析,同時(shí)也對(duì)SRAM應(yīng)用在STM32F4上進(jìn)行詳細(xì)解說。以此也可以類推出NAND/PSRAM等時(shí)序的應(yīng)用技巧。時(shí)序當(dāng)前用到的是模式A,其中讀時(shí)序如下。圖片截

2022-01-07 07:20:20

硬件_8080接口LCD時(shí)序分析參考資料,GIT倉庫里:8080接口LCD接口原理圖:其他資料\STM32F103\原理圖\100ASK_STM32F103_V10_0707FINAL.pdfLCD

2022-03-01 06:02:46

請(qǐng)教如何做時(shí)序分析

2013-06-01 22:45:04

靜態(tài)時(shí)序分析STA是什么?靜態(tài)時(shí)序分析STA的優(yōu)點(diǎn)以及缺點(diǎn)分別有哪些呢?

2021-11-02 07:51:00

高速電路的時(shí)序分析電路中,數(shù)據(jù)的傳輸一般都是在時(shí)鐘對(duì)數(shù)據(jù)信號(hào)進(jìn)行有序的收發(fā)控制下進(jìn)行的。芯片只能按規(guī)定的時(shí)序發(fā)送和接收數(shù)據(jù),過長(zhǎng)的信號(hào)延遲或信號(hào)延時(shí)匹配不當(dāng)都會(huì)影響芯片的建立和保持時(shí)間,導(dǎo)致芯片無法

2012-08-02 22:26:06

在“圓夢(mèng)小車DIY 套件”設(shè)計(jì)中,忽略了PC 機(jī)側(cè)的接口需求,使用了一個(gè)比較“湊合”的方案,即使用一塊擴(kuò)展版(YM1-PCB2)為基礎(chǔ),焊上USB 轉(zhuǎn)UART 及無線接口部分,這樣雖然

2008-09-03 09:59:48 88

88 Cadence高速PCB的時(shí)序分析:列位看觀,在上一次的連載中,我們介紹了什么是時(shí)序電路,時(shí)序分析的兩種分類(同步和異步),并講述了一些關(guān)于SDRAM 的基本概念。這一次的連載中,

2009-07-01 17:23:27 0

0 Cadence 高速 PCB 的時(shí)序分析 1.引言 時(shí)序分析,也許是 SI 分析中難度最大的一部分。我懷著滿腔的期許給 Cadence 的資深工程師發(fā)了一封 e-mail,希望能夠得到一份時(shí)序分析的案

2010-04-05 06:37:13 0

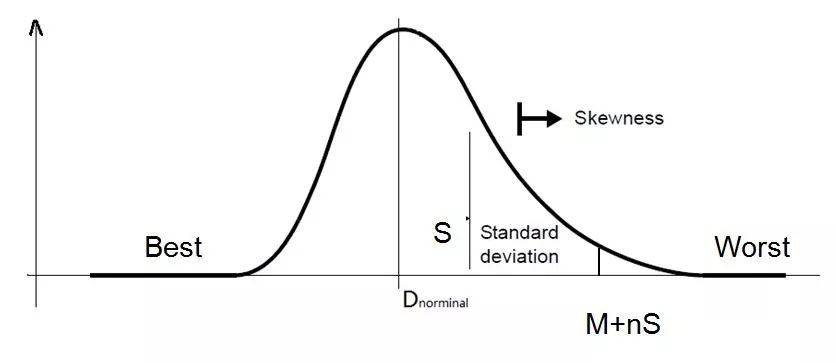

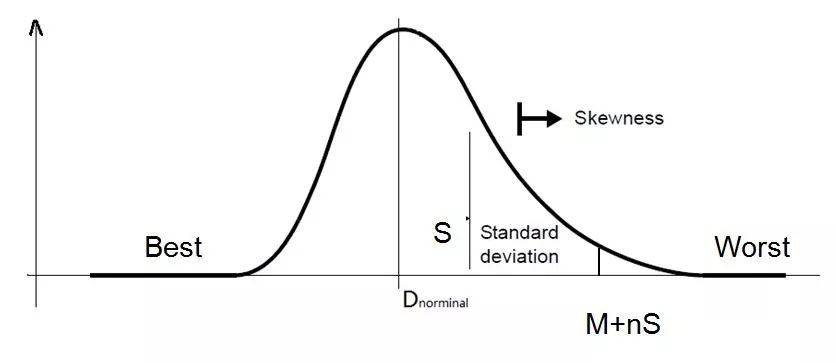

0 信號(hào)完整性和時(shí)序分析的模式變化:簡(jiǎn)單的接口分析經(jīng)驗(yàn)法則在分析現(xiàn)代高速接口(如DDR2、PCI Express和SATA-II)時(shí)非常不合適。隨著新興標(biāo)準(zhǔn)(如DDR3 和5-10 Gbps串行接口)逐漸普及,

2010-04-27 08:25:54 70

70 時(shí)序約束與時(shí)序分析 ppt教程

本章概要:時(shí)序約束與時(shí)序分析基礎(chǔ)常用時(shí)序概念QuartusII中的時(shí)序分析報(bào)告

設(shè)置時(shí)序約束全局時(shí)序約束個(gè)別時(shí)

2010-05-17 16:08:02 0

0 靜態(tài)時(shí)序概念,目的

靜態(tài)時(shí)序分析路徑,方法

靜態(tài)時(shí)序分析工具及邏輯設(shè)計(jì)優(yōu)化

2010-07-09 18:28:18 129

129 本文詳細(xì)分析了ADSL系統(tǒng)中ATM層和物理層之間的UTOPIA LEVEL2接口時(shí)序,采用FPGA實(shí)現(xiàn)了UTOPIA接口設(shè)計(jì),應(yīng)用在ADSL系統(tǒng)中,數(shù)據(jù)收發(fā)正確,工作穩(wěn)定;該方案的實(shí)現(xiàn)對(duì)解決現(xiàn)有專門通信芯

2010-07-28 16:54:10 19

19 在討論時(shí)序邏輯電路的分析與設(shè)計(jì)之前,讓我們先回顧一下在第四章中介紹過的時(shí)序電路結(jié)構(gòu)框圖和一些相關(guān)術(shù)語。時(shí)序電路的結(jié)構(gòu)框圖如圖5.1所示.。

2010-08-13 15:24:35 69

69 時(shí)序邏輯電路的分析方法

1. 時(shí)序邏輯電路的特點(diǎn) 在時(shí)序邏輯電路中,任意時(shí)刻的輸出信號(hào)不僅取決于當(dāng)時(shí)的輸入信

2009-04-07 23:18:11 8146

8146

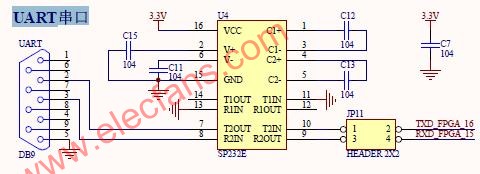

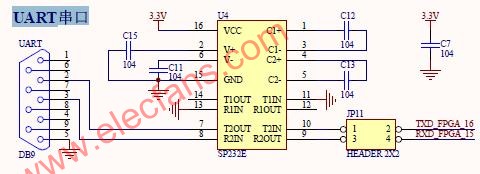

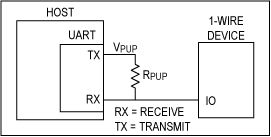

UART串口接口電路(采用SP232E)

2010-03-17 09:23:28 8584

8584

跳變點(diǎn)是所有重要時(shí)序分析工具中的一個(gè)重要概念。跳變點(diǎn)被時(shí)序分析工具用來計(jì)算設(shè)計(jì)節(jié)點(diǎn)上的時(shí)延與過渡值。跳變點(diǎn)的有些不同含義可能會(huì)被時(shí)序分析工程師忽略。而這

2010-09-15 10:48:06 1461

1461

介紹了采用STA (靜態(tài)時(shí)序分析)對(duì)FPGA (現(xiàn)場(chǎng)可編程門陣列)設(shè)計(jì)進(jìn)行時(shí)序驗(yàn)證的基本原理,并介紹了幾種與STA相關(guān)聯(lián)的時(shí)序約束。針對(duì)時(shí)序不滿足的情況,提出了幾種常用的促進(jìn) 時(shí)序收斂的方

2011-05-27 08:58:50 70

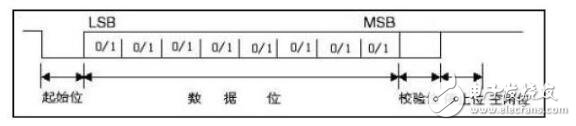

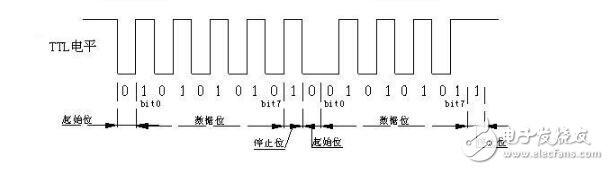

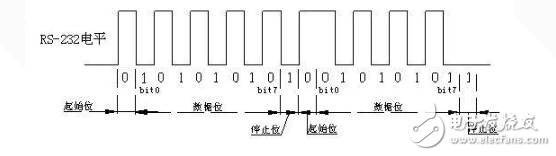

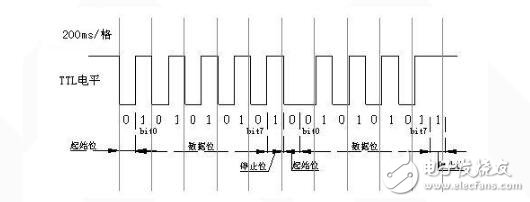

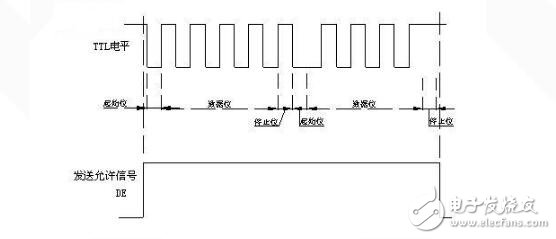

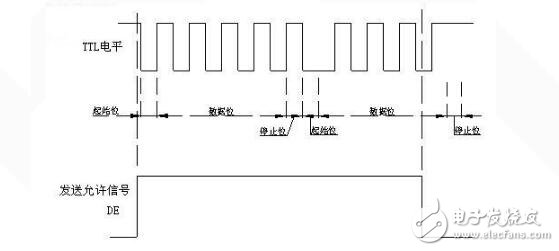

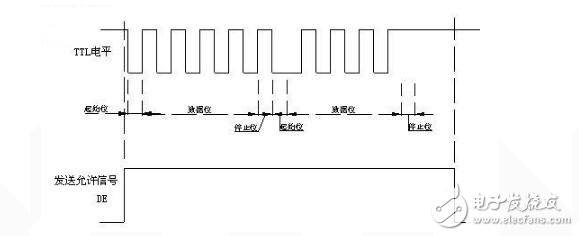

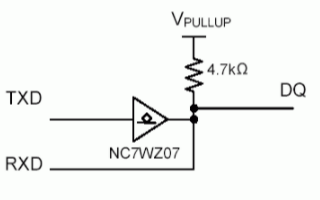

70 UART(Universal Asynchronous Receiver Transmitter,通用異步收發(fā)器)是廣泛使用的異步串行數(shù)據(jù)通信協(xié)議。下面首先介紹 UART 硬件接口及電平轉(zhuǎn)換電路,分析UART的傳輸時(shí)序并利用Verilog HDL語言進(jìn)

2011-07-22 11:24:35 113

113 隨著FPGA的廣泛應(yīng)用,經(jīng)常需要FPGA與其他數(shù)字系統(tǒng)進(jìn)行串行通信,專用的UART集成電路如8250,8251等是比較復(fù)雜的,因?yàn)閷S玫?b class="flag-6" style="color: red">UART集成電路既要考慮異步的收發(fā)功能,又要兼容RS232接口設(shè)計(jì)

2011-09-16 11:57:43 4390

4390

討論了靜態(tài)時(shí)序分析算法及其在IC 設(shè)計(jì)中的應(yīng)用。首先,文章討論了靜態(tài)時(shí)序分析中的偽路徑問題以及路徑敏化算法,分析了影響邏輯門和互連線延時(shí)的因素。最后通過一個(gè)完整的IC 設(shè)計(jì)

2011-12-20 11:03:16 95

95 _靜態(tài)時(shí)序分析(Static_Timing_Analysis)基礎(chǔ)及應(yīng)用[1]。

2016-05-09 10:59:26 31

31 異步串行接口UART的C語言編程,快來下載學(xué)習(xí)啊

2016-07-04 14:01:58 7

7 電子專業(yè)單片機(jī)相關(guān)知識(shí)學(xué)習(xí)教材資料之時(shí)序邏輯電路的分析與設(shè)計(jì)

2016-09-02 14:30:26 0

0 華清遠(yuǎn)見FPGA代碼-RS-232C(UART)接口的設(shè)計(jì)與實(shí)現(xiàn)

2016-10-27 18:07:54 10

10 華為BTS邏輯分析時(shí)序,感興趣的小伙伴們可以瞧一瞧。

2016-11-15 17:23:09 0

0 基于時(shí)序路徑的FPGA時(shí)序分析技術(shù)研究_周珊

2017-01-03 17:41:58 2

2 靜態(tài)時(shí)序分析基礎(chǔ)及應(yīng)用

2017-01-24 16:54:24 7

7 使用的串行數(shù)據(jù)傳輸協(xié)議。UART允許在串行鏈路上進(jìn)行全雙工的通信。 串行外設(shè)用到RS232-C異步串行接口,一般采用專用的集成電路即UART實(shí)現(xiàn)。

2019-10-06 16:59:00 654

654

時(shí)序分析時(shí)FPGA設(shè)計(jì)中永恒的話題,也是FPGA開發(fā)人員設(shè)計(jì)進(jìn)階的必由之路。慢慢來,先介紹時(shí)序分析中的一些基本概念。

2017-02-11 19:08:29 3938

3938

與并行通信之間加以轉(zhuǎn)換。作為把并行輸入信號(hào)轉(zhuǎn)成串行輸出信號(hào)的芯片,UART通常被集成于其他通訊接口的連結(jié)上。

2017-11-08 17:26:55 55646

55646

通用異步收發(fā)傳輸器(UniversalAsynchronousReceiver/Transmitter),通常稱作UART,是一種異步收發(fā)傳輸器。將數(shù)據(jù)由串行通信與并行通信間作傳輸轉(zhuǎn)換,作為并行輸入

2017-11-20 16:19:57 12213

12213

嵌入式里面說的串口,一般是指UART口, 但是我們經(jīng)常搞不清楚它和COM口的區(qū)別, 以及RS232, TTL等關(guān)系, 實(shí)際上UART,COM指的物理接口形式(硬件), 而TTL、RS-232

2017-12-06 10:21:50 25009

25009 時(shí)序分析基本概念介紹——STA概述,動(dòng)態(tài)時(shí)序分析,主要是通過輸入向量作為激勵(lì),來驗(yàn)證整個(gè)設(shè)計(jì)的時(shí)序功能。動(dòng)態(tài)時(shí)序分析的精確與否取決于輸入激勵(lì)的覆蓋率,它最大的缺點(diǎn)就是速度非常慢,通常百萬門的設(shè)計(jì)想全部覆蓋測(cè)試的話,時(shí)間就是按月來計(jì)算了。

2017-12-14 17:01:32 27851

27851

時(shí)序分析基本概念介紹——時(shí)序庫Lib。用于描述物理單元的時(shí)序和功耗信息的重要庫文件。lib庫是最基本的時(shí)序庫,通常文件很大,分為兩個(gè)部分。

2017-12-15 17:11:43 10427

10427

我們常用UART口進(jìn)行調(diào)試,但是UART的數(shù)據(jù)要傳到電腦上分析就要匹配電腦的接口,通常我們電腦使用接口有COM口和USB口(最終在電腦上是一個(gè)虛擬的COM口),但是要想連上這兩種接口都要需要進(jìn)行硬件接口轉(zhuǎn)換和電平轉(zhuǎn)換。

2017-12-28 08:42:37 22930

22930

STA的簡(jiǎn)單定義如下:套用特定的時(shí)序模型(Timing Model),針對(duì)特定電路分析其是否違反設(shè)計(jì)者給定的時(shí)序限制(Timing Constraint)。以分析的方式區(qū)分,可分為Path-Based及Block-Based兩種。

2018-04-03 15:56:16 10

10 UART接口UART接口是通用的異步串行接口,按照標(biāo)準(zhǔn)波特率完成雙向通訊,傳輸速度較慢。采用UART接口,WiFi模塊支持串口透明數(shù)據(jù)傳輸模式,并且具有多模安全能力。內(nèi)置TCP/IP協(xié)議

2018-08-09 19:01:00 6699

6699 關(guān)鍵詞:uart , WiFi模塊 , WU106 , WG219 UART接口 UART接口是通用的異步串行接口,按照標(biāo)準(zhǔn)波特率完成雙向通訊,傳輸速度較慢。采用UART接口, WiFi模塊 支持

2018-08-13 07:38:01 299

299 時(shí)序分析在FPGA設(shè)計(jì)中是分析工程很重要的手段,時(shí)序分析的原理和相關(guān)的公式小編在這里不再介紹,這篇文章是小編在練習(xí)Vivado軟件時(shí)序分析的筆記,小編這里使用的是18.1版本的Vivado。 這次

2019-09-15 16:38:00 5787

5787

FPGA中的時(shí)序問題是一個(gè)比較重要的問題,時(shí)序違例,尤其喜歡在資源利用率較高、時(shí)鐘頻率較高或者是位寬較寬的情況下出現(xiàn)。建立時(shí)間和保持時(shí)間是FPGA時(shí)序約束中兩個(gè)最基本的概念,同樣在芯片電路時(shí)序分析中也存在。

2019-12-23 07:01:00 1894

1894

靜態(tài)時(shí)序分析是一種驗(yàn)證方法,其基本前提是同步邏輯設(shè)計(jì)(異步邏輯設(shè)計(jì)需要制定時(shí)鐘相對(duì)關(guān)系和最大路徑延時(shí)等,這個(gè)后面會(huì)說)。靜態(tài)時(shí)序分析僅關(guān)注時(shí)序間的相對(duì)關(guān)系,而不是評(píng)估邏輯功能(這是仿真和邏輯分析

2019-11-22 07:07:00 3179

3179 時(shí)序分析是以分析時(shí)間序列的發(fā)展過程、方向和趨勢(shì),預(yù)測(cè)將來時(shí)域可能達(dá)到的目標(biāo)的方法。此方法運(yùn)用概率統(tǒng)計(jì)中時(shí)間序列分析原理和技術(shù),利用時(shí)序系統(tǒng)的數(shù)據(jù)相關(guān)性,建立相應(yīng)的數(shù)學(xué)模型,描述系統(tǒng)的時(shí)序狀態(tài),以預(yù)測(cè)未來。

2019-11-15 07:02:00 2570

2570

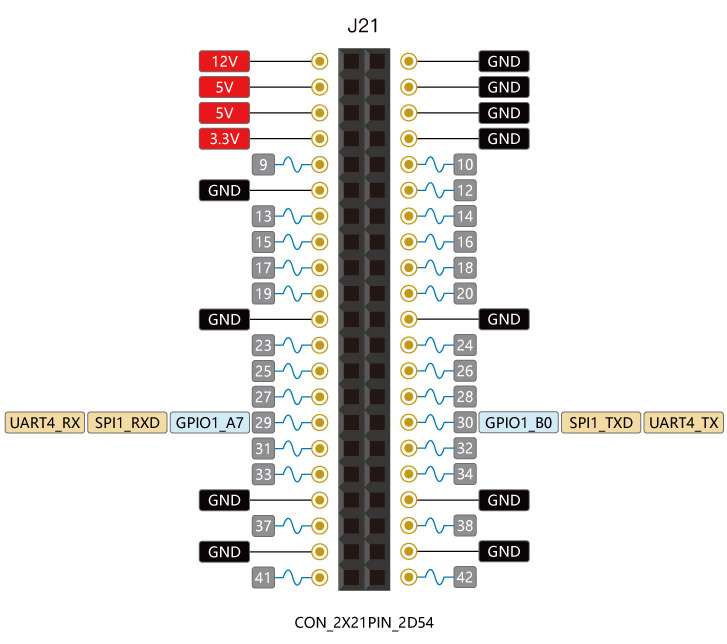

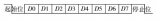

Firefly-RK3399 支持五路UART:UART0, UART1, UART2, UART3, UART4,都擁有兩個(gè)64字節(jié)的FIFO緩沖區(qū),用于數(shù)據(jù)接收和發(fā)送。

2019-11-20 11:01:02 2481

2481

基于FTDI FT232RQ,PmodUSBUART提供了一個(gè)USB與UART接口交叉轉(zhuǎn)換模塊。用戶可在該P(yáng)mod任一方向發(fā)送數(shù)據(jù),并以適當(dāng)?shù)母袷浇邮辙D(zhuǎn)換后的數(shù)據(jù)。

2019-11-27 14:36:12 2004

2004

Air機(jī)器的適配器電壓為14.5V,經(jīng)過一個(gè)電源小板到底主板的電源接口J7000,雖然電源小板集合了很多功能,但是買一個(gè)沒多少錢,我再次就不熬贅了,只會(huì)分析主板的上電時(shí)序。

2019-11-15 08:00:00 86

86 ,分析 UART 的傳輸時(shí)序并利用 Verilog HDL 語言進(jìn)行建模與仿真,最后通過開發(fā)板與 PC 相連進(jìn)行 RS-232 通信來測(cè)試 UART 收發(fā)器的正確性。

2019-12-27 08:00:00 4

4 停止條件即示波器停止“統(tǒng)計(jì)分析”的條件,當(dāng)測(cè)試條件滿足預(yù)設(shè)條件時(shí),時(shí)序分析軟件會(huì)停止統(tǒng)計(jì)完成分析工作。

2020-04-29 15:18:52 2425

2425 UART作為整個(gè)系列首個(gè)和大家探討的數(shù)字接口,主要是由于其功能簡(jiǎn)單且應(yīng)用廣泛。而且大部分SOC芯片均選擇通過UART作為Debug接口。芯片回片時(shí),第一次啟動(dòng)通過串口打印出來的字符,像極了一顆新生命在說Hello world,那種感覺估計(jì)也只有同行才能懂。

2020-09-03 15:53:28 8832

8832

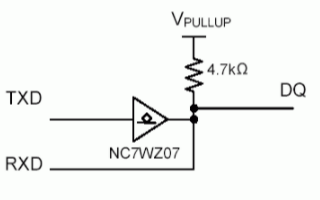

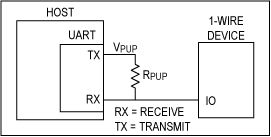

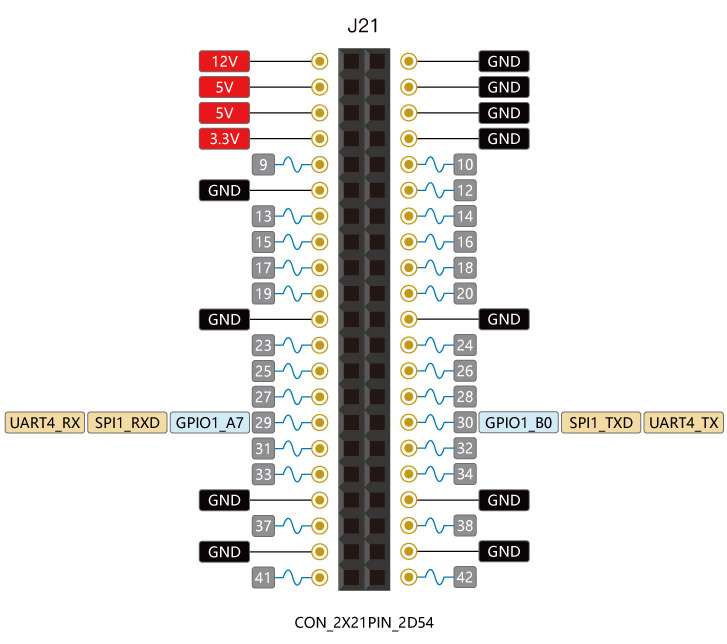

本應(yīng)用筆記說明了如何使用微處理器的UART來實(shí)現(xiàn)1-Wire?總線主機(jī)。它包括所需的電接口,UART配置以及UART與1-Wire信號(hào)之間的時(shí)序關(guān)系的說明。設(shè)置UART字節(jié)時(shí)序提供的靈活性允許直接

2021-05-28 16:24:30 3603

3603

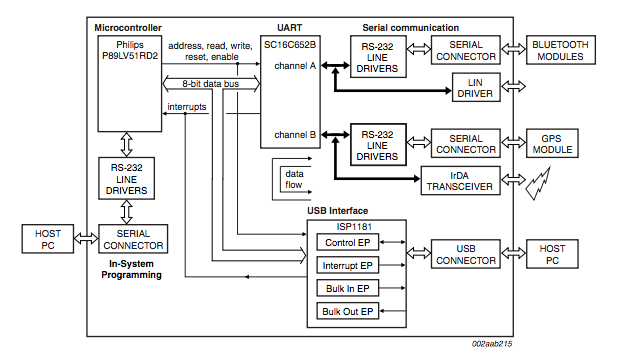

該套件使用戶能夠通過USB快速了解UART串行接口的實(shí)現(xiàn)以及UART至RS-232串行端口的接口。

2021-04-22 15:07:32 5423

5423

靜態(tài)時(shí)序分析是檢查芯片時(shí)序特性的一種方法,可以用來檢查信號(hào)在芯片中的傳播是否符合時(shí)序約束的要求。相比于動(dòng)態(tài)時(shí)序分析,靜態(tài)時(shí)序分析不需要測(cè)試矢量,而是直接對(duì)芯片的時(shí)序進(jìn)行約束,然后通過時(shí)序分析工具給出

2020-11-11 08:00:00 58

58 本文檔的主要內(nèi)容詳細(xì)介紹的是華為FPGA硬件的靜態(tài)時(shí)序分析與邏輯設(shè)計(jì)包括了:靜態(tài)時(shí)序分析一概念與流程,靜態(tài)時(shí)序分析一時(shí)序路徑,靜態(tài)時(shí)序分析一分析工具

2020-12-21 17:10:54 18

18 時(shí)序分析時(shí)FPGA設(shè)計(jì)中永恒的話題,也是FPGA開發(fā)人員設(shè)計(jì)進(jìn)階的必由之路。慢慢來,先介紹時(shí)序分析中的一些基本概念。

2021-01-08 16:57:55 28

28 本文檔的主要內(nèi)容詳細(xì)介紹的是時(shí)序分析的靜態(tài)分析基礎(chǔ)教程。

2021-01-14 16:04:00 14

14 本文檔的主要內(nèi)容詳細(xì)介紹的是時(shí)序分析的Timequest教程免費(fèi)下載。

2021-01-14 16:04:00 3

3 本文檔的主要內(nèi)容詳細(xì)介紹的是時(shí)序分析的Timequest教程免費(fèi)下載。

2021-01-14 16:04:00 15

15 串行UART接口產(chǎn)品亮點(diǎn)

2021-04-22 19:46:13 5

5 UC-006:一種4線UART轉(zhuǎn)PC接口

2021-05-08 08:10:45 0

0 方法,能夠有效減少時(shí)序路徑問題分析所需工作量。 時(shí)序路徑問題分析定義為通過調(diào)查一條或多條具有負(fù)裕量的時(shí)序路徑來判斷達(dá)成時(shí)序收斂的方法。當(dāng)設(shè)計(jì)無法達(dá)成時(shí)序收斂時(shí),作為分析步驟的第一步,不應(yīng)對(duì)個(gè)別時(shí)序路徑進(jìn)行詳細(xì)時(shí)序分

2021-05-19 11:25:47 2677

2677

時(shí)序分析時(shí)FPGA設(shè)計(jì)中永恒的話題,也是FPGA開發(fā)人員設(shè)計(jì)進(jìn)階的必由之路。慢慢來,先介紹時(shí)序分析中的一些基本概念。

2022-03-18 11:07:13 2095

2095 EU204 是具有 1 個(gè)從機(jī) I2C 接口和 4 個(gè) UART

接口的數(shù)據(jù)轉(zhuǎn)發(fā)芯片,可通過 I2C 接口協(xié)議擴(kuò)

展為 4 個(gè)標(biāo)準(zhǔn)的 UART 接口, UART 通訊速率最高

2022-06-17 14:42:50 11

11 EU204 是具有 1 個(gè)從機(jī) I2C 接口和 4 個(gè) UART接口的數(shù)據(jù)轉(zhuǎn)發(fā)芯片,可通過 I2C 接口協(xié)議擴(kuò)展為 4 個(gè)標(biāo)準(zhǔn)的 UART 接口, UART 通訊速率最高

460800bps,各接口

2022-06-20 18:01:10 19

19 要從時(shí)序分析刪除一組路徑,如果您確定這些路徑不會(huì)影響時(shí)序性能(False 路徑),可用FROM-TO 約束以及時(shí)序忽略 (TIG) 關(guān)鍵字。

2022-08-02 08:57:26 517

517 電子發(fā)燒友網(wǎng)站提供《時(shí)序分析工具對(duì)比報(bào)告.pdf》資料免費(fèi)下載

2022-09-27 11:08:11 0

0 既可以用于系統(tǒng)級(jí)的設(shè)計(jì),用于時(shí)序分析和文檔編制,也用于ASIC/FPGA設(shè)計(jì)中,用于接口規(guī)范,以及創(chuàng)建SDC時(shí)序約束。

2022-11-21 11:36:15 2174

2174 電子發(fā)燒友網(wǎng)站提供《用于Basys3板的VHDL中的UART接口.zip》資料免費(fèi)下載

2022-11-22 09:50:57 2

2 本文介紹了在低功耗系統(tǒng)中降低功耗同時(shí)保持測(cè)量和監(jiān)控應(yīng)用所需的精度的時(shí)序因素和解決方案。它解釋了當(dāng)所選ADC是逐次逼近寄存器(SAR)ADC時(shí)影響時(shí)序的因素。對(duì)于Σ-Δ(∑-Δ)架構(gòu),時(shí)序考慮因素有所不同(請(qǐng)參閱本系列文章的第1部分)。本文探討了模擬前端時(shí)序、ADC時(shí)序和數(shù)字接口時(shí)序中的信號(hào)鏈考慮因素。

2022-12-13 11:20:18 1057

1057

本應(yīng)用筆記解釋了如何使用微處理器的UART實(shí)現(xiàn)1-Wire總線主機(jī)。它包括對(duì)所需電氣接口、UART配置以及UART和1-Wire信號(hào)之間的時(shí)序關(guān)系的說明。此外,它還參考了UART 1-Wire

2023-03-29 11:28:17 2178

2178

引言 在同步電路設(shè)計(jì)中,時(shí)序是一個(gè)非常重要的因素,它決定了電路能否以預(yù)期的時(shí)鐘速率運(yùn)行。為了驗(yàn)證電路的時(shí)序性能,我們需要進(jìn)行 靜態(tài)時(shí)序分析 ,即 在最壞情況下檢查所有可能的時(shí)序違規(guī)路徑,而不需要測(cè)試

2023-06-28 09:38:57 714

714

今天要介紹的時(shí)序分析基本概念是lookup table。中文全稱時(shí)序查找表。

2023-07-03 14:30:34 666

666

今天我們介紹的時(shí)序分析概念是 **SOCV** 。也被叫作POCV,全稱為 **Statistic OCV** . 這是一種比AOCV更加先進(jìn)的分析模式。

2023-07-03 15:19:00 1347

1347

??本文主要介紹了靜態(tài)時(shí)序分析 STA。

2023-07-04 14:40:06 528

528

今天我們要介紹的時(shí)序分析基本概念是MMMC分析(MCMM)。全稱是multi-mode, multi-corner, 多模式多端角分析模式。這是在先進(jìn)工藝下必須要使用的一種時(shí)序分析模式。

2023-07-04 15:40:13 1461

1461

電子發(fā)燒友網(wǎng)站提供《嵌入式系統(tǒng)外圍接口的時(shí)序分析與電路設(shè)計(jì).pdf》資料免費(fèi)下載

2023-10-09 16:50:13 1

1

電子發(fā)燒友App

電子發(fā)燒友App

評(píng)論