IIC總線概述

IIC開發于1982年,當時是為了給電視機內的CPU和外圍芯片提供更簡易的互連方式。電視機是最早的嵌入式系統之一,而最初的嵌入系統是使用內存映射(memory-mappedI/O)的方式來互連微控制器和外圍設備的。要實現內存映射,設備必須并行連入微控制器的數據線和地址線,這種方式在連接多個外設時需大量線路和額外地址解碼芯片,很不方便并且成本高。

為了節省微控制器的引腳和和額外的邏輯芯片,使印刷電路板更簡單,成本更低,位于荷蘭的Philips實驗室開發了IIC(Inter-IntegratedCircuit),它是由數據線SDA和時鐘線SCL兩根線構成的串行總線,可發送和接收數據。在CPU與被控IC之間、IC與IC之間進行雙向傳送

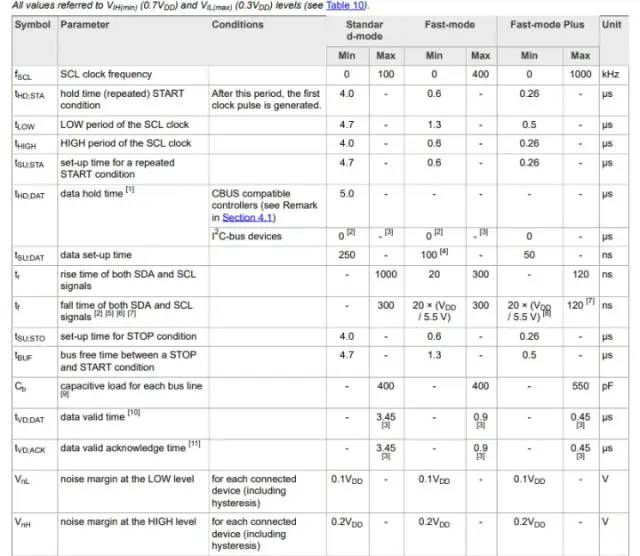

IIC數據傳輸速率有標準模式(100kbps)、快速模式(400kbps)和高速模式(3.4Mbps),另外一些變種實現了低速模式(10kbps)和快速+模式(1Mbps)

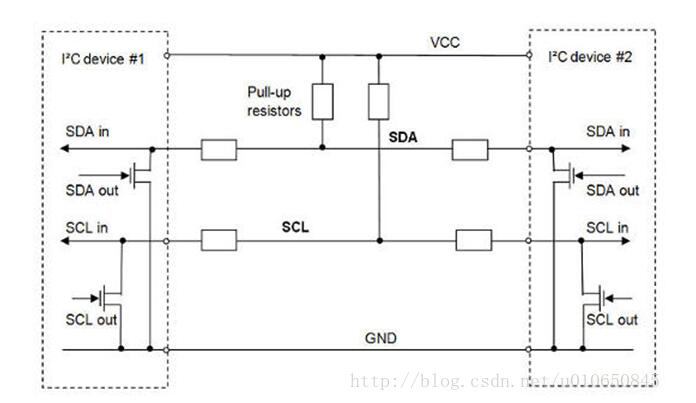

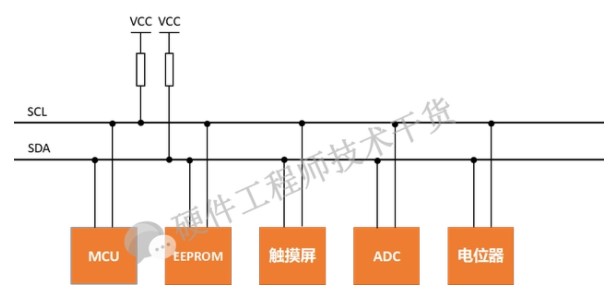

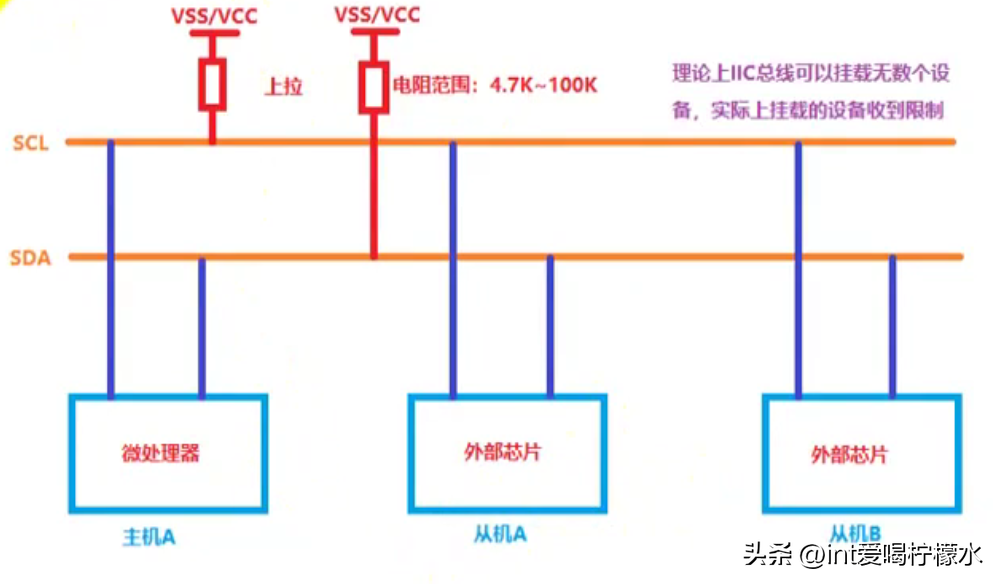

IIC總線硬件結構

IIC即I2C,是一種總線結構。

每一個I2C總線器件內部的SDA、SCL引腳電路結構都是一樣的,引腳的輸出驅動與輸入緩沖連在一起。其中輸出為漏極開路的場效應管、輸入緩沖為一只高輸入阻抗的同相器。這種電路具有兩個特點:

由于SDA、SCL為漏極開路結構,借助于外部的上拉電阻實現了信號的“線與”邏輯;

引腳在輸出信號的同時還能對引腳上的電平進行檢測,檢測是否與剛才輸出一致。為“時鐘同步”和“總線仲裁”提供硬件基礎。

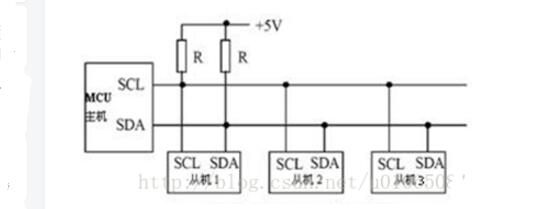

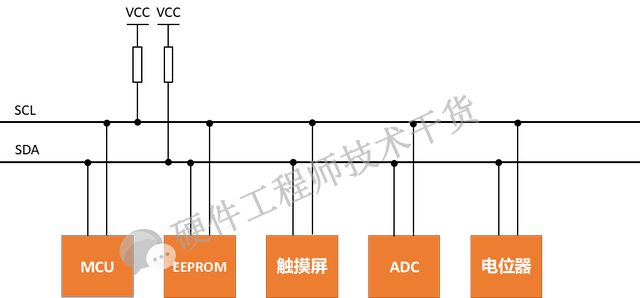

IIC總線典型應用

IIC設備典型應用:

物理結構上,IIC系統由一條串行數據線SDA和一條串行時鐘線SCL組成。主機按一定的通信協議向從機尋址和進行信息傳輸。在數據傳輸時,由主機初始化一次數據傳輸,主機使數據在SDA線上傳輸的同時還通過SCL線傳輸時鐘。信息傳輸的對象和方向以及信息傳輸的開始和終止均由主機決定。

每個器件都有一個唯一的地址,而且可以是單接收的器件(例如:LCD驅動器)或者可以接收也可以發送的器件(例如:存儲器)。發送器或接收器可以在主模式或從模式下操作,這取決于芯片是否必須啟動數據的傳輸還是僅僅被尋址。

IIC總線的FPGA實現原理及過程

一、實驗平臺

軟件平臺:ModelSim-Altera 6.4a (Quartus II 9.0)

硬件平臺:DIY_DE2

二、實驗原理

1、IIC總線器件工作原理

在IIC總線上傳送信息時的時鐘同步信號是由掛接在SCL時鐘線上的所有器件的邏輯“與”完成的。SCL線上由高電平到低電平的跳變將影響到這些器件,一旦某個器件的時鐘信號變為低電平,將使SCL線上所有器件開始并保護低電平期。此時,低電平周期短的器件的時鐘由低至高的跳變并不影響SCL線的狀態,這些器件將進入高電平等待的狀態。

當所有器件的時鐘信號都變為高電平時,低電平期結束,SCL線被釋放返回高電平,即所有的器件都同時開始它們的高電平期。其后,第一個結束高電平期的器件又將SCL線拉成低電平。這樣就在SCL線上產生一個同步時鐘。可見,時鐘低電平時間由時鐘低電平期最長的器件決定,而時鐘高電平時間由時鐘高電平期最短的器件決定。

IIC總線上數據的傳輸速率在標準模式下可達100kbit/s 在快速模式下可達400kbit/s 在高速模式下可達3.4Mbit/s ,連接到總線的接口數量只由總線電容是400pF 的限制決定。

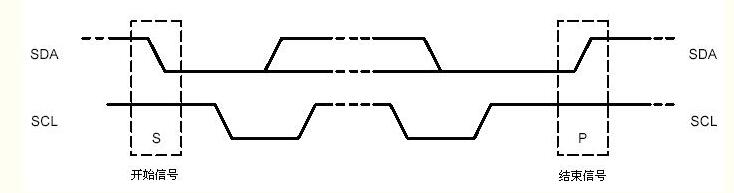

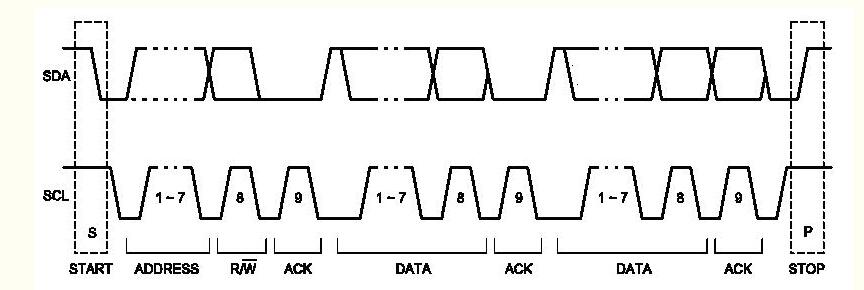

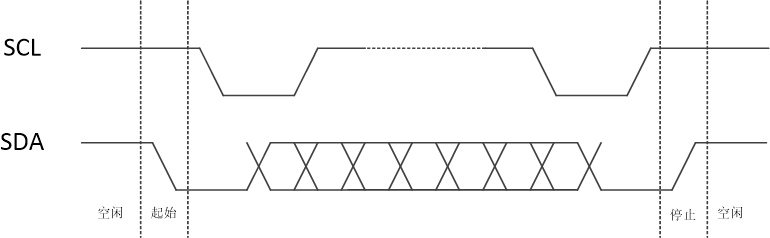

2、IIC總線的傳輸協議與數據傳送時序

(1)起始和停止條件

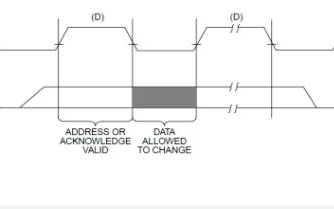

在數據傳送過程中,必須確認數據傳送的開始和結束。在IIC總線技術規范中,開始和結束信號(也稱啟動和停止信號)的定義如圖1所示。

圖1起始和停止信號圖

開始信號:當時鐘總線SCL為高電平時,數據線SDA由高電平向低電平跳變,開始傳送數據。

結束信號:當SCL線為高電平時,SDA線從低電平向高電平跳變,結束傳送數據。

開始和結束信號都是由主器件產生。在開始信號以后,總線即被認為處于忙狀態,其它器件不能再產生開始信號。主器件在結束信號以后退出主器件角色,經過一段時間過,總線被認為是空閑的。

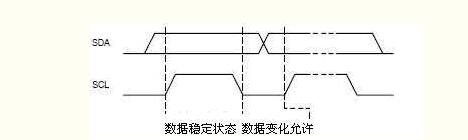

(2)數據格式

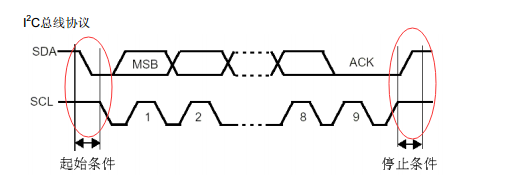

IIC總線數據傳送采用時鐘脈沖逐位串行傳送方式,在SCL的低電平期間,SDA線上高、低電平能變化,在高電平期間,SDA上數據必須保護穩定,以便接收器采樣接收,時序如圖2所示。

圖2 數據傳送時序圖

IIC總線發送器送到SDA線上的每個字節必須為8位長,傳送時高位在前,低位在后。與之對應,主器件在SCL線上產生8個脈沖;第9個脈沖低電平期間,發送器釋放SDA線,接收器把SDA線拉低,以給出一個接收確認位;第9個脈沖高電平期間,發送器收到這個確認位然后開始下一字節的傳送,下一個字節的第一個脈沖低電平期間接收器釋放SDA。每個字節需要9個脈沖,每次傳送的字節數是不受限制的。

IIC總線的數據傳送格式是在IIC總線開始信號后,送出的第一字節數據是用來選擇從器件地址的,其中前7位為地址碼,第8位為方向位(R/W)。方向位為“0”表示發送,即主器件把信息寫到所選擇的從器件中;方向位為“1”表示主器件將從從器件讀信息。格式如下:

開始信號后,系統中的各個器件將自己的地址和主器件送到總線上的地址進行比較,如果與主器件發送到總線上的地址一致,則該器件即被主器件尋址的器件,其接收信息還是發送信息則由第8位(R/W)決定。發送完第一個字節后再開始發數據信號。

(3)響應

數據傳輸必須帶響應。相關的響應時鐘脈沖由主機產生,當主器件發送完一字節的數據后,接著發出對應于SCL線上的一個時鐘(ACK)認可位,此時鐘內主器件釋放SDA線,一字節傳送結束,而從器件的響應信號將SDA線拉成低電平,使SDA在該時鐘的高電平期間為穩定的低電平。從器件的響應信號結束后,SDA線返回高電平,進入下一個傳送周期。

通常被尋址的接收器在接收到的每個字節后必須產生一個響應。當從機不能響應從機地址時,從機必須使數據線保持高電平,主機然后產生一個停止條件終止傳輸或者產生重復起始條件開始新的傳輸。如果從機接收器響應了從機地址但是在傳輸了一段時間后不能接收更多數據字節,主機必須再一次終止傳輸。這個情況用從機在第一個字節后沒有產生響應來表示。從機使數據線保持高電平主機產生一個停止或重復起始條件。完整的數據傳送過程如圖3所示。

圖3 完整的數據傳送過程

另外,IIC總線還具有廣播呼叫地址用于尋址總線上所有器件的功能。若一個器件不需要廣播呼叫尋址中所提供的任何數據,則可以忽咯該地址不作響應。如果該器件需要廣播呼叫尋址中按需提供的數據,則應對地址作出響應,其表現為一個接收器。

三、實驗過程

根據上述的實驗原理,對DE2_TV中的IIC部分進行modelsim仿真。

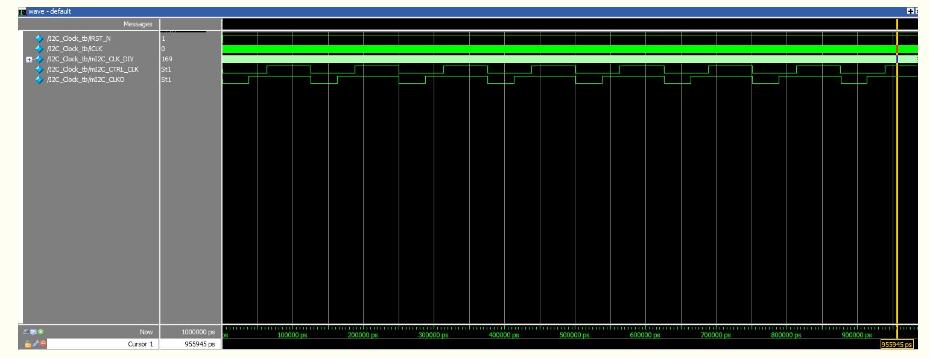

1、IIC所需時鐘的仿真

FPGA作為IIC器件的主機,要產生IIC的工作時鐘,下面先對IIC所需的時鐘信號進行仿真。

待仿真的時鐘信號程序如下:

module I2C_Clock

(

iCLK,

iRST_N,

mI2C_CTRL_CLK,

mI2C_CLK_DIV,

mI2C_CLKO

);

input iCLK;

input iRST_N;

output mI2C_CTRL_CLK;

output mI2C_CLK_DIV;

output mI2C_CLKO;

reg mI2C_CTRL_CLK;

reg [15:0] mI2C_CLK_DIV;

reg mI2C_CLKO;

// Clock Setting

parameter CLK_Freq = 50000000; //??? 50 MHz

parameter I2C_Freq = 80000; //??? 40 KHz 25Us

parameter I2C_Thd = 200000; //??? 5Us 200 KHz

always@(posedge iCLK or negedge iRST_N)

begin

// 5000 times divide frequence of iCLK

if (!iRST_N)

begin

mI2C_CLK_DIV 《= 0;

mI2C_CLKO 《= 0;

mI2C_CTRL_CLK 《= 0;

end

else if( mI2C_CLK_DIV 《 (CLK_Freq/I2C_Freq))

begin

mI2C_CLK_DIV 《= mI2C_CLK_DIV+1;

if ((!mI2C_CTRL_CLK)&(mI2C_CLK_DIV 《 ((CLK_Freq/I2C_Freq)- (CLK_Freq/I2C_Thd))) )

mI2C_CLKO 《= 0;

else

mI2C_CLKO 《= 1;

end

else

begin

mI2C_CLK_DIV 《= 0;

mI2C_CTRL_CLK 《= ~mI2C_CTRL_CLK;

end

end

endmodule

testbench程序如下:

module I2C_Clock_tb ;

//parameter I2C_Thd = 200000 ;

//parameter I2C_Freq = 80000 ;

//parameter CLK_Freq = 50000000 ;

wire mI2C_CTRL_CLK ;

wire [15:0] mI2C_CLK_DIV ;

wire mI2C_CLKO ;

reg iRST_N ;

reg iCLK ;

I2C_Clock //#( I2C_Thd , I2C_Freq , CLK_Freq )

DUT (

.mI2C_CTRL_CLK (mI2C_CTRL_CLK ) ,

.mI2C_CLK_DIV (mI2C_CLK_DIV ) ,

.mI2C_CLKO (mI2C_CLKO ) ,

.iRST_N (iRST_N ) ,

.iCLK (iCLK ) );

initial

begin

iRST_N = 0;

iCLK = 0;

#50

iRST_N = 1;

end

always

begin

#50 iCLK = ~iCLK;

end

endmodule

modelsim仿真的波形如下:

圖4 IIC內部時鐘仿真圖

經過計算,IIC內部所用的時鐘頻率為40KHz。

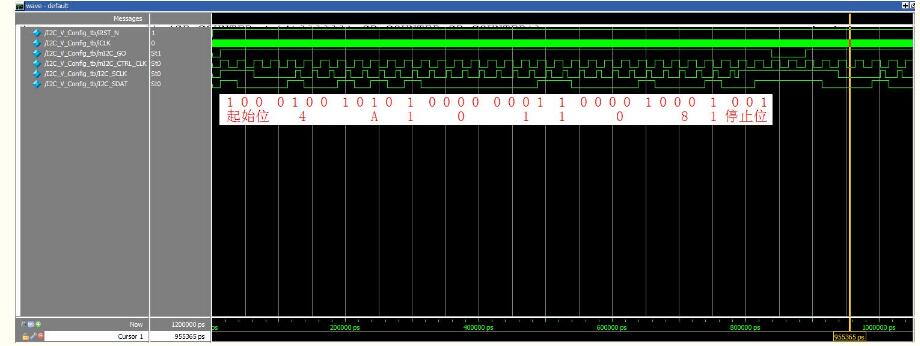

2、IIC整體仿真

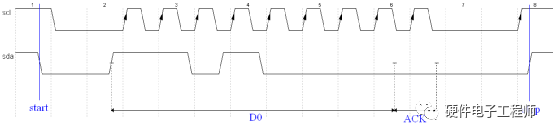

相關程序在附件中。下面是仿真波形。

圖5 IIC整體仿真波形圖

結合上述仿真波形圖和程序可以看出:

起始位:SCLK為高電平時,SDAT由高到低,指示IIC總線傳輸數據的開始;

之后,傳送一個字節的數據,即4A,為從機的地址,隨后,跟了一個高電平,為應答位;

之后,傳送一個字節的數據,即01,為從機地址的子地址,隨后,跟了一個高電平,為應答位;

之后,傳送一個字節的數據,即08,為上面子地址寄存器配置的數據,隨后,跟了一個高電平,為應答位;

最后,為停止位,SCLK為高電平時,SDAT由低到高,指示該次IIC總線傳輸數據的結束。

由仿真結果可知,當傳送完一個字節后,SDAT為一個脈沖的高電平,而不是從器件先將SDAT拉低再拉高,這樣也是可以的。

電子發燒友App

電子發燒友App

評論