隨著航天技術的發展,FPGA 等大規模邏輯器件越來越成為不可缺的角色; 同時處理數據量的增大、以及各類型接口電路的交叉使用,使得合理、可靠的高速接口設計成為衡量設計優劣的關鍵。而由于空間環境的特殊性,導致近年來在軌衛星產品中單粒子翻轉( SEU) 頻發,使得設計人員必須考慮將以SRAM 為基礎的FPGA 設計移植到更為可靠的ASIC或反熔絲FPGA.

DDR( Double DataRate) 是雙倍速率讀寫技術的意思。傳統的數據處理方式在1 個時鐘周期內只傳輸1 次數據,是在時鐘的上升期進行數據傳輸; 而DDR 內存則是1 個時鐘周期內傳輸2 次數據,能夠在時鐘的上升期和下降期各傳輸1 次數據,因此稱為雙倍速率讀寫技術。采用DDR 技術可以在相同的總線頻率下達到更高的數據傳輸率。

文章根據實際的背景應用提出一種基于Actel公司RTAX-S 系列耐輻射反熔絲FPGA 芯片RTAX250S 的高速DDR 接口設計方法,并通過Actel公司IDE V9. 0 編譯軟件和Modelsim 6. 5d 仿真軟件進行了仿真驗證。該方法已用在某星載GMSK 調制器上,獲得了良好的效果。

1 DDR 高速接口設計

1. 1 RTAX – S 系列反熔絲FPGA 的特點

對于衛星應用,設計人員在選擇可選的技術時一向十分為難。在可編程器件領域,其中就包括了專用集成電路( ASIC) 、以SRAM 為基礎的現場可編程門陣列FPGA 和以反熔絲為基礎的FPGA.由于沒有一種技術是萬能的,衛星設計人員與所有設計人員一樣面對同樣的挑戰,需要針對特定的應用權衡取舍各種特性以找出最佳方案。

以往的設計中,以SRAM 為基礎的FPGA ( 以Xilinx 產品為代表) 有著更多的應用,其優勢在于擁有高邏輯密度和高靈活性,而作為航天應用,其致命的缺點是所有SRAM 都易受高強度宇宙輻射所影響,來自宇宙射線中的重離子很容易在SRAM 單元中或附近沉積足夠的電荷導致單一數據位出錯即單粒子翻轉( SEU) ,而且由于SRAM 型FPGA 在SRAM開關中存儲其邏輯配置,因此很容易出現配置擾亂導致電路的布局和功能受到破壞,這些錯誤非常難以檢測和糾正,并且幾乎不可能預防,因為配置開關在SRAM FPGA 的整個SRAM 數據位中超過90% ,輻射誘發的配置擾亂可導致系統失效。

對于衛星設備,ASIC 是具有最高密度最小重量和最低功耗的解決方案,然而卻缺乏FPGA 所提供的靈活性。而且當把設計工具成本、校驗時間和非經常性工程費用( NRE) 一并考慮之后,ASIC 也是成本較高的解決方案。

與可重新配置的SRAM 型FPGA 不同,基于反熔絲解決方案的FPGA 采用一次性編程( OTP) .其優點為固有的非揮發性以及在每次啟動時無須進行強制性的器件配置。與ASIC 一樣,反熔絲FPGA 的上電即行功能使其成為真正的單芯片解決方案。在各種學術會議上已發表了許多輻射測試數據,如IEEE 的核空間輻射影響會議( NSREC) 、NASA 的軍事和航天可編程邏輯器件國際會議( MAPLD) ,事實上,多年的測試證明,耐輻射的反熔絲FPGA 具有SEU 免疫力,其性能也不會因TID( 總電離劑量) 隨時間積累而發生劣化。眾所周知,邏輯觸發器中的數據易被宇宙輻射線所破壞,與SRAM 方案采用軟TMR( 三模冗余) 方法不同,Actel 開發的耐輻射反熔絲FPGA RTAX-S 系列通過架構的提升解決了這個問題,其中每個觸發器實際上是由3 個觸發器和1個表決電路組成,此舉可讓設計人員獲得優于63MeV-cm2 /mg 的LETth,可以滿足大多衛星項目的TID 要求。

1. 2 典型高速接口電路應用目標

文章中高速接口方案的應用目標為GMSK 調制器中基帶數據的數字高斯濾波。

GMSK 調制是一種典型的恒包絡數字調制技術,實現方法的流程圖如圖1 所示,一路待調制的基帶數據從A 處進入FPGA,FPGA 內部通過查表的方式得到量化后的波形數據,并分別從B 處和C 處將其送給2 片DAC,得到需要的I、Q 路波形,從而完成基帶數據的數字高斯濾波。

硬件電路的關鍵是高速DAC 器件的選擇。方案中需要DAC 實現4 倍采樣,即圖1 中A 處每輸入1 個碼元,B 處和C 處都要分別產生4 個點的量化信息給DAC.以115Mbps 碼速率為例,DAC 的采樣時鐘應當為115MHz × 4 = 460MHz,如果使用傳統的單路DAC,則FPGA 主時鐘工作在460MHz,目前宇航級FPGA 無法滿足這一速率。方案中選擇了TI 公司最新的高速DAC 產品DAC5670,它在最高采樣頻率達到2.4GHz 的同時,內部集成了并串轉換模塊,這使得FPGA 的處理速率至少可以降低一半,即230MHz.

應用目標實現流程圖DAC5670

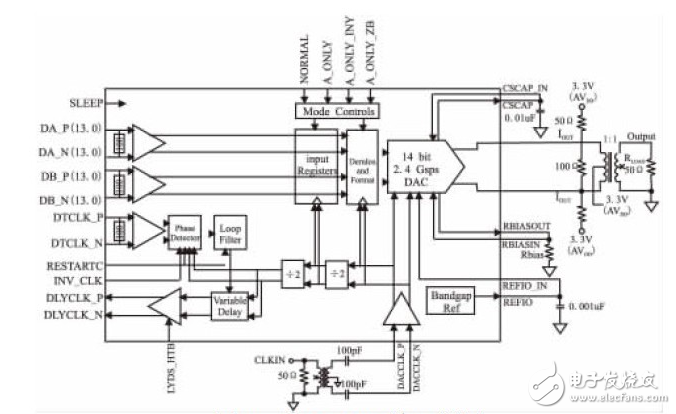

DAC5670 器件手冊推薦的接口框圖如下圖所示

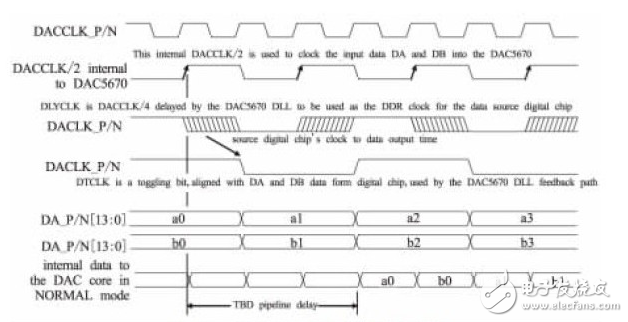

器件工作原理如下: 頻率源輸出400MHz 采樣時鐘,通過變壓器進行單端轉差分輸入DAC 采樣鐘輸入口( DACCLK) ,DAC 內部進行2 級2 分頻并延遲后得到LVDS 電平115MHz 時鐘( DLYCLK) 輸出給FPGA 做數字處理,FPGA 處理完成后輸出LVDS的100MHz1 路時鐘( DTCLK) 和2 路14bit 的量化數據( DA( 13: 0) 和DB( 13: 0) ) .時鐘與數據的關系必須滿足圖3 所示的時序。DAC 內部的鎖相電路將DTCLK 與器件內部的100MHz 進行鑒相,如果存在相差則調整DLYCLK 的延遲量,直到同步,從而保證采樣鐘DACCLK 能夠對DA( 13: 0) 和DB( 13: 0) 進行正確采樣。

1. 3 高速接口方案設計

本應用目標對FPGA 和DAC 之間的高速接口提出如下要求:

( a) DAC 輸出1 路115MHz 時鐘給FPGA;( b ) FPGA 輸出1 路115MHz 時鐘和2 路230Mbps 數據給每片DAC.

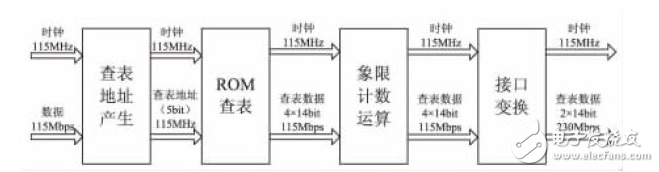

針對這一需求,考慮到FPGA 資源余量較大,為了降低系統運行速率,程序設計中遵循了用面積換取速度的原則,先采用115MHz 時鐘進行并行處理,產生4 路115Mbps 的14bit 量化數據,在輸出接口處將其轉換為2 路230Mbps 的14bit 量化數據,這樣可以使系統時鐘的速率降低一半。處理流程如圖4 所示。

處理流程圖

輸出端接口變換部分是我們討論的重點,它對數據進行4 路到2 路的轉換,量化數據從115Mbps提高到230Mbps,有2 種方式可以實現:

方式一: 對輸入115MHz 時鐘進行2 倍頻得到230MHz 時鐘,使用異步FIFO 對數據進行4 路寫入,2 路讀出,寫鐘為115MHz,讀鐘為230MHz.

方式二: 將4 路14bit 的量化數據分為2 組,每一組均使用115MHz 時鐘進行DDR 輸出接口處理,從而使每一組的輸出均達到230MHz.

下面對2 種方式的可行性進行分析。

對于方式一,實現的關鍵在于2 倍頻時鐘的產生。按照手冊描述,Actel 公司AX 系列芯片作為反熔絲FPGA 中處理能力最強的器件,內部處理時鐘最高可以達到350MHz,且芯片內部集成了PLL( 延遲鎖相環) 資源,可以實現對數字時鐘信號的倍頻和分頻。而選擇RTAX-S 系列在AX 的基礎上進行了耐輻射能力加強,同時去掉了PLL 資源,原因是Actel公司通過實驗證明PLL 資源在空間環境中使用是不可靠的,這意味著倍頻無法在FPGA 內部實現。

因此,如果采用方式一,需要在FPGA 外部增加一個2 倍頻的器件,還要增加相應的電平匹配的電路,這一切對于230MHz 的數字時鐘信號實現上難度較大。

對于方式二,實現的關鍵在于DDR 輸出。通過查閱器件手冊可知,Actel 公司的RTAX – S 系列與Xilinx 公司SRAM 型FPGA 不同,其內部并沒有現成的DDR 輸出模塊可以調用,但是其內部有一種叫做Multiplexor 的多路選擇器資源,可以實現多路輸入到多路輸出的選擇控制,如圖5 所示。

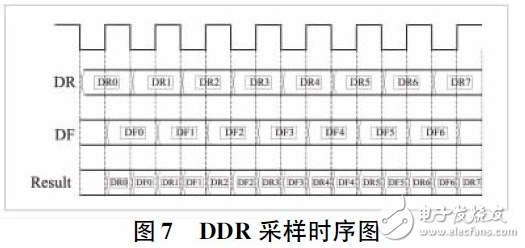

如果將其輸入Data 設置為2 路,輸出Result 設置為1 路,而時鐘作為控制信號SEL,則應當可以實現DDR 的效果。具體實現框圖如圖6 所示。

圖6 框圖實現的時序如圖7 所示,從圖7 可以看出兩路數據在DDR 變換后交替輸出,速率提高一倍,其中DR( 數據1) 先輸出,DF( 數據2) 后輸出。

2 仿真及優化

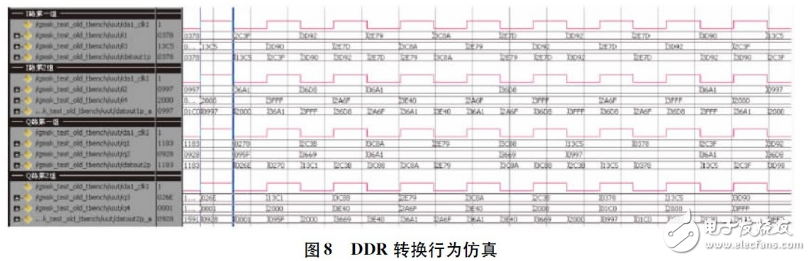

在Actel 公司的編程環境IDE V9. 0 中進行編程仿真。使用Modelsim 6. 5d 進行行為仿真,仿真波形如圖8 所示。由圖8 可見變換后數據符合預期,功能實現正確。

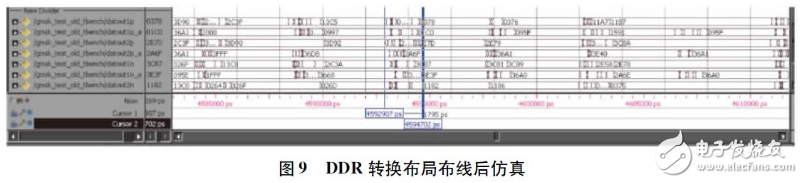

使用Modelsim 6. 5d 進行布局布線后仿真,仿真波形如圖9 所示。由圖9 可見各路數據均存在毛刺,毛刺的最大寬度達到了1. 8ns,這超出了DAC 器件對于輸入并行數據相位差小于1ns 的要求。可能導致DAC 采樣錯誤。

分析最終輸出數據毛刺產生的原因,應當是每路數據的14bit 單獨信號之間路徑的延時不同導致的。而數據在輸出之前大部分環節都是由全局時鐘進行同步處理,可以保證嚴格的同步,除了選擇器Multiplexor 輸出到IO 端口部分走線,因為在Multiplexor的輸出環節不會再有時鐘采樣,因此該部分多路信號延遲差異無法消除。檢查布局布線后底層的布局圖,如圖10 所示,深黑色的單元即為Multiplexor,顯然各個Multiplexor 與對應IO 口的距離差別較大,驗證了之前的分析。

根據前段分析,對Multiplexor 的位置進行手動優化,即在底層布局圖中將所有Multiplexor 均調整到盡量接近IO 端口的位置,保證多路信號在Multiplexor后端延遲盡量一致,優化后鎖定這些Multiplexor的位置,如圖11 所示。

優化Multiplexor 布局后重新進行后仿真,仿真結果如圖12 所示。由圖12 可見,最大毛刺寬度僅為500ps 左右,完全滿足DAC 要求的1ns.可見,優化后的方案合理、可行的實現了要求的功能。

文章中闡述的方法不僅僅局限于FPGA 與DAC之間的接口設計,也適用于FPGA 與其他高速芯片的通信,例如FPGA、DSP、SDRAM 等等支持DDR 接口的器件,同時,對于板級及單元級的通信,使用該方法可以有效降低線纜傳輸信號速率,使得系統各個環節的設計更為簡單。

?結束語

文章分析了Actel 公司反熔絲FPGA 相對于常用的SRAM 型FPGA 在衛星產品中應用的優點,并就一種常見的應用目標,提出基于Actel 公司RTAX-S 系列抗輻射反熔絲FPGA 的高速DDR 輸出接口的設計方法,并通過優化得到符合要求的結果,為反熔絲FPGA 在衛星產品中的高速設計、應用提供了技術保障。

電子發燒友App

電子發燒友App

評論