0 引言

近幾十年來,集成電路事業(yè)發(fā)展迅速,設(shè)計(jì)與工藝技術(shù)不斷發(fā)展,更多和更復(fù)雜的功能被集成到一塊芯片上。SoC的集成度和復(fù)雜度大大提高,在IC設(shè)計(jì)中就容易引入錯(cuò)誤,所以驗(yàn)證工作將變得艱巨。隨著IC設(shè)計(jì)規(guī)模的增大以及設(shè)計(jì)周期的壓縮,傳統(tǒng)驗(yàn)證技術(shù)已經(jīng)不能再滿足日益增長(zhǎng)的驗(yàn)證需求,驗(yàn)證方法學(xué)應(yīng)運(yùn)而生,目前,UVM驗(yàn)證方法學(xué)已經(jīng)成為應(yīng)用最廣泛的方法學(xué)。

本文目的在于為數(shù)字基帶處理單元中標(biāo)簽發(fā)送鏈路的編碼模塊搭建一個(gè)適當(dāng)?shù)摹⑼晟频尿?yàn)證平臺(tái),用來驗(yàn)證RTL代碼的正確與否。運(yùn)用面向?qū)ο笏枷氲腢VM驗(yàn)證方法學(xué)和C語言進(jìn)行平臺(tái)的設(shè)計(jì)與實(shí)現(xiàn),它能有效地縮短驗(yàn)證周期,提高驗(yàn)證效率,加大芯片的面試可能性。

1 UVM驗(yàn)證方法學(xué)

目前,主流的驗(yàn)證方法學(xué)有VMM、OVM和UVM。UVM基于System Verilog語言,具有VMM、OVM等諸多驗(yàn)證方法學(xué)的優(yōu)點(diǎn),是一套高效、開源的驗(yàn)證方法學(xué)。UVM由Accellera標(biāo)準(zhǔn)組織推出,并得到了三大主流EDA供應(yīng)商支持。

通用驗(yàn)證方法學(xué)(Universal Verification Methodology,UVM)是一個(gè)以SystemVerilog類庫為主體的驗(yàn)證平臺(tái)開發(fā)框架,可以利用其可重用組件構(gòu)建具有標(biāo)準(zhǔn)化層次結(jié)構(gòu)和接口的功能驗(yàn)證環(huán)境。

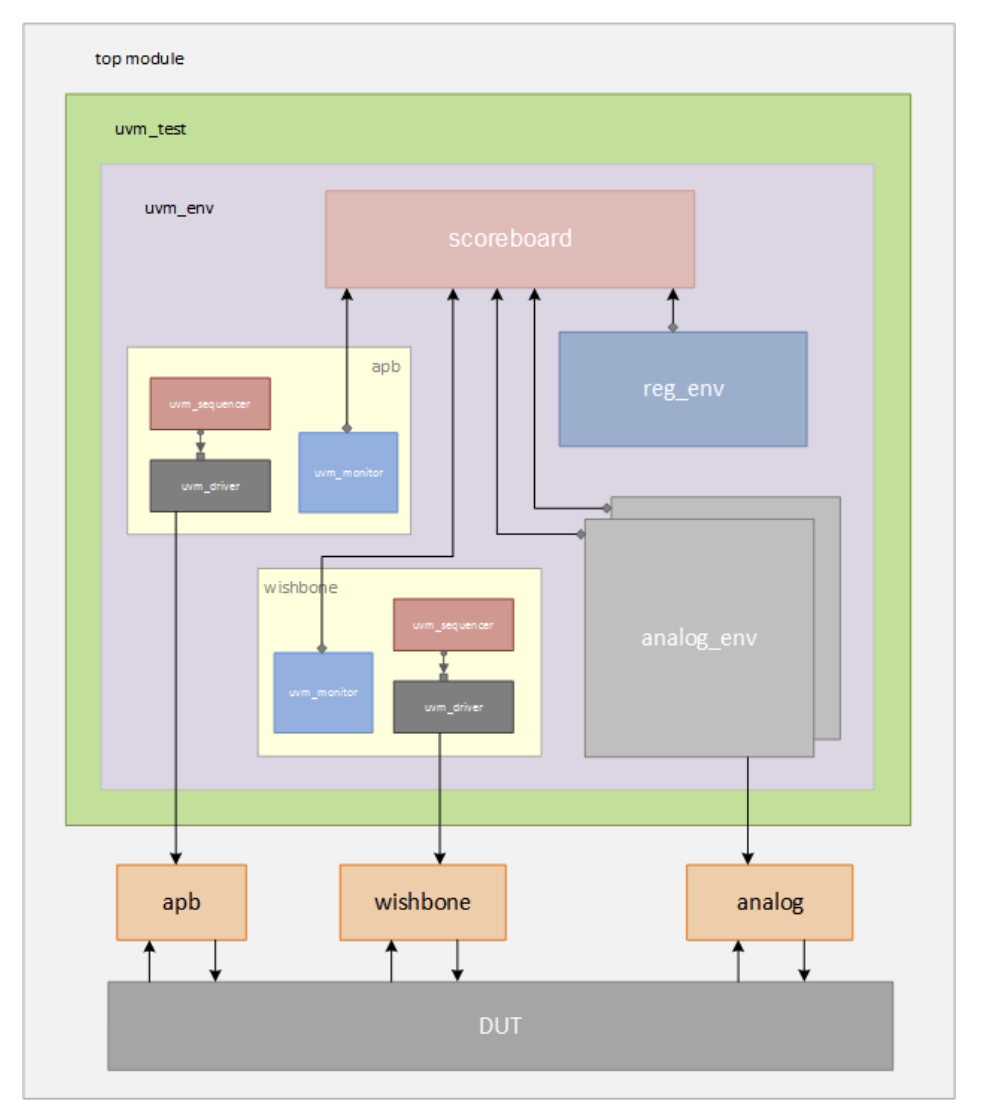

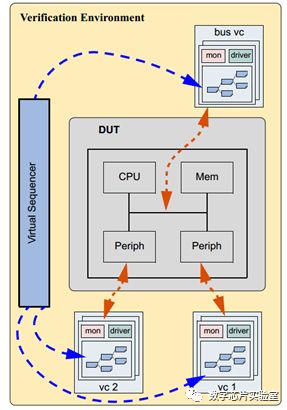

UVM平臺(tái)架構(gòu)主要是由通用驗(yàn)證組件(Universal Verification Component,UVC)構(gòu)成。每個(gè)UVC都是功能完備、可配置、封裝好的驗(yàn)證環(huán)境。根據(jù)UVC功能的不同,可分為接口UVC(Interface UVC)和模塊UVC(Module UVC)等。

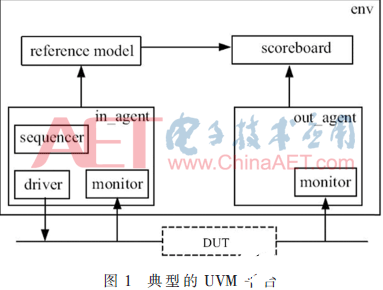

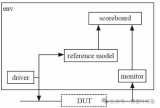

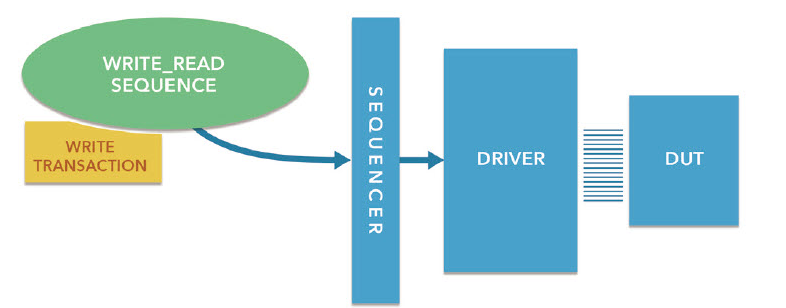

由圖1可知構(gòu)成UVM環(huán)境的常見組件類如下:

(1)uvm_driver類:是從uvm_sequencer中獲取事務(wù)(transaction),經(jīng)過轉(zhuǎn)化在接口中對(duì)DUT進(jìn)行時(shí)序激勵(lì)。diver類與sequencer類之間的通信就是為了獲取新的事務(wù)對(duì)象,這一操作通過pull方式實(shí)現(xiàn):

driver.seq_item_port.connect(sequencer.seq_item_export);

driver.rsp_port.connect(sequencer.rsp_export);

(2)uvm_monitor類:用來監(jiān)測(cè)數(shù)據(jù)。

(3)uvm_sequencer類:就像一個(gè)管道,從中傳送連續(xù)的激勵(lì)事務(wù),并最終通過TLM端口送至driver一側(cè)。

(4)uvm_agent類:用來封裝一個(gè)driver、一個(gè)monitor和一個(gè)sequencer。

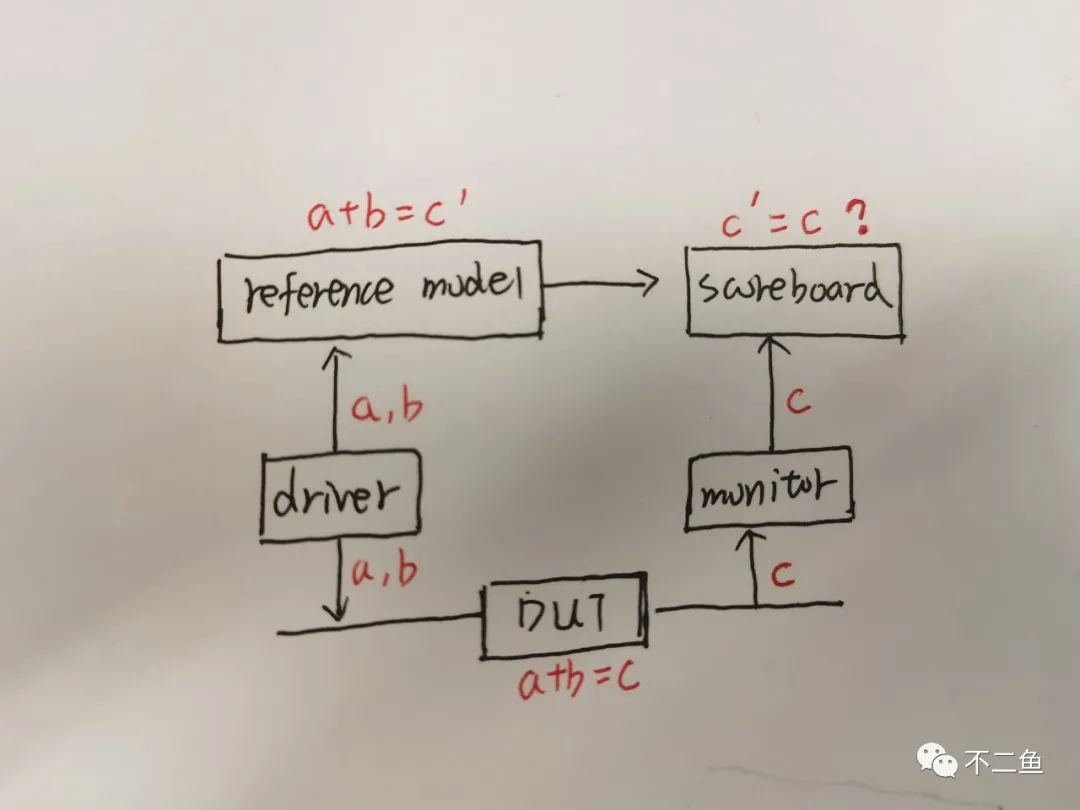

(5)reference_model:用于完成和DUT相同的功能。reference model的輸出被scoreboard接收,用于和DUT的輸出相比較。

(6)uvm_scoreboard:用來進(jìn)行數(shù)據(jù)比對(duì)和報(bào)告。

(7)uvm_env:是一個(gè)結(jié)構(gòu)化的容器,用來容納各組件。

(8)uvm_test:是驗(yàn)證環(huán)境的唯一入口,只有通過它才能正常運(yùn)轉(zhuǎn)uvm的phase機(jī)制。

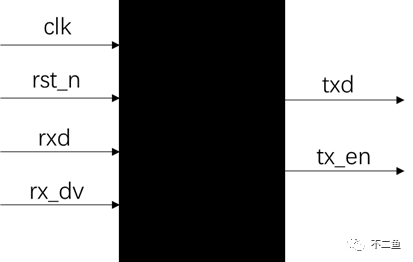

2 DUT介紹

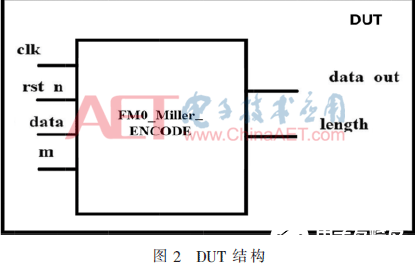

圖2中的DUT實(shí)現(xiàn)了FM0和Miller副載波調(diào)制編碼。在ISO/IEC18000-6C協(xié)議標(biāo)準(zhǔn)中,標(biāo)簽發(fā)送鏈路主要采用是FM0編碼和Miller編碼。編碼方式的選擇由m[1:0]來決定,只有當(dāng)m值為2′b00時(shí)才會(huì)選擇FM0編碼,m為2′b01、2′b10、2′b11時(shí)選擇Miller編碼。

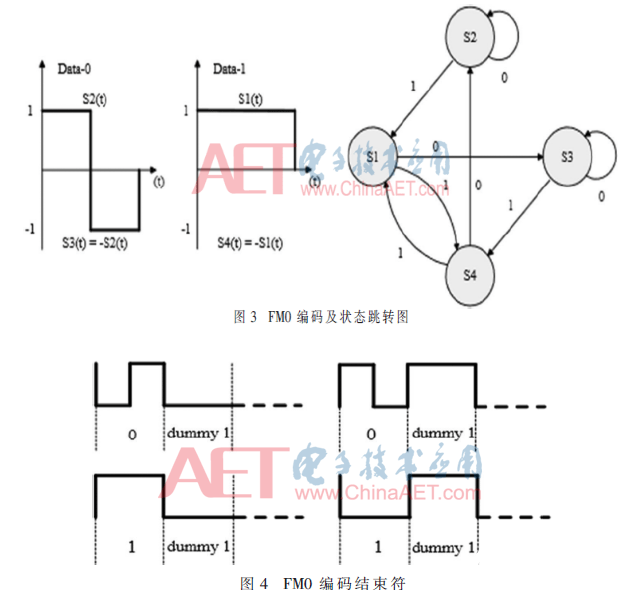

FM0編碼是通過電平翻轉(zhuǎn)的方式來實(shí)現(xiàn)編碼,數(shù)據(jù)碼元-0和-1翻轉(zhuǎn)的次數(shù)不同。碼元-0在碼元周期中間會(huì)發(fā)生一次電平翻轉(zhuǎn),而碼元-1只在每個(gè)碼元起始處發(fā)生電平翻轉(zhuǎn)。從圖3所示FM0編碼的狀態(tài)跳轉(zhuǎn)圖可以看出FM0編碼的碼元-0和-1的波形,而且在FM0編碼結(jié)束后需要在碼元數(shù)據(jù)的尾端添加結(jié)束標(biāo)志,結(jié)束標(biāo)志會(huì)以固定碼流來結(jié)束。碼元波形和結(jié)束符如圖4所示。

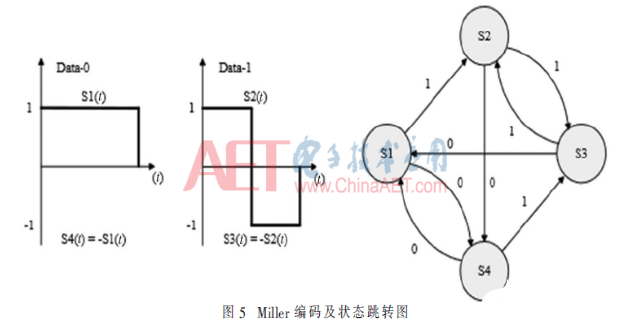

Miller編碼又稱為副載波調(diào)制編碼,也是通過電平翻轉(zhuǎn)的方式來實(shí)現(xiàn)編碼。編碼方式和狀態(tài)跳轉(zhuǎn)如圖5所示。

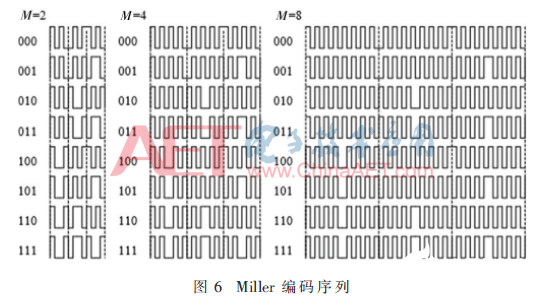

根據(jù)Miller編碼規(guī)則,按照m[1:0]值不同,每個(gè)數(shù)據(jù)可能被編碼成4位、8位16位碼元。如果m值為01,對(duì)應(yīng)M值為2,每個(gè)數(shù)據(jù)編碼為4位碼元;m值為10,對(duì)應(yīng)M值為4,每個(gè)數(shù)據(jù)編碼為8位碼元;m值為11,對(duì)應(yīng)M值為8,每個(gè)數(shù)據(jù)編碼為16位碼元。Miller編碼序列如圖6所示,每個(gè)編碼序列分別對(duì)應(yīng)M值為2、4、8。由圖可知數(shù)據(jù)編碼時(shí),只有在數(shù)據(jù)-0和-0邊界電平不發(fā)生翻轉(zhuǎn)跳變以外其他數(shù)據(jù)邊界處都會(huì)發(fā)生電平的翻轉(zhuǎn)跳變。

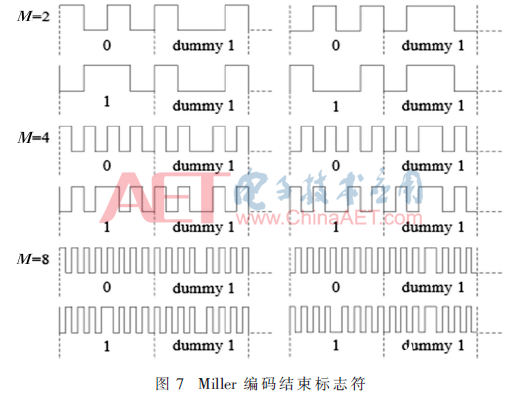

與FM0編碼類似,Miller除了采用電平翻轉(zhuǎn)實(shí)現(xiàn)編碼外,編碼結(jié)束后在數(shù)據(jù)的尾部同樣需要添加結(jié)束標(biāo)志。FM0采用固定碼流作為結(jié)束標(biāo)志,即保持持續(xù)碼元電平。但是Miller編碼的結(jié)束標(biāo)志相對(duì)會(huì)復(fù)雜一些,如圖7所示。

3 驗(yàn)證架構(gòu)

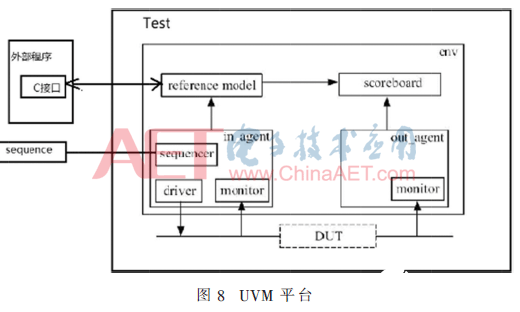

本文設(shè)計(jì)UVM平臺(tái)如圖8所示。

v 組件搭建描述:

(1)interface:聲明接口。

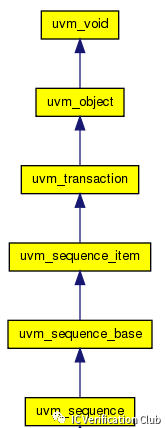

(2)transaction(數(shù)據(jù)包):繼承于uvm_sequence_item,利用隨機(jī)化和相關(guān)約束約束產(chǎn)生隨機(jī)數(shù)據(jù),創(chuàng)建兩個(gè)transaction對(duì)象,transaction_in在DUT輸入端輸入,transaction_out在DUT輸出與參考模型的輸出相比較。

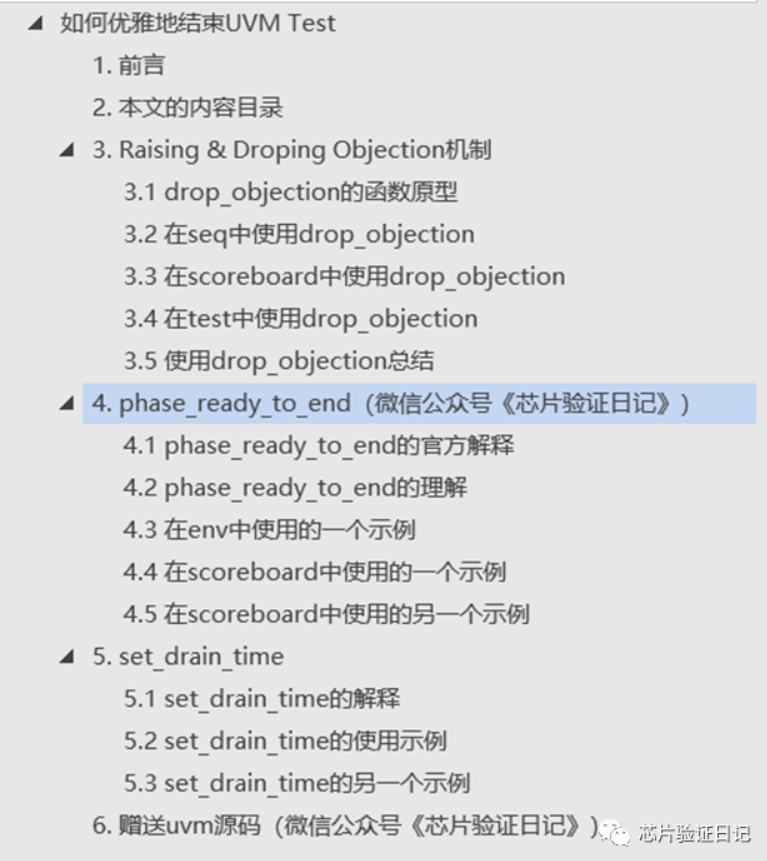

(3)sequence類:繼承于uvm_sequence,加入objection機(jī)制來控制驗(yàn)證平臺(tái)的關(guān)閉,利用repeat( )來控制執(zhí)行的次數(shù)。

(4)sequencer:繼承于uvm_sequencer,連接driver,實(shí)現(xiàn)數(shù)據(jù)的發(fā)送。

(5)driver類:繼承于uvm_driver,與sequencer連接,用來請(qǐng)求數(shù)據(jù)。

(6)monitor類:繼承于uvm_monitor,創(chuàng)建monitor_before和monitor_after,前者用來收集driver發(fā)送的數(shù)據(jù),后者用來監(jiān)測(cè)DUT的輸出,分別在monitor_after和monitor_before中設(shè)置covergroup用來收集功能覆蓋率。

(7)agent類:繼承于uvm_agent,創(chuàng)建i_agent和o_agent,前者用來封裝driver和monitor_before,后者用來封裝monitor_after,聲明并例化sequencer、driver、monitor,利用端口將它們連接起來。

(8)reference_model:繼承于uvm_component,將外部C_Model通過DPI調(diào)入,并將數(shù)據(jù)存儲(chǔ),用來與monitor監(jiān)測(cè)到的DUT的輸出做比較。

設(shè)計(jì)FM0編碼的C_Model。模型輸入包括了m參數(shù)、data,輸出編碼后數(shù)據(jù)及編碼后的數(shù)據(jù)長(zhǎng)度。首先需要將數(shù)據(jù)讀入模型,根據(jù)數(shù)據(jù)電平編碼。編碼算法主要設(shè)置一個(gè)變量data_tmp,在編碼開始時(shí)設(shè)置為1,如果是編碼-0,則輸出碼元~data_tmp和data_tmp,data_tmp值保持不變。如果是編碼-1,則輸出碼元~data_tmp和~data_tmp,data_tmp值取反。通過不斷更新data_tmp值來實(shí)現(xiàn)數(shù)據(jù)的編碼輸出,編碼完成后添加結(jié)束標(biāo)識(shí)符。

設(shè)計(jì)Miller副載波調(diào)制編碼的C_Model,模型輸入包括了m參數(shù)、data,結(jié)合副載波調(diào)制類型和數(shù)據(jù)類型,將編碼后的數(shù)據(jù)及長(zhǎng)度輸出,另外,由于Miller前同步碼最后一位碼元電平為低,因此其初始data_tmp應(yīng)為0,結(jié)合m的值進(jìn)行編碼,編碼完成后添加結(jié)束標(biāo)識(shí)符。

(9)Scoreboard類:繼承于uvm_scoreboard,將monitor_after檢測(cè)到的輸出與reference_model得到的輸出做比較。

(10)env類:繼承于uvm_env,聲明并例化agent,reference_model,scoreboard,利用端口將它們連接起來。

(11)Test類:繼承于uvm_test,聲明并例化env,設(shè)置default_sequence來啟動(dòng)sequence。

(12)Top模塊:聲明接口,實(shí)現(xiàn)DUT和平臺(tái)互連,設(shè)置時(shí)鐘信號(hào)。

4 仿真結(jié)果

環(huán)境搭建完畢后用QuestaSim進(jìn)行仿真驗(yàn)證,根據(jù)輸出的波形和驗(yàn)證信息比較DUT功能的正確與否,并查看輸出的功能覆蓋率來檢測(cè)各功能點(diǎn)的實(shí)現(xiàn)狀況。

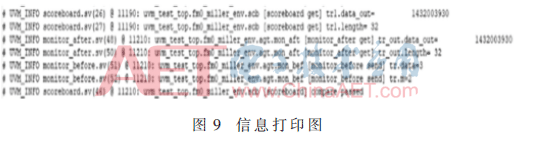

由圖9所示可以發(fā)現(xiàn),UVM計(jì)分板中顯示驗(yàn)證通過,DUT的輸出和模型的輸出是一致的,DUT的設(shè)計(jì)滿足功能實(shí)現(xiàn)。

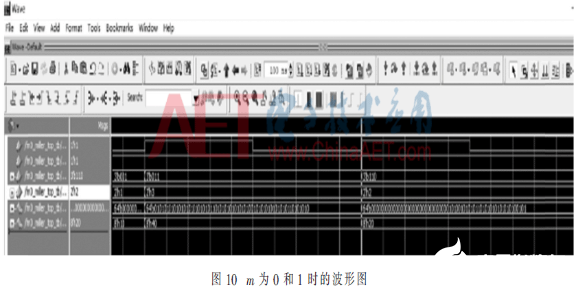

由圖10可知,m=0時(shí),執(zhí)行FM0編碼,m=1時(shí),即執(zhí)行miller編碼,每個(gè)數(shù)據(jù)分別編碼為2和4個(gè)碼元,由圖可知:m=0,data=3′b000,得到編碼后的數(shù)據(jù)為01010100,數(shù)據(jù)長(zhǎng)度為8位,最后2位是結(jié)束標(biāo)識(shí)符00,根據(jù)FM0編碼原則結(jié)果是正確的;而m=1,data=3′111,得到的編碼后數(shù)據(jù)為1001_0110_1001_0110,數(shù)據(jù)長(zhǎng)度為16位,最后4位0110是結(jié)束標(biāo)識(shí)符,根據(jù)miller編碼原則結(jié)果是正確的。

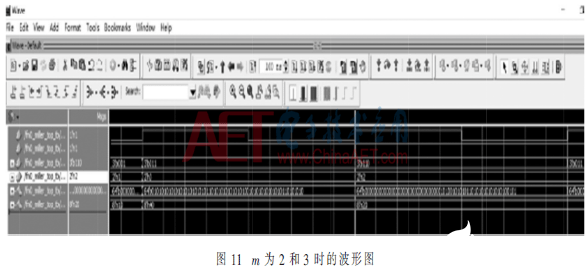

由圖11可知,m=2和3時(shí),即執(zhí)行miller編碼,每個(gè)數(shù)據(jù)分別編碼為8和16個(gè)碼元,由圖可知:m=2,data=3′b110,得到編碼后的數(shù)據(jù)為1010_0101_0101_1010_1010_1010_1010_0101,數(shù)據(jù)長(zhǎng)度為32位,最后8位是結(jié)束標(biāo)識(shí)符1010_0101,根據(jù)miller編碼原則結(jié)果是正確的;而m=3,data=3′011,得到的編碼后數(shù)據(jù)為0101_0101_0101_0101_0101_0101_1010_1010_1010_1010_0101_0101_0101_0101_1010_1010,數(shù)據(jù)長(zhǎng)度為64位,最后16位0101_0101_1010_1010是結(jié)束標(biāo)識(shí)符,根據(jù)miller編碼原則結(jié)果也是正確的。

圖12是一個(gè)由覆蓋率驅(qū)動(dòng)并且受約束的隨機(jī)分層測(cè)試平臺(tái)所產(chǎn)生的整個(gè)FM0、Miller編碼仿真波形圖,由圖可見,平臺(tái)跑了很多個(gè)testcase。

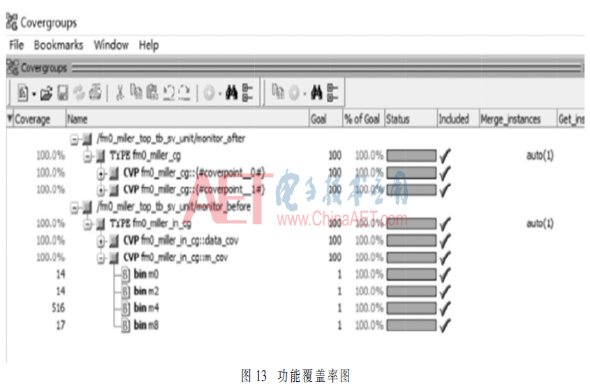

圖13描述此DUT的功能覆蓋率,F(xiàn)M0編碼以及Miller編碼的3種模式都覆蓋到了,各功能點(diǎn)的覆蓋率達(dá)到了100%。

5 結(jié)論

UVM驗(yàn)證方法學(xué)作為目前主流的IC驗(yàn)證方法學(xué),盡管在前期搭建驗(yàn)證平臺(tái)的的時(shí)間較長(zhǎng),但是執(zhí)行效率很高,可以縮短整個(gè)研發(fā)的驗(yàn)證時(shí)間。本文介紹了基于DPI-C接口和UVM相結(jié)合的驗(yàn)證環(huán)境,實(shí)現(xiàn)了C程序與基于UVM環(huán)境的接口對(duì)接,使用受約束的隨機(jī)激勵(lì)以及覆蓋率驅(qū)動(dòng),使驗(yàn)證平臺(tái)中程序開發(fā)方便且調(diào)試方便,縮短了驗(yàn)證周期,保證了驗(yàn)證的完備性,有效地縮短了驗(yàn)證周期,提高了驗(yàn)證效率,加大了芯片的面試可能性。

參考文獻(xiàn)

[1] 張強(qiáng).UVM實(shí)戰(zhàn)[M]。北京:機(jī)械工業(yè)出版社,2014.

[2] 劉斌。芯片驗(yàn)證漫游指南[M]。北京:電子工業(yè)出版社,2018.

[3] 程剛,蔡敏。基于SystemVerilog的SoC功能驗(yàn)證方法研究[J]。科學(xué)技術(shù)與工程,2009(22):6814-6818.

[4] 克里斯·斯皮爾.SystemVerilog驗(yàn)證[M]。張春,譯。北京:科學(xué)出版社,2009.

[5] 徐偉俊,楊鑫,陳先勇,等。針對(duì)功能覆蓋率的驗(yàn)證過程[J]。中國集成電路,2007(7):58-62.

[6] 克里斯·斯皮爾.SystemVerilog驗(yàn)證:測(cè)試平臺(tái)編寫指南[M]。張春,麥宋平,趙益新,譯。北京:科學(xué)出版社,2009.

[7] 李璐,周春良,馮曦,等。基于DPI-C接口的可擴(kuò)展SOC驗(yàn)證平臺(tái)[J]。電子設(shè)計(jì)工程,2018,26(4):136-140.

[8] Michael Keating.Reuse methodology manual for system-on-a-chip design[M].Third Edition.Kluwer Academic Publishers,2002.

電子發(fā)燒友App

電子發(fā)燒友App

評(píng)論