介紹了一種應用于通用微處理器系統中的SDRAM與雙口RAM之間的數據轉移接口控制電路,由VHDL語言設計,用Xilinx公司4000系列FPGA實現,目前該電路硬件實現和微處理器系統已經通過驗證,證

2011-11-11 09:43:14 1415

1415

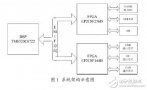

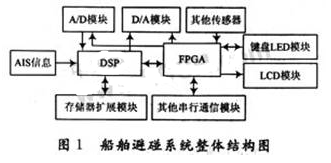

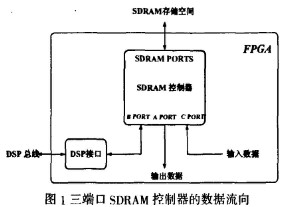

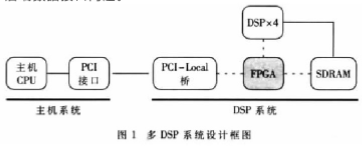

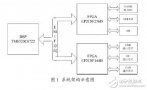

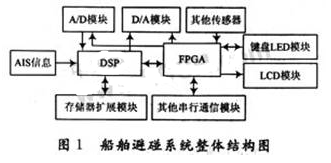

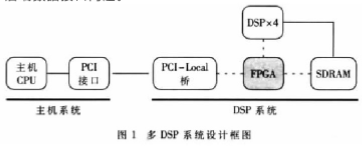

提出一種DSP 通過EMIF 接口控制復雜系統的方案。通過將DSP 芯片連接多片FPGA,并利用FPGA 與各種外部芯片連接,使得DSP 通過EMIF 接口就能控制各種芯片,實現復雜系統的控制。這樣節省DSP 的引腳資源,使DSP 的運算功能得以更充分的發揮。

2013-06-13 15:55:57 5573

5573

本帖最后由 yelo168 于 2015-6-21 15:07 編輯

DSP6713復位SDRAM(32位數據總線接法,CE0空間),FPGA(CE2),比如往0x80000000,0x80000004寫0xAAAAAAAA,只有高16位寫進去了,低16位還是FFFF。????

2015-06-20 10:22:06

用的貴公司的TL138F-EVM A2開發板。想利用SPI協議實現FPGA和DSP通信。看了核心板引腳說明 沒有看到FPGA這邊SPI協議要用的接口,是不是這塊板子不能實現DSP和FPGA的SPI通信。麻煩床龍工程師指導下。還有其他方法嗎?

2020-04-24 06:46:47

: ARM+DSP+FPGA 綜合實驗系統 為了開發使用方便,做了大量考慮。開發系統中大量的資源被有結構的組織起來。系統中不同部分的數據路徑通暢合理,能夠最大限度的滿足各種應用的需求。外圍接口 非常豐富,每個子系統都有各自

2010-12-25 15:47:19

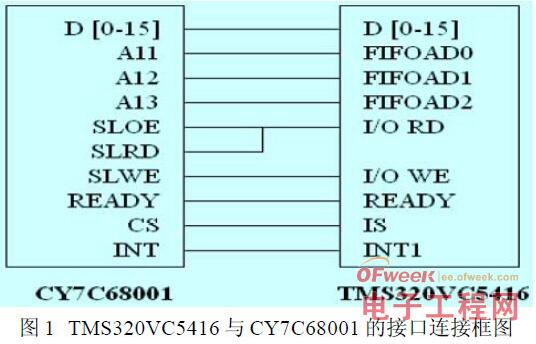

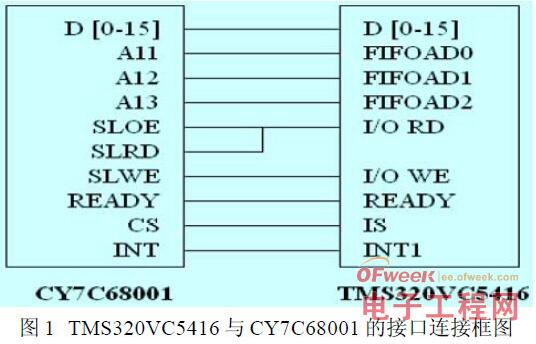

的EZ-USB FX2系列智能USB接口芯片。其作用是將主機所發送的命令序列經USB2.0端口輸出,實現對數據采集系統的控制;同時把A/D轉換器采集的數據以高速的數據序列形式發送到主機。其中,USB2.0端口

2020-01-07 07:00:00

個周期內可同時完成相乘及累加運算。5、 有DMA通道控制器及串行通信口等,便于數據傳送。6、 有中斷處理器及定時控制器,便于構成小規模系統。7、 具有軟硬件等待功能,能與各種存儲器接口。DSP作為專門

2019-05-07 01:28:40

和比較,并給出了FPGA與這兩種DSP芯片進行鏈路口通倍的具體方法。在FPGA內部實現了DSP鏈路口的設計,同時給出了DSP進行鏈路口通信的具體設置方法。由于實時處理中數據的重發會嚴重影響處理的實時性

2019-06-19 05:00:08

和比較,并給出了FPGA與這兩種DSP芯片進行鏈路口通倍的具體方法。在FPGA內部實現了DSP鏈路口的設計,同時給出了DSP進行鏈路口通信的具體設置方法。由于實時處理中數據的重發會嚴重影響處理的實時性,故

2018-12-04 10:39:29

DSP芯片的鏈路口進行了分析和比較,并給出了FPGA與這兩種DSP芯片進行鏈路口通倍的具體方法。在FPGA內部實現了DSP鏈路口的設計,同時給出了DSP進行鏈路口通信的具體設置方法。由于實時處理中數據

2019-06-21 05:00:04

更快、更大,每比特的功耗也更低,但是如何實現FPGA和DDR3 SDRAM DIMM條的接口設計呢? 關鍵字:均衡(leveling)如果FPGA I/O結構中沒有包含均衡功能,那么它與DDR3

2019-04-22 07:00:08

的數目之外,就是采用可編程邏輯器件,主要是FPGA芯片來實現。本課程以DSP設計在FPGA芯片上的開發為主線,遵照由淺入深的基本步驟和思路進行詳細講解,每一個知識點都給出了基于ISE(HDL語言

2009-07-21 09:22:42

多,就需要較多的外圍芯片,體積、功耗都比較大。采用FPGA的方案后,接口邏輯都可以在FPGA內部來實現了,大大簡化了外圍電路的設計。 在現代電子產品設計中,存儲器得到了廣泛的應用,例如SDRAM、SRAM

2020-10-26 14:35:32

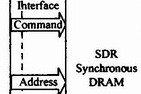

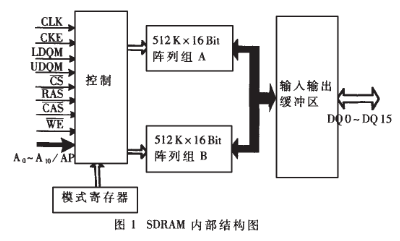

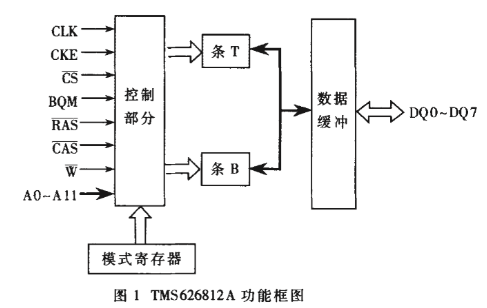

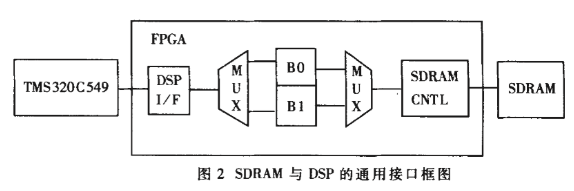

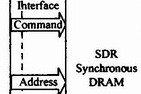

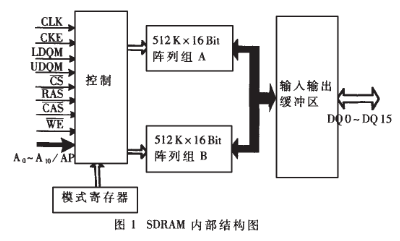

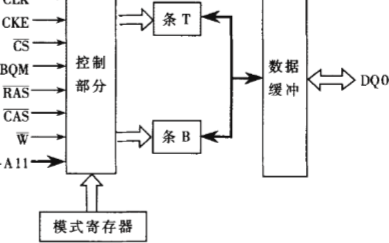

現場電路設計中。本文用 FPGA 作為接口芯片,提供控制信號和定時信號,來實現 DSP 到 SDRAM 的數據存取。1 、SDRAM 介紹本文采用的 SDRAM 為 TMS626812A,圖 1 為其

2020-04-23 08:00:00

FPGA怎么實現控制CF從SDRAM中讀取數據以及實現CF卡向SDRAM中上傳數據????本人初學者,希望大家幫幫忙!!!!謝謝!!

2013-02-25 21:58:59

實戰應用,這種快樂試試你就會懂的。話不多說,上貨。SDR SDRAM驅動設計實用進階 本篇實現基于叁芯智能科技的SANXIN -B01 FPGA開發板,以下為配套的教程,如有入手開發板,可以登錄官方

2023-03-27 17:09:14

和后仿真。以上介紹了一種應用于通用微處理器系統中的SDRAM與雙口RAM之間的數據轉移接口控制電路,由VHDL語言設計,用Xilinx公司4000系列FPGA實現,目前該電路硬件實現和微處理器系統已經通過驗證,證明可將SDRAM作為高速、大容量存儲器應用在簡單電子系統中。

2019-06-10 05:00:08

幀結構,緩存系統的設計需要保存原始采樣數據并能夠實現數據的重組幀,以滿足不同處理需求。針對以上問題,本文提出了一種基于文件結構存儲方式的數據緩存系統,該系統利用FPGA設計結構化狀態機實現對SDRAM的控制,完成了對數據的緩存與重組幀,具有速度快、可靠性高、靈活性強和功能可擴展等優點。

2012-08-13 10:40:40

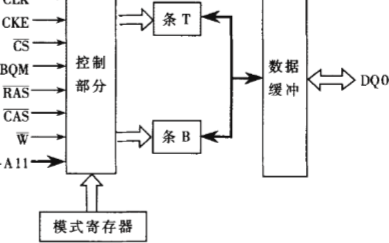

對SDRAM的控制,并通過利用FPGA控制數據存取的順序來實現對數字視頻圖像的旋轉,截取、平移等實時處理。SDRAM的控制原理,如圖1所示。 [/hide]

2009-11-13 11:37:08

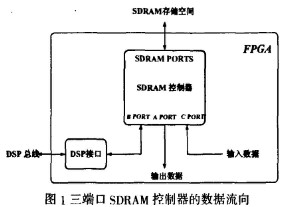

緩沖存儲器,且緩沖存儲器一般選用同步動態隨機存儲器(SDRAM)。由于DSP不能直接與SDRAM接口,而且SDRAM控制時序比較復雜,因此本文介紹如何利用電可擦除可編程邏輯器件實現TMS320C5402

2018-12-07 10:35:02

,討論了在系統設計的過程中應該重點注意的幾個問題和ADSP-TS201的外部接口技術,并給出了其與SDRAM,FPGA的連接實例,對基于TigerSHARC系列DSP的應用設計具有實用的參考價值。來源

2019-04-12 07:00:11

。 在該系統中,由FPGA的完成各模塊之間的接口控制。FPGA接收從前端傳送過來的高速數字信號,并將其存儲在DDR SDRAM中;DSP通過FPGA讀取DDR中的數據,處理后再送回到DDRSDRAM,最后

2018-12-18 10:17:15

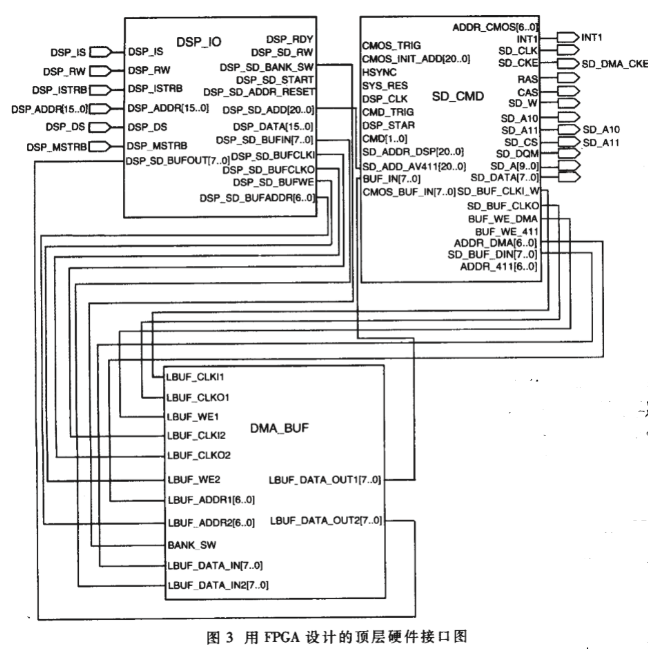

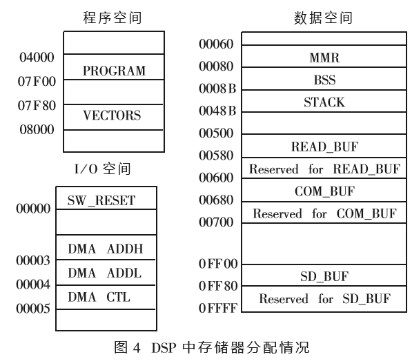

基于DSP5509 的數據采集系統系統采用了DSP + FPGA 的雙核結構,由CMOS 感光芯片OV7620 采集圖像,得到數據源, FPGA 作為輔助處理器,控制部分外圍器件并協助采集數據

2009-04-28 10:47:02

儀器儀表及控制裝置中,易于產品化。設計出的具有HDLC功能的FPGA芯片已應用于導航設備樣機的有線通訊鏈路中,成功實現了雙向數據通信。基于軟件編程與FPGA來共同實現HDLC協議,方法靈活、速度快。適合于DSP+FPGA的數字硬件平臺的接口設計,實現后可靠有效。

2011-03-17 10:23:56

處理器的數目之外,就是采用可編程邏輯器件,主要是FPGA芯片來實現。本課程以DSP設計在FPGA芯片上的開發為主線,遵照由淺入深的基本步驟和思路進行詳細講解,每一個知識點都給出了基于ISE(HDL語言

2009-07-21 09:20:11

的一些不項目描述:通過fpga控制ad對芯片參數進行采集,利用dsp對數據進行預處理,并根據測試結果對測試進行一些控制,處理的數據通過pcie發給上位機。項目規劃:1、首先通過開發板帶例子學習

2015-10-09 15:10:00

。5.總線接口模塊:實現與DSP總線接口,通過DSP的EMIF讀操作,從FIFO中讀取數據到DSP外擴SDRAM中,以便后續數據處理。4、DSP模塊功能介紹[21]:DSP內部主要包括高速有效的對DDR3

2015-11-06 10:01:48

,能與各種存儲器接口。

DSP作為專門的,主要用于計算,優勢是軟件的靈活性。適用于條件進程,特別是復雜的多算法任務。DSP通過匯編或高級語言(如C語言)進行編程,實時實現方案。因此,采用DSP器件的優勢

2023-06-01 11:03:14

為什么利用Spartan-3 FPGA來實現DSP系統?Spartan-3系列器件在平板顯示器中的應用有哪些?

2021-04-29 06:32:17

為什么利用Spartan-3 FPGA來實現DSP系統?Spartan-3系列器件在平板顯示器中的應用有哪些?

2021-04-30 07:12:22

逆變換的實現,VGA控制,數據的編解碼,解復用,高達上Gbps的信號的處理,協議的轉換實現等等等等功能,都是DSP難以勝任的。 DSP內部有很多現成的硬件模塊和接口以及控制器,但是需要軟件編程設定,可以

2016-12-23 16:56:04

課程介紹1. SDRAM文檔的閱讀和理解2. SDRAM的功能匯總3. SDRAM的實現架構4. SDRAM接口的模塊劃分5. SDRAM的時序分析和約束練習3說明視頻,轉碼問題,上傳不了。需要完整

2022-02-15 10:26:33

自己做的DSP開發板,在DSP對SDRAM進行寫操作的時候,發現一個問題:當往SDRAM中寫的地址數超過128個的時候,再尋址的時候第8根地址線會亂掉,導致地址錯位,此時,數據線第8根電壓也反向了

2014-04-23 20:14:39

,時間信號解碼器,時序控制觸發器。FPGA芯片通過16位HPI接口與DSP相連,同時外擴32位以太網控制總線與以太網接口芯片相連。實現網絡報文從接口芯片到DSP之間的數據鏈橋接。 3]數字化繼電保護

2018-09-06 10:21:51

1394b作為一種與平臺無關的技術,可以同時應用在MAC和PC中,本文研究的主要內容是利用FPGA、DSP和PCI9054芯片實現1394b數據傳輸系統。現在國內基本上還停留在1394或1394a總線

2012-05-14 12:35:39

拆包處理,發送模塊用來與DSP鏈路口接收通道進行連接和數據打包處理;接收緩沖/發送緩沖分別是用來配合接 收模塊和發送模塊進行傳輸時作為數據緩沖區,并實現與系統中其他接口或者FPGA中的其他模塊的接口

2019-05-21 05:00:19

基于FPGA的SDRAM設計與實現

2013-03-14 18:34:25

進行了DDR3 SDRAM控制器的編寫,分析并提出了提高帶寬利用率的方法。最終將其進行類FIFO接口的封裝,屏蔽掉了DDR3 IP核復雜的用戶接口,為DDR3數據流緩存的實現提供便利。系統測試表明,該

2018-08-02 09:34:58

引言 本文從實際應用的角度出發,采用FPGA作為主控芯片,設計了一款數字視頻接口轉換設備,該設備針對于MT9M111這款數字圖像傳感器產生的ITU-R BT.656格式數據進行采集、色彩空間變換

2018-12-11 10:59:36

輸入,一路Base CameraLink輸出,2路Rs232,1路USB2.0,一路千兆以太網。 FPGA控制高速SDRAM數據存取,并與DSP之間構建64-bit高速同步數據總線接口;一片TI

2012-07-06 16:17:50

對SDRAM的主要操作路徑及操作過程,應用于解復用的SDRAM接口電路的設計方法;最后給出了實現結果。 1 SDRAM的主要控制信號和基本命令SDRAM的主要控制信號為:·CS:片選使能信號?低電平

2018-12-03 15:20:48

在雷達信號處理、數字圖像處理等領域中,信號處理的實時性至關重要。由于FPGA芯片在大數據量的底層算法處理上的優勢及DSP芯片在復雜算法處理上的優勢,DSP+FPGA的實時信號處理系統的應用越來越廣泛。那么,我們該怎么利用FPGA與ADSP TS201設計總線接口呢?

2019-08-09 06:56:11

請問如何利用電可擦除可編程邏輯器件實現TMS320C5402與SDRAM的接口?

2021-04-15 06:24:39

本文根據十接口千兆以太網線路接口卡設計的功能需求和性能需求,按照數據處理流程劃分功能模塊,以PM3388作為鏈路層處理芯片和兩片高性能FPGA作為鏈路層處理芯片完成了系統設計,并給出了具體實現方案。

2021-04-28 06:28:33

均衡的定義和重要性是什么如何實現FPGA和DDR3 SDRAM DIMM條的接口設計?

2021-05-07 06:21:53

如何實現Reg istered SDRAM接口電路的設計?Reg istered SDRAM的工作原理是什么?Registered SDRAM接口電路的原理設計與布局布線規則是什么?

2021-04-12 07:10:21

本文提出了一種基于FPGA的SDRAM控制器的設計方法,并用Verilog給于實現,仿真結果表明通過該方法設計實現的控制器可以在FPGA芯片內組成如圖1所示的SDRAM接口,從而使得系統用戶對SDRAM的操作非常方便。

2021-04-15 06:46:56

1.SDRAM引入1.1 常見存儲器介紹:DRAM介紹同步動態隨機存取內存(synchronous dynamic random-access memory,簡稱SDRAM),有一個同步接口的動態

2022-05-16 15:03:13

本文用FPGA作為接口芯片,提供控制信號和定時信號,來實現DSP到SDRAM的數據存取。

2021-05-06 09:25:24

領域。本文基于雷達實時信號處理的需要,用FPGA實現了多DSP信號處理模板局部總線和基于標準VME總線的計算機進行通信的接口設計。 2 VME總線的功能特點VME總線系統的功能結構可以分為4類:數據

2019-04-22 07:00:07

第39章 STM32F429的FMC總線應用之SDRAM本章教程為大家講解SDRAM的驅動實現,后面LCD的顯存和大數量的存取都要用到。目錄第39章 STM32F429的FMC總線應用之

2021-08-10 06:39:31

我現在在設計電路,結構是一片FPGA和兩片TMS320C6747(456M的那款),數據是先從FPGA傳輸到DSP1做處理,再從DSP1傳輸到DSP2中。FPGA到DSP1采用EMIFA接口

2018-07-25 07:49:42

是整個溫控系統的硬件基礎,其中涉及到溫度采集,與微處理器通信,串口輸出,控制數模轉換芯片等多個組成部分。本文提出一種高效實用的FPGA接口設計,它能夠完成協調各個組成部分有序工作,準確、快速實現數據

2020-08-19 09:29:48

(包括YCbCr數據流、行場同步信號和像素時鐘)經ITU輸入接口送入FPGA主控芯片。FPGA主控芯片對ITU信號進行解交織和色彩空間轉換,再將轉換后的每個像素的RGB值寫入SDRAM存儲器。再由

2019-04-22 07:00:11

引言 本文從實際應用的角度出發,采用FPGA作為主控芯片,設計了一款數字視頻接口轉換設備。 該設備針對于MT9M111這款數字圖像傳感器產生的ITU-R BT.656格式數據進行采集、色彩空間

2019-05-05 09:29:33

的ITU信號(包括YCbCr數據流、行場同步信號和像素時鐘)經ITU輸入接口送入FPGA主控芯片。FPGA主控芯片對ITU信號進行解交織和色彩空間轉換,再將轉換后的每個像素的RGB值寫入SDRAM存儲器

2019-04-23 07:00:10

引言 本文從實際應用的角度出發,采用FPGA作為主控芯片,設計了一款數字視頻接口轉換設備,該設備針對于MT9M111這款數字圖像傳感器產生的ITU-R BT.656格式數據進行采集、色彩空間變換

2019-04-17 07:00:05

引言本文從實際應用的角度出發,采用FPGA作為主控芯片,設計了一款數字視頻接口轉換設備,該設備針對于MT9M111這款數字圖像傳感器產生的ITU-R BT.656格式數據進行采集、色彩空間變換

2019-05-29 05:00:03

首先提出了一個通用DSP系統的設計方案,主要給出了FPGA在系統中的位置和作用。然后簡要介紹了FPGA的各個功能模塊,著重針對DSP和SDRAM接口進行了討論,針對數據寬度和時鐘速率不匹配的特點,提出雙狀態機

2019-05-17 07:00:13

GPIF向量組成一個GPIF波形,匹配受控接口的時序。ADSP-TS101作為彈載主DSP芯片,含4個鏈路口,每個鏈路口可在時鐘雙沿以8位進行雙向數據傳輸,速率高達250 MB/s。通過該接口,DSP

2019-05-31 05:00:04

介紹基于現場可編程門陣列(FPGA),利用VHDL 語言設計實現MMC2107 與SDRAM 接口電路。文中包括MMC2107 組成結構、SDRAM 存儲接口結構和SDRAM 控制狀態機的設計。

2009-05-15 14:47:29 24

24 使用EMIF將Xilinx FPGA與TI DSP平臺接口:本應用指南使用外部存儲器接口 (EMIF) 實現了 Xilinx FPGA 到 Texas Instruments 數字信號處理器 (DSP) 平臺的幾種連接。指南目錄本手冊包含以下章節

2009-11-01 15:00:09 68

68 比較了多種DSP芯片的互連性能,給出了一種簡單高性能DSP網絡結構。針對構成DSP網絡通訊接口的鏈路口,分析其基本特點,并且提出了在FPGA中實現的設計原理。最后給出了設計仿真圖和

2010-07-27 16:46:46 22

22 設計一種基于DSP和FPGA架構的通用圖像處理平臺,運用FPGA實現微處理器接口設計,并對圖像數據進行簡單預處理,利用DSP進行復雜圖像處理算法和邏輯控制,實現圖像數據的高速傳輸

2010-12-25 17:06:54 60

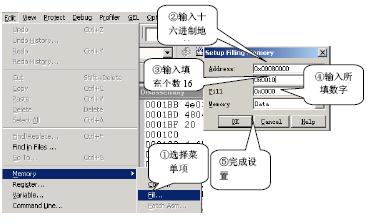

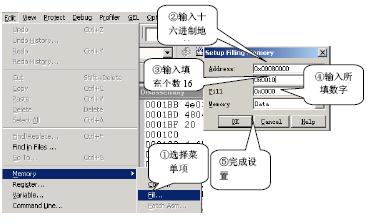

60 實驗5:DSP數據存取實驗一.實驗目的1.了解TMS320F2812A的內部存儲器空間的分配及指令尋址方式。2.了解ICETEK-F2812-A評估板擴展存儲器空間尋址方法,及其應用

2009-03-17 00:16:59 3815

3815

摘 要:介紹了SDRAM的特點和工作原理,提出了一種基于FPGA的SDRAM控制器的設計方法,使用該方法實現的控制器可非常方便地對SDRAM進行控制。

關鍵

2009-06-20 13:04:51 2075

2075 基于DSP和FPGA的通用圖像處理平臺設計

摘要:設計一種基于DSP和FPGA架構的通用圖像處理平臺,運用FPGA實現微處理器接口設計,并對圖像數據進行簡單預處理,利用DSP

2010-02-01 11:10:21 1379

1379

本文提出了一種基于文件結構存儲方式的數據緩存系統,該系統利用FPGA設計結構化狀態機實現對SDRAM的控制,完成

2010-11-25 11:19:03 1009

1009

為了降低DSP外部SDRAM存儲系統的功耗,針對DSP訪問片外SDRAM的功耗來源特點,提出了基于總線利用率動態監測的讀寫歸并方案。該方案動態監測外部存儲器接口(EMIF)總線的利用率,根據總線利用率的不同選擇開放的頁策略、封閉的頁策略或休眠模式;設計了簡化

2011-01-14 17:40:12 50

50 摘要:為了實現高速HDLC通訊協議,設計了DSP+FPGA結構的485通訊接口,接口包括DSP、FPGA、485轉換等硬件電路,以及DSP與FPGA之間的數據交換程序和FPGA內部狀態機;其中DSP用于實現數據控制,FPGA用于實現HDLC通訊協議,DSP與FPGA之間采用XINTF方式,通過雙FI

2011-02-25 17:24:34 98

98 摘要: 在高速并行流水信號處理中,ASIC(FPGA)+DSP+RAM是目前國際流行的一種方式,尤其是FPGA+DSP+RAM更適合中國的國情.本文利用FPGA的算術邏輯單元與外部存儲器相結合,解決了線路板面積有限與雷達數據處理需要大量存儲空間的矛盾;利用FPGA的并行流水特點解決了

2011-02-27 16:00:26 83

83 在本文工作的基礎上,可以進一步發揮FPGA的靈活性。如可以利用FPGA實現DSP功能,從而提供音頻DSP處理或編碼解碼;也可以與SoPC相結合,作為音頻接口模塊,為片上系統提供音頻接口

2011-06-24 10:38:33 7291

7291

在雷達信號處理、數字圖像處理等領域中,信號處理的實時性至關重要。由于FPGA芯片在大數據量的底層算法處理上的優勢及DSP芯片在復雜算法處理上的優勢,DSP+FPGA的實時信號處理系統

2012-07-05 15:01:40 7272

7272

使用功能強大的FPGA來實現一種DDR2 SDRAM存儲器的用戶接口。該用戶接口是基于XILINX公司出產的DDR2 SDRAM的存儲控制器,由于該公司出產的這種存儲控制器具有很高的效率,使用也很廣泛,

2013-01-08 18:15:50 237

237 基于FPGA的高速DSP與液晶模塊接口的實現

2017-10-19 13:46:23 3

3 摘要 利用異步FIFO實現FPGA與DSP進行數據通信的方案。FPGA在寫時鐘的控制下將數據寫入FIFO,再與DSP進行握手后,DSP通過EMIFA接口將數據讀入。文中給出了異步FIFO的實現

2017-10-30 11:48:44 1

1 為了滿足高速圖像數據采集系統中對高帶寬和大容量的要求,利用Virtex-7 系列FPGA 外接DDR3 SDRAM 的設計方法,提出了一種基于Verilog-HDL 語言的DDR3 SDRAM

2017-11-17 14:14:02 3290

3290

控制器,在介紹控制器的邏輯結構的基礎上,對FPGA與SDRAM間數據通信進行了時序分析,實現SDRAM 帶有自動預充電突發讀寫和非自動預充電整頁讀寫。

2017-11-18 12:42:03 2054

2054

的I/O功能,實現外圍輸入輸出接口如其他串行口、ADC數據采集緩存等硬件電路,使部分數據采集和數據通信的I/O任務由DSP和FPGA協同承擔,從而使DSP減輕負擔,可以更專注于避碰的復雜算法。FPGA還可以實現

2020-05-13 07:57:00 1705

1705

,且緩沖存儲器一般選用同步動態隨機存儲器(SDRAM)。由于DSP不能直接與SDRAM接口,而且SDRAM控制時序比較復雜,因此本文介紹如何利用電可擦除可編程邏輯器件實現TMS320C5402與SDRAM的接口。

2020-04-09 08:02:00 1784

1784

SDRAM 具有存儲容量大、速度快、成本低的特點,因此廣泛應用于雷達信號處理等需 要海量高速存儲的場合,但是SDRAM 的操作相對復雜,需要有專門的控制器配合處理器 工作完成數據的存取操作。隨著FPGA 技術的快速發展及其應用的普及,用FPGA 實現 SDRAM 控制器是目前最流行的技術手段。

2019-04-26 08:06:00 2129

2129

在基于FPGA的SOC設計中,常使用串口作為通信接口,但直接用FPGA進行串口通信數據的處理是比較繁雜的,特別是直接使用FPGA進行串口通信的協議的解釋和數據打包等處理,將會消耗大量的FPGA硬件

2019-08-02 08:08:00 3816

3816 實現數據的高速大容量存儲是數據采集系統中的一項關鍵技術。本設計采用Altera 公司Cyclone系列的FPGA 完成了對DDR SDRAM 的控制,以狀態機來描述對DDR SDRAM 的各種時序

2019-08-14 08:00:00 3401

3401

本文檔的主要內容詳細介紹的是FPGA讀寫SDRAM的實例和SDRAM的相關文章及一些SDRAM控制器設計論文主要包括了:FPGA讀寫SDRAM的實例,SDRAM控制器核心介紹,系列SDRAM數據手冊

2018-12-25 08:00:00 56

56 交換。DSP用于實現USB協議,通過DSP編程實現DSP數據通過USB接口與PC機通信,且USB芯片的描述符寫入及各種命令狀態的處理均通過DSP編程實現。

2019-06-19 15:17:17 1813

1813

不同于以往簡單地使用一個CPLD進行粘合邏輯設計,本文提出了一種基于雙狀態機+Cache,預存預取的主機接口設計結構。在主機接口中設立了一個Cache,降低了CPCI總線與板上DSP和SDRAM芯片

2020-09-15 10:47:00 1019

1019

看,SDRAM 由于其性能價格比的優勢,而被 DSP 開發者所青睞。DSP 與 SDRAM 直接接口是不可能的。 FPGA(現場可編程門陣列)由于其具有使用靈活、執行速度快、開發工具豐富的特點而越來越多地出現在現場電路設計中。本文用 FPGA 作為接口芯片,提供控制

2020-10-25 09:46:18 3328

3328

看,SDRAM 由于其性能價格比的優勢,而被 DSP 開發者所青睞。DSP 與 SDRAM 直接接口是不可能的。 FPGA(現場可編程門陣列)由于其具有使用靈活、執行速度快、開發工具豐富的特點而越來越多地出現在現場電路設計中。本文用 FPGA 作為接口芯片,提供控制

2020-12-22 13:16:00 5

5 針對SDRAM 操作繁瑣的問題,在對SDRAM 存儲器和全頁突發式操作進行研究的基礎上,提出一種簡易SDRAM 控制器的設計方法。該設計方法充分利用全頁式高效率存取的優點,對SDRAM 進行配置、全頁突發式讀寫時,操作方便。在實現sDRAM 的快速批量存儲方面,具有良好的應用價值。

2020-12-18 16:13:18 6

6 的設計方法。結合實際系統,設計給出了使用FPGA實現 SDRAM控制器的硬件接口,在 Altera公司的主流FPGA芯片EPlC6Q240C8上,通過增加流水級數和將輸出觸發器布置在IO單元中,該控制器可達到185MHz的頻率。

2021-01-26 15:30:52 13

13 1.SDRAM使用越來越廣泛。

2.SDRAM具有存儲容量大,速率快的特點。

3.SDRAM對時序要求嚴格,需要不斷刷新保持數據。

.FPGA在電子設計中的廣泛應用,使用十分靈活利用FPGA來設計自己的 SDRAM控制器。

2021-03-05 14:49:00 10

10 FPGA作為ARM的SDRAM使用的LPC3250與FPGA接口程序(華為嵌入式開發工程師拉勾網)-FPGA作為ARM的SDRAM使用的LPC3250與FPGA接口程序,適合感興趣的學習者學習,可以提高自己的能力,大家可以多交流哈

2021-08-04 12:09:30 22

22 實時視頻SDRAM控制器的FPGA設計與實現

2022-12-30 09:21:26 3

3

電子發燒友App

電子發燒友App

評論