數(shù)據(jù)采集系統(tǒng)中,通過微機(jī)COM端口的RS-232串行通訊及通過微機(jī)并行端口的并行通訊具有開發(fā)使用方便的特點(diǎn),前者可與工作于11.0592MHz晶振下的8052單片機(jī)在波特率115200時(shí),實(shí)現(xiàn)10ksps(samples per second)的連續(xù)數(shù)據(jù)采集和傳輸而不丟失數(shù)據(jù),若要達(dá)到更高速率的數(shù)據(jù)采集,可以通過并行口通訊方式實(shí)現(xiàn)。當(dāng)前微機(jī)均可通過配置CMOS,將基地址為 378H的并行口設(shè)置為EPP模式以支持通過數(shù)據(jù)口雙向傳輸通訊,并由芯片硬件自動(dòng)產(chǎn)生握手信號(hào),實(shí)現(xiàn)高速傳輸?shù)哪康摹?/p>

為充分實(shí)現(xiàn)EPP模式的高速特性,外設(shè)應(yīng)當(dāng)及時(shí)響應(yīng)EPP的握手信號(hào),當(dāng)數(shù)據(jù)采集系統(tǒng)工作于非實(shí)時(shí)多任務(wù)的WIN98操作系統(tǒng)環(huán)境下,為實(shí)現(xiàn)數(shù)據(jù)高速、均勻性采樣,還需要在外設(shè)配置必要的數(shù)據(jù)緩沖存儲(chǔ)器。如果數(shù)據(jù)采集速率低于EPP模式數(shù)據(jù)讀入平均速率,就可能實(shí)現(xiàn)數(shù)據(jù)的連貫有效性。有資料說明在 EPP模式,可實(shí)現(xiàn)500kBytes/s以上的傳輸速率,這表明通過EPP模式,可以實(shí)現(xiàn)500ksps的數(shù)據(jù)采集系統(tǒng)。通過對(duì)EPP模式的深入實(shí)驗(yàn)分析,發(fā)現(xiàn)要實(shí)現(xiàn)500ksps,外設(shè)硬件及微機(jī)軟件程序均要采取一些策略:硬件上必須配置FIFO數(shù)據(jù)緩沖存儲(chǔ)器,才能協(xié)調(diào)數(shù)據(jù)采集嚴(yán)格的時(shí)間間隔要求與數(shù)據(jù)傳輸給微機(jī)的非實(shí)時(shí)、非均勻性之間的矛盾;軟件程序方面應(yīng)當(dāng)采取雙字讀的方法,否則EPP模式下僅能實(shí)現(xiàn)250kBytes/s數(shù)據(jù)讀取可行性。

1、 EPP模式讀取速率的實(shí)驗(yàn)分析

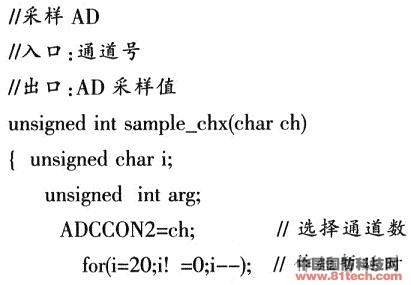

圖1為實(shí)驗(yàn)EPP模式讀取速率的電路,實(shí)驗(yàn)程序?yàn)?/p>

圖1

Delphi結(jié)合內(nèi)嵌匯編語(yǔ)言,涉及EPP讀取的關(guān)鍵代碼如下:

VAR

STARTTIME,STOPTIME,DELAY:INT64;

NUMBERONGWORD;

QUERYPERFORMANCECOUNTER(STARTTIME);

FOR NUMBER:=0 TO 999999 DO

BEGIN

ASM

MOV DX,$37C

IN AL,DX

MOV RESULT,AL

END;

END;

QUERYPERFORMANCECOUNTER(STOPTIME);

DELAY:=STOPTTIME-STARTTIME;

END;

此為循環(huán)1000000次讀取EPP數(shù)據(jù)口程序,循環(huán)僅為方便用計(jì)時(shí)及示波器觀察而設(shè),并在執(zhí)行前后分別讀取系統(tǒng)計(jì)數(shù)值,DELAY值除以1.2后為執(zhí)行花費(fèi)的時(shí)間(單位為微秒),執(zhí)行前先通過對(duì)地址379H的D0位寫入高,使該位為低(注意:對(duì)該位寫入低通常不能達(dá)到使該位變?yōu)榈偷哪康模挥胁扇懭敫卟拍苁乖撐蛔優(yōu)榈停郧宄鼸PP超時(shí)位,當(dāng)A、B點(diǎn)均為低時(shí),可實(shí)現(xiàn)最快的EPP握手,若A為高、B為低時(shí),由于EPP周期開始時(shí)滿足WAIT為低的要求,EPP自動(dòng)在DATASTB處輸出低,但因WAIT沒有出現(xiàn)表示應(yīng)答的高狀態(tài),EPP在延時(shí)10μs后,將DATASTB恢復(fù)為高以結(jié)束該次EPP訪問過程,并置超時(shí)位。稍后因WAIT為低再次開始一次EPP訪問過程,如果B為高,則WAIT為高,不能滿足EPP的開始條件,故DATASTB保持為高,EPP在延時(shí)10μs后結(jié)束該次EPP訪問過程,并置超時(shí)位。在發(fā)生超時(shí)情況下,數(shù)據(jù)仍然可正確讀入(這一特性與所查資料有出入),此結(jié)論可通過對(duì)比循環(huán)前后時(shí)間差來及實(shí)際讀入數(shù)據(jù)值證實(shí)。

圖2

注意程序循環(huán)中并未執(zhí)行清除EPP超時(shí)位的指令,根據(jù)筆者實(shí)驗(yàn),即使已發(fā)生EPP訪問超時(shí),也不影響下一次的EPP讀周期(包括對(duì)37BH的地址讀及對(duì) 37CH的數(shù)據(jù)讀),但超時(shí)對(duì)EPP寫周期有影響,在清除超時(shí)位之前,EPP寫周期無效(因本文不涉及EPP寫周期的內(nèi)容,此處不再展開探討)。在圖2所示意波形中,當(dāng)有正確握手的EPP讀周期執(zhí)行時(shí)間約為1.5μs,此時(shí)間是字節(jié)模式下一次有效EPP訪問所需最短時(shí)間,在這段時(shí)間內(nèi),“IN AL,DX”這一條指令占據(jù)了約90%以上的訪問時(shí)間,驗(yàn)證此點(diǎn)僅需臨時(shí)屏蔽“IN AL,DX”指令,并比較所花費(fèi)的時(shí)間差別即可。1.5μs相當(dāng)于接近700kBytes/s的數(shù)據(jù)讀速率。如果以“IN EAX,DX”替代“IN AL,DX”指令,可以充分利用EPP模式下硬件將4個(gè)8位數(shù)自動(dòng)合并為1個(gè)32位數(shù)的特性,在一次I/O訪問中由硬件自動(dòng)產(chǎn)生4個(gè)DATASTB負(fù)脈沖從而實(shí)現(xiàn)4個(gè)字節(jié)的輸入。因?yàn)橐淮巫止?jié)模式的I/O訪問所費(fèi)時(shí)大約間需要1.5μs,減少這類指令的執(zhí)行次數(shù)有利于實(shí)現(xiàn)更高速的EPP訪問過程,經(jīng)實(shí)驗(yàn)發(fā)現(xiàn)以4字節(jié)方式訪問的EPP過程可以在3.2μs內(nèi)讀取一次,即平均每字節(jié)需0.8μs,相當(dāng)于1.2MBytes/s,此實(shí)驗(yàn)結(jié)果是基于外設(shè)可以連續(xù)不斷的輸送數(shù)據(jù)理想前提,實(shí)際上要實(shí)現(xiàn)有效的數(shù)據(jù)傳輸,可得到的速率要低于該值。

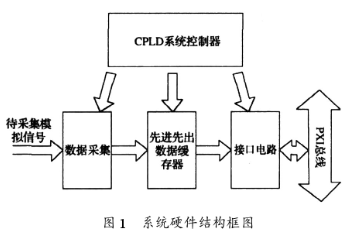

2、 WIN98下高速EPP接口的構(gòu)成

在WIN98環(huán)境下,由于非實(shí)時(shí)多任務(wù)的特性,運(yùn)行于RING3的應(yīng)用程序頻繁被操作系統(tǒng)打斷,這決定了靠軟件無法實(shí)現(xiàn)連續(xù)均勻的數(shù)據(jù)采樣,只有在硬件上配置數(shù)據(jù)緩沖存儲(chǔ)器并及時(shí)傳入微機(jī)以免數(shù)據(jù)緩沖存儲(chǔ)器溢出。只要保證一定深度的數(shù)據(jù)緩沖存儲(chǔ)器,且滿足數(shù)據(jù)傳輸平均速率大于數(shù)據(jù)采樣速率,就能將所采集的數(shù)據(jù)傳入微機(jī)的大容量?jī)?nèi)存,以備處理。在硬件構(gòu)成方面,為以較低代價(jià)獲得大容量的FIFO數(shù)據(jù)緩沖存儲(chǔ)器,采取CPLD器件結(jié)合512KB的SRAM方式,實(shí)現(xiàn),由CPLD器件完成讀寫控制的FIFO特性及EPP模式的應(yīng)答握手信號(hào)。接口結(jié)構(gòu)及CPLD內(nèi)部功能模塊見圖3所示,數(shù)據(jù)在CPLD控制下,以 2μs 的固定速率存入SRAM環(huán)狀連續(xù)增量地址,因?yàn)镋PP模式讀取速率與數(shù)據(jù)采樣的固定速率是異步的,控制邏輯為保證2μs 的固定采樣速率,當(dāng)采樣時(shí)間點(diǎn)到達(dá)時(shí),不論當(dāng)前是否處于EPP應(yīng)答處理期間,優(yōu)先執(zhí)行數(shù)據(jù)采樣,因?yàn)樘幚硎窃谙到y(tǒng)時(shí)鐘脈沖驅(qū)動(dòng)下的硬件行為,僅存在固定的傳輸延時(shí),故兩次采樣間隔是嚴(yán)格保證的。

圖3

EPP模式的讀取平均速率必須高于數(shù)據(jù)采樣速率,一旦FIFO數(shù)據(jù)讀空必須讓微機(jī)正確處理,由前述實(shí)驗(yàn)可知,每次字節(jié)方式I/O執(zhí)行時(shí)間約為1.5μs,如果通過在EPP的狀態(tài)口(379H)的保留位輸入代表FIFO讀空的信號(hào),則每完整讀取均要執(zhí)行兩次I/O指令:EPP數(shù)據(jù)讀及EPP狀態(tài)讀,至少需 3μs完成讀取一個(gè)字節(jié),這也是通常方式能達(dá)到的最快有效讀取速率。當(dāng)采用雙字讀讀及EPP狀態(tài)讀的方式時(shí),需4.8μs完成4個(gè)數(shù)據(jù)字節(jié)讀取,但此方式需要處理的一個(gè)問題:由于雙字方式EPP數(shù)據(jù)讀由硬件自動(dòng)產(chǎn)生4個(gè)EPP數(shù)據(jù)讀周期,當(dāng)其執(zhí)行完畢,執(zhí)行EPP狀態(tài)讀發(fā)現(xiàn)FIFO已空,微機(jī)軟件無法判別在從第幾個(gè)EPP數(shù)據(jù)讀周期開始FIFO為空,從而影響對(duì)數(shù)據(jù)隊(duì)列的正確排序,故CPLD邏輯應(yīng)當(dāng)在FIFO隊(duì)列還有至少4個(gè)未讀數(shù)據(jù)時(shí)必須發(fā)出讀空信號(hào),微機(jī)程序應(yīng)當(dāng)在每次EPP開始前執(zhí)行讀取狀態(tài)口的指令,以決定是否可以開始EPP數(shù)據(jù)讀周期,從上分析可以看出為實(shí)現(xiàn)有效的EPP數(shù)據(jù)讀取,平均每字節(jié)至少需要1.2μs,即可以獲得最快約800kBytes/s的數(shù)據(jù)傳輸速率。因500ksps的數(shù)據(jù)采集設(shè)計(jì)速率僅略低于800kBytes/s的數(shù)據(jù)傳輸速率,考慮WIN98工作環(huán)境,配置大容量的FIFO十分必要,采用大容量SRAM與CPLD器件構(gòu)成FIFO,具有成本較低的優(yōu)點(diǎn),通過使用VHDL的行為描述,經(jīng)CPLD器件開發(fā)軟件的編譯、綜合、仿真、適配、下載,實(shí)現(xiàn)所需要的控制邏輯。根據(jù)設(shè)計(jì),當(dāng)數(shù)據(jù)鎖存輸出的下一個(gè)時(shí)鐘脈沖(即83ns后),WAIT將輸出為高電平,EPP在此時(shí)讀取數(shù)據(jù)口信號(hào),如果不采用外部緩沖驅(qū)動(dòng)器,數(shù)據(jù)上升過程將耗時(shí)80ns,對(duì)EPP數(shù)據(jù)接收可靠性有不容忽視的影響,為減小電纜電容的影響,數(shù)據(jù)輸出使用了74ALS574芯片作緩沖,其高電平輸出能力達(dá)15mA,是ispLSI1032高電平輸出能力的3.5倍,在電纜電容有100pF 時(shí),23ns可達(dá)到3.5V的邏輯高電平,保證數(shù)據(jù)接收可靠性。

仿真波形參見圖4,出于方便,仿真時(shí)鐘設(shè)置為12.5MHz。系統(tǒng)每24個(gè)時(shí)鐘脈沖產(chǎn)生一次數(shù)據(jù)采集,仿真采樣速率521ksps。數(shù)據(jù)由 DIN[7:0]輸入,通過CPLD內(nèi)部數(shù)據(jù)輸入觸發(fā)時(shí)鐘(該時(shí)鐘同相緩沖后形成RAMOE脈沖,持續(xù)寬度為兩個(gè)系統(tǒng)時(shí)鐘)的上升沿鎖存,并控制地址選擇器將寫地址輸出到ABUS上,在RAMOE為高期間,DBUS開放三態(tài)數(shù)據(jù)觸發(fā)器輸出使能,使被鎖存的8位數(shù)據(jù)經(jīng)DBUS輸出,數(shù)據(jù)輸入觸發(fā)時(shí)鐘過后一個(gè)系統(tǒng)時(shí)鐘,RAMWR產(chǎn)生一個(gè)系統(tǒng)時(shí)鐘寬度的負(fù)脈沖,控制SRAM將DBUS上的數(shù)據(jù)寫入,再下一個(gè)系統(tǒng)時(shí)鐘的上升沿,RAMWR變高,RAMOE變低使 SRAM輸出有效,三態(tài)數(shù)據(jù)觸發(fā)器恢復(fù)為高阻狀態(tài),ABUS變?yōu)榇x數(shù)據(jù)地址,完成一次數(shù)據(jù)采集、存儲(chǔ)過程。微機(jī)軟件執(zhí)行EPP數(shù)據(jù)讀前先讀取狀態(tài)口(379H)以判別READ_EN是否有效,當(dāng)READ_EN為高時(shí),可以執(zhí)行EPP數(shù)據(jù)讀周期,CPLD在同步DATASTB_IN的下降沿后,產(chǎn)生一個(gè)寬度的OUTCLK輸出鎖存脈沖,其上升沿將相應(yīng)待讀地址的SRAM數(shù)據(jù)鎖存于外部74ALS574,下降沿使WAIT_OUT上升,形成EPP模式的應(yīng)答握手信號(hào)。WAIT_OUT在DATASTB_IN的上升沿異步復(fù)位以響應(yīng)下一次EPP模式訪問。數(shù)據(jù)寫入優(yōu)先于數(shù)據(jù)讀取,當(dāng)?shù)竭_(dá)固定的采樣間隔點(diǎn)時(shí),CPLD總是推后OUTCLK及WAIT_OUT 的執(zhí)行,待采樣并存儲(chǔ)完畢才繼續(xù)被暫緩的EPP應(yīng)答,在設(shè)計(jì)中,數(shù)據(jù)的采樣及存儲(chǔ)需要兩個(gè)系統(tǒng)時(shí)鐘周期共167ns,遠(yuǎn)低于EPP的超時(shí)參數(shù),故有充分的時(shí)間正確地完成EPP握手。圖4仿真了數(shù)據(jù)讀空狀態(tài),在圖中部,READ_EN信號(hào)存在一個(gè)低電平區(qū)域,此負(fù)脈沖前,根據(jù)RAMWR個(gè)數(shù)可知當(dāng)時(shí)采樣了 11個(gè)數(shù)據(jù),根據(jù)OUTCLK個(gè)數(shù)可知讀取了8個(gè)數(shù),剩下3個(gè)數(shù)不足以提供EPP執(zhí)行雙字讀的操作,如果此時(shí)微機(jī)需要訪問EPP,在其對(duì)狀態(tài)口的讀取中,因得知READ_EN無效而暫緩EPP的執(zhí)行,當(dāng)再次完成一次數(shù)據(jù)采樣后,達(dá)到至少存在4個(gè)未讀數(shù)據(jù)的條件,READ_EN重新變?yōu)橛行В晒┪C(jī)讀取。

為與微機(jī)接口,附加部分其它口線,其中RESET使CPLD全局復(fù)位,74ALS574的OE腳由微機(jī)控制輸出是否為高阻,在程序設(shè)定數(shù)據(jù)端口作為輸入使用前,保持該腳為高電平,使74ALS574輸出為高阻態(tài),雖然使用的是EPP模式的地址選通信號(hào)腳作控制,但程序中并無EPP模式的地址讀寫指令,此腳的變化直接由EPP端口的控制口(37AH)的D3位控制,另外一般D5位為讀寫方向控制,將該位置為高,使數(shù)據(jù)端口作為輸入使用。SYN與RAMWR有固定(芯片編程時(shí)設(shè)定)的相位關(guān)系,作為數(shù)據(jù)采集的同步控制用,當(dāng)選用MAX114芯片且配置為流水線模式(Pipelined Mode)時(shí),MAX114的WR及RD腳共同連接至SYN腳,此信號(hào)波形是與RAMWR同步下降但持續(xù)時(shí)間為500ns的負(fù)脈沖信號(hào),由A/D芯片 MAX114與SRAM及CPLD等器件可構(gòu)成EPP模式下500ksps的連續(xù)數(shù)據(jù)采集接口。

微機(jī)的數(shù)據(jù)接收是個(gè)環(huán)狀循環(huán)體后臺(tái)程序,頻繁對(duì)端口的訪問占據(jù)大量CPU時(shí)間片,為保證對(duì)用戶操作的響應(yīng),應(yīng)采取多線程方式的程序結(jié)構(gòu)。微機(jī)軟件部分采用 Delphi程序設(shè)計(jì)語(yǔ)言,端口訪問使用內(nèi)嵌匯編語(yǔ)言,程序中開辟一塊20-100M字節(jié)或更大的環(huán)型數(shù)據(jù)區(qū),可根據(jù)實(shí)際需要考慮。

責(zé)任編輯:gt

電子發(fā)燒友App

電子發(fā)燒友App

評(píng)論