這種接口電路中,采用單路方式傳輸,每個基色信號采用6位數據,共18位RGB數據,因此,也稱18位或18bit LVDS接口。此,也稱18位或18bit LVDS接口。

2023-03-28 11:46:23 2931

2931 DDR哪幾根線要做差分阻抗,控制在多少ohms也要等長,要控制多少ohms

2014-12-26 10:46:04

請教大家, 怎么樣測量LVDS的具體定義。 在沒有屏規格書,并不知道這5組LVDS那組是什么信號,且哪個是+ -信號, 我們應該怎么去測量, 首先時鐘我們可以測量出來,那么其他4組怎么去區分D0+

2015-10-10 15:23:27

低電壓差分信號傳輸(LVDS)在汽車電子中有哪些應用?

2021-05-13 06:23:22

LVDS接口常常與控制和調節系統一起使用,大數據量必須在電子電路之間或短電纜之間發送。它還能將時鐘信號非常快速地 分配給完整應用中的不同器件,從而使相應器件同步。工業測量應用和控制系統中的模擬前端

2019-08-02 07:16:56

數據傳輸和接口技術。LVDS即低電壓差分信號,這種技術的核心是采用極低的電壓擺幅高速差動傳輸數據,可以實現點對點或一點對多點的連接,具有低功耗、低誤碼率、低串擾和低輻射等特點,其傳輸介質可以是銅質的PCB連線,也

2011-02-23 09:55:17

問一下各位大神們 LVDS接口的數據傳輸速率是怎么計算的?跟頻率的關系是怎樣的?一般用多少頻率傳輸?假如是單路8位(4對差分數據)LVDS接口,知道時鐘速率,數據傳輸速率怎么計算?

2017-01-02 15:31:50

LVDS,即Low Voltage Differential Signaling,是一種低壓差分信號技術接口。它是美國NS公司(美國國家半導體公司)為克服以TTL電平方式傳輸寬帶高碼率數據時功耗

2020-12-29 15:41:14

LVDS,即Low Voltage Differential Signaling,是一種低壓差分信號技術接口。它是美國NS公司(美國國家半導體公司)為克服以TTL電平方式傳輸寬帶高碼率數據時功耗

2019-06-24 05:00:52

LVDS(Low Voltage Differential Signaling)即低壓差分信號傳輸,是一種滿足當今高性能數據傳輸應用的新型技術,LVDS 數據線連接廣泛應用于高速數據信號傳輸,例如

2020-10-30 16:07:34

干擾)。 減小視頻干擾的一種方案是用數字信號取代模擬信號,視頻信號線本身不能產生干擾。已經證明,低壓差分信號(LVDS)能夠為數字視頻傳輸提供最合理的連接。小信號幅度(0.35V)、差分結構使

2019-04-23 07:00:11

LVDS:Low-Voltage Differential Signaling 低電壓差分信號。一種信號傳輸模式,是一種電平標準,LVDS接口又稱RS-644總線接口,是一種數據傳輸和接口

2016-04-15 16:13:33

/MS90C032T和LVDS驅動MS90C031 可以提供高速點對點接口應用,兼容DS90C031.MS90C031是一款低功耗、高數據傳輸率的四通道CMOS差分LVDS信號總線驅動芯片,其支持的數據接收

2022-01-05 11:30:34

本文討論LVDS的各種多媒體特性,其中包括:低電源電壓、低功耗、低輻射、高抗干擾能力以及簡單的電纜布線與終端匹配。低電壓差分信號傳輸(LVDS)已經在眾多應用中得到驗證,LVDS在傳送高數據率信號

2018-12-10 10:23:03

差分放大電路的差模信號是兩個輸入端信號的和,共模信號是兩個輸入端信號的差。這是為什么,能舉個例子嗎?

2023-03-31 14:06:38

想要高質量地傳輸單端模擬信號時可以使用同軸電纜,那么傳輸差分模擬信號時應該使用什么線纜呢?

如上圖所示,我的差分模擬信號采集電路接出兩根同軸線,并在同軸線的末端短接之后,信號的頻譜起伏很大,非常差,是線纜阻抗匹配的問題嗎?

2023-11-13 21:52:50

“浮動”,不僅會給操作人員帶來安全隱患,而且還給儀器的變壓絕緣帶來壓力。由于儀器機箱的電容與電路相連,它還會降低測量精度。差分探頭和隔離器充分允許儀器安全地測量沒有參考接地的浮動電壓或信號。它們特別適合

2017-08-04 09:56:22

本篇主要介紹常用的差分邏輯電平,包括LVDS、xECL、CML、HCSL/LPHCSL、TMDS等。

2021-07-17 19:37:39

的差分系統中,V+ = -V- 和 |I+| = |I-| 可產生平衡的信號。在平衡差分拓撲中,兩根導線緊密耦合在一起,凈接地電流 (IGND-) 等于零。在系統中實施差分信號拓撲有各種優勢,包括更高

2018-09-17 16:34:43

買的AD7760的開發板,上面只提供差分輸入信號接口,而信號發生器只能產生單端信號,難道我自己要去做一個單端轉差分的電路,產生差分信號,那這樣開發板的意義又何在?

2023-12-07 08:04:51

我的AD9446的工作在LVDS模式下,請問對于AD9446(100MHz),LVDS信號線的PCB走線的差分對間等長有沒有要求?(PS:16對差分線,都做等長好復雜)謝謝!

2023-12-18 06:26:51

我使用的是AD9522-2的0、3、6、11這四個端口,其它不用的我都關閉了,而且都是默認設置,即常見的LVDS信號格式設置輸出問題1 在輸出的時候0端口峰峰值變成600mv,只有差分正極有輸出,而

2018-12-05 09:01:41

中,它說:在I / O bank中有差分輸入,如LVDS和LVDS_25是可以接受的除了那些輸出所需的標稱電壓之外的電壓電平標準(LVDS輸出為1.8V,LVDS_25輸出為2.5V)。但是,這些標準

2020-07-17 13:45:49

今天給大俠帶來基于FPGA的LVDS屏幕接口應用,話不多說,上貨。

什么是LVDS,LVDS的全稱是Low-Voltage Differential Signaling ,即低電壓差分信號

2023-06-05 17:31:08

應用的需要。此技術基于ANSI/TIA/EIA-644 LVDS 接口標準。LVDS 技術擁有 330mV 的低壓差分信號 (250mV MIN and 450mV MAX) 和快速過渡時間。 這可以讓

2019-12-11 09:51:59

大家好假設我有一個IO信號Ain verilog設計。我想用它來使用差分信號標準LVDS。我是否必須在我的verilog代碼中使用IOBUFDS?或者有一種更簡單的方法,只需在ucf中將A設置為

2019-01-18 07:03:58

,提高數據的傳輸速度,發展了低壓差分信號LVDS接口技術。LVDS是一種低擺幅的差分信號技術,它使得信號能在差分PCB線對或平衡電纜上以幾百Mbps的速率傳輸,其低壓幅和低電流驅動輸出實現了低噪聲

2019-09-23 09:05:05

Z-turn底部的DIP擴展接口支持LVDS差分輸入輸出嗎?

2015-04-03 14:50:29

。如何量化抖動?查看抖動的最基本方法是用差分探針去測量LVDS信號對,并且上升沿和下降沿上均要觸發,示波器設定為無限持續。這意味著高至低和低至高的躍遷會相互迭加,因此可以測量交越點。交越寬度對應于峰峰

2018-10-30 14:44:43

% UI,假設誤碼率為1×10-12。如何量化抖動?查看抖動的最基本方法是用差分探針去測量LVDS信號對,并且上升沿和下降沿上均要觸發,示波器設定為無限持續。這意味著高至低和低至高的躍遷會相互迭加,因此可以

2018-11-01 10:49:03

什么是差分信號?為什么要用差分信號?差分放大電路的基本結構和作用差分放大電路的應用電路

2021-03-11 08:21:01

折疊式手機面臨哪些問題?一種滿足手機高速圖像數據傳輸的差分串行接口方案

2021-06-01 06:51:04

以太網的接口信號,在PCB走線的時候,差分可以不等長么?如果要等長,誤差是多少?

2023-04-07 17:38:17

的電壓放大器,接下來用一個I-V轉換單元去驅動數字邏輯。使用差分電流傳感電路的一個直接優勢是非常低的電壓擺幅,因而減少電流尖峰和降低EMI。有工作記載已經顯示,電流模式信號受負載電容的影響遠遠小于電壓模式

2019-04-16 07:00:03

Low Voltage Differential Signaling,英文簡稱:LVDS,中文全稱:低壓差分信號技術接口,是一種為了克服TTL電平方式傳輸寬帶高碼率數據時功耗大、EMI電磁干擾等缺點

2020-12-29 13:46:50

想利用單電源差分放大電路放大信號,但是因為同相端的信號幅值低,導致信號差分效果很差。

2020-05-23 19:16:22

單端信號和差分信號會有差異嗎? 他們有何差異,還有在數據傳輸中 為什么使用LVDS或M-LVDS?

2021-03-09 08:40:24

我們在這里使能差分信號,點擊OK生成IP核。AD9684觸發時鐘配置完后,我們配置該芯片的接收器,由于這里AD9684是并行DDR模式的LVDS數據,所以我們需要使用的Xilinx selectIO

2019-12-06 15:33:22

在A40i平臺底層驅動,默認是打開LVDS0接口,因為自研的底板需要用到LVDS1,所以經過與飛凌的唐工不斷溝通,以及去sunxi開源官網查了說明,最終調出了LVDS1接口。在FEX配置文件的關鍵

2022-01-04 06:57:34

)。 減小視頻干擾的一種方案是用數字信號取代模擬信號,視頻信號線本身不能產生干擾。已經證明,低壓差分信號(LVDS)能夠為數字視頻傳輸提供最合理的連接。小信號幅度(0.35V)、差分結構使LVDS傳輸線具有

2019-05-05 09:29:30

嗨,關于Virtex-5與具有LVDS DDR信令的并行高速ADC接口的任何應用說明。我擔心數據偏斜,因此需要靜態和動態相位對齊。最接近的appnote是xapp860,但它不使用并行源,更像

2020-06-19 06:48:36

我需要將輸出信號設置為LVDS,但在Vivado 2016.2中沒有這樣的選項。我正在使用ZedBoard。在Xilinx支持中寫道,只需設置正差分端口就可以自動設置負數。在文檔中,JC1連接器由差

2020-08-07 06:27:32

怎樣去設計一種差分放大電路?怎樣去設計一種反相加法電路?怎樣去設計一種同向加法電路?

2021-09-30 07:21:56

:[Drc 23-20]規則違規(IOSTDTYPE-1)IOStandard類型 -I / O端口B_N是單端但具有LVDS的IOS標準,只能支持差分[Drc 23-20]規則違規

2018-11-01 16:07:18

您好,我需要一個時鐘分配器,輸入74.25的差分或單端,輸出至少2路74.25M的差分LVDS,有哪些芯片通達 到功能,謝謝

2018-12-17 09:33:40

我正在使用Artix 7 fpga。我沒有2.5V IO庫,所以我不能使用LVDS輸出。有沒有人有使用差分HSTL與LVDS接口的經驗? TI建議為接口提供交流耦合終端,有何評論?見附件。

2020-07-30 10:49:04

大家好,我試圖在兩個FPGA(Spartan 6)之間運行邊界掃描互連測試。但是,某些信號有LVDS緩沖器。有沒有辦法使用JTAG提供LVDS信號的激勵/測量響應?AR#6664規定必須將后配置

2019-08-06 11:00:44

接口,因此說到LVDS接口時無特殊說明都是指液晶屏LVDS接口),它們的主要信號成分都是5組差分對,其中1組時鐘CLK,4組DATA(MIPI DSI接口中稱之為lane),它們到底有什么區別,能直接

2016-06-13 20:18:24

目前在做一個電路,關于lvds的信號,請高手解決我選了一個芯片輸出端是差分的lvd信號,我想將這對信號接到另外2個芯片的輸入端,也是lvds信號,可以這樣接2個負載嗎,我知道blvds是可以的,現在是2個負載芯片,是不是lvds也是可以的呢?

2013-04-15 11:19:54

和端口之間的矛盾;而低壓差分信號LVDS(Low-Voltage Differential Signaling)接口作為一種新型的高速串行。低噪聲的數據傳輸接口,廣泛應用于視頻傳輸領域,實現USB

2018-11-22 11:24:30

對處于惡劣環境中的外部接口需要予以電流隔離,以增強安全性、功能性或是抗擾能力。這包括工業測量和控制所用數據采集模塊當中的模擬前端,以及處理節點之間的數字接口。低壓差分信號傳輸(LVDS)是一種在更高

2019-07-23 07:27:54

@我的AD9446的工作在LVDS模式下,請問對于AD9446(100MHz),LVDS信號線的PCB走線的差分對的對間等長有沒有要求?(PS:16對差分線,都做等長好復雜)謝謝!

2018-09-19 09:47:36

請教AD9516的差分參考輸入(ref)和外部時鐘輸入(clk)能否為LVDS?還是必須為TTL?謝謝!

2018-11-05 09:24:01

大家好,我開發了DDR2內存和高速ADC 500Mpbs(2 ADC)到Spartan6 LX25器件。我想知道銀行分配的最佳選擇,因為接口都是高速且需要時鐘定時至關重要。根據MIG的推薦,DDR

2019-07-12 06:30:06

請問一下低電壓差分電路(LVDS)驅動器如何提高工作速度呢?

2023-04-20 16:46:03

DS90UB913Q-Q1和DS90UB914Q-Q1采用STP的方式始終調不通,差分LVDS信號從913上出來后串了0.1uf的電容,然后進入914,這種連接方式是否正確,再LVDS差分線是是否要串上100Ω的電阻?謝謝!

2019-06-19 08:08:08

CPU需要外接lvds接口的屏,方案就是先用芯片將并行的RGB數據轉換成lvds差分對,然后接到LCD上。在轉換芯片的手冊上看到這樣的典型應用原理圖:這讓我產生了疑惑,因為我在網上看到:在PCB設計

2017-11-20 10:21:31

親愛的先生我嘗試在Artix-7 FPGA之間進行像LVDS這樣的DDR差分信號傳輸。但是我不能在Artix-7中使用SelectIO IP。有人能告訴我示例設計嗎?謝謝。

2020-08-18 09:34:09

本文將介紹如何通過一個差分接口來延長串行外設接口 (SPI) 總線,而這可以應用在支持遠程溫度或壓力傳感器的系統的設計。 在SPI應用中,主控器件和受控器件間的距離相對較近,而信號也通常不會

2018-07-02 01:17:42

咨詢超高速比較的是否有差分輸入,LVDS輸出的?關于差分輸入的如何實現過零比較。

2018-08-07 08:13:23

本文將介紹如何通過一個差分接口來延長串行外設接口 (SPI) 總線,而這可以應用在支持遠程溫度或壓力傳感器的系統的設計。 在SPI應用中,主控器件和受控器件間的距離相對較近,而信號也通常不會傳遞到

2019-06-13 05:00:02

最近看了一篇文章,也轉到了我的博里了,講的是LVDS、CML以及PECL接口以及相互之間的對接。個人總結這種差分高速串行接口互聯應該注意下面三個問題:交流耦合或者直流耦合以使信號傳輸;直流偏置以滿足

2015-01-22 14:20:51

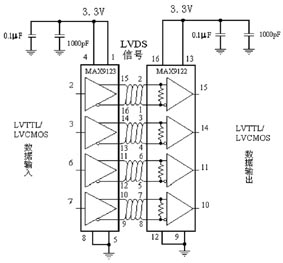

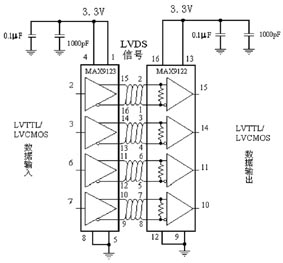

LVDS和TTL板的接口定義及連接原理圖:

TTL板與LVDS 相同

一、接口定義:

1、 LCD MODULE與驅動板之間的信號線接口定義如下:VDS接口又稱RS-644總線接口,是20世紀90年

2008-07-28 16:22:11 1143

1143 介紹了LVDS 接口的原理和優點,接口機的硬件組成以及在設計LVDS 接口時需注意的事項。關鍵詞 LVDS;數據傳輸;時序

當聲吶在海洋中執行任務時,前置預處理機設備接收

2010-09-22 08:27:26 67

67 lvds接口標準:

LVDS接口是LCD Panel通用的接口標準,以8-bit Panel為例,包括5組傳輸線,其中4組是數據線,代表Tx0+/Tx0-... Tx3+/Tx3-。還有一組是時鐘信號,代表TxC+/TxC-。相應的在Pan

2008-07-01 13:51:09 30818

30818

lvds接口定義

LVDS接口又稱RS-644總線接口,是20世紀90年代才出現的一種數據傳輸和接口技術。

2008-07-01 13:55:46 16326

16326 什么是lvds信號

LVDS:Low Voltage Differential Signaling,低電壓差分信號。LVDS傳輸支持速率一般在155Mbps(大約為77MHZ)以上。LVDS是一種低擺幅的差分信號

2008-10-16 13:49:11 7844

7844 LVDS信號電平特性

LVDS物理接口使用1.2V偏置電壓作為基準,提供大約400mV擺幅。LVDS驅動器由一個驅動差分線對的電流源組成(通常電

2008-10-16 13:50:25 16632

16632 LVDS接口電路及設計

LVDS接口又稱RS-644總線接口,是20世紀90年代才出現的一種數據傳輸和接口技術。LVDS即低電壓差分信號,這種技術的核心是采用極低的電壓

2009-06-16 11:19:26 5057

5057

隨著數字電路數據量的提高,數據的傳輸速率也越來越快,LVDS(低壓差分信號)標準越來越多的應用在FPGA和ASIC器 件中。文章對LVDS信號的特點進行了分析,說明了PCB設計中差分走線的注意事項并結合實際應用設計了一塊LVDS接口板。 關鍵詞: LVDS; PCB設計;接口;阻抗

2011-02-23 09:54:03 340

340 LVDS接口又稱RS-644總線接口,是20世紀90年代才出現的一種數據傳輸和接口技術。LVDS即低電壓差分信號,這種技術的核心是采用極低的電壓擺幅高速差動傳輸數據,可以實現點對點或一點

2011-06-02 09:30:41 10793

10793

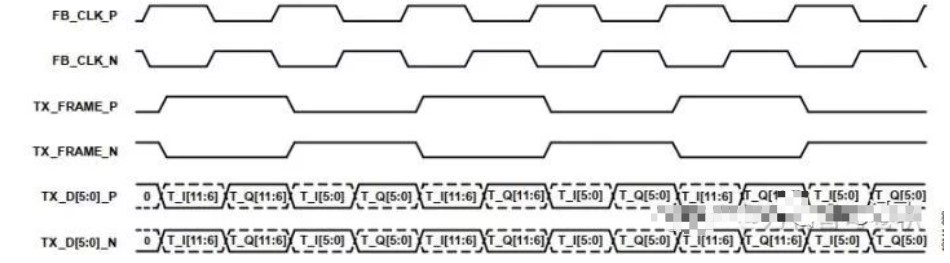

介紹了LVDS技術的原理,對LVDS接口在高速數據傳輸系統中的應用做了簡要的分析,著重介紹了基于FPGA的LVDS_TX模塊的應用,并通過其在DAC系統中的應用實驗進一步說明了LVDS接口的優點。

2012-01-11 10:46:04 99

99 LVDS,即Low Voltage Differential Signaling,是一種低壓差分信號技術接口。它是美國NS公司(美國國家半導體公司)為克服以TTL電平方式傳輸寬帶高碼率數據時功耗大、EMI電磁干擾大等缺點而研

2012-07-19 16:01:53 5328

5328

LVDS顯示屏接口LVDS顯示屏接口LVDS顯示屏接口LVDS顯示屏接口

2016-01-15 16:31:39 0

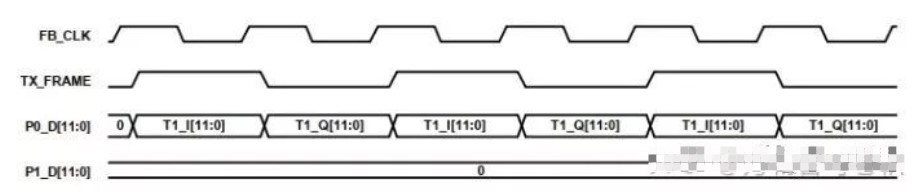

0 wp02-將凌力爾特公司的DDR LVDS ADC與Altera Stratix IV FPGA接口

2021-05-23 11:13:28 1

1 這種接口電路中,采用單路方式傳輸,每個基色信號采用6位數據,共18位RGB數據,因此,也稱18位或18bit LVDS接口。此,也稱18位或18bit LVDS接口。

2023-06-02 16:01:53 5462

5462

,用于高速數據傳輸。它的優勢包括高速傳輸能力、低功耗、抗干擾能力強、傳輸距離遠等。 二、LVDS信號正常的判斷方法 1. LVDS通信線路測試 LVDS通信線路測試主要用來判斷LVDS通信電纜、連接器、接口是否良好,需要用到萬用表、信號發生器、示波器等測試設備。測試

2023-10-18 15:38:13 2929

2929 什么叫做LVDS信號?請問TTL信號與LVDS信號有什么區別? LVDS信號 LVDS(Low Voltage Differential Signaling)又稱低壓差分信號傳輸技術,是一種采用

2023-10-18 15:38:18 1265

1265 雙路LVDS信號和單路的時鐘頻率有什么關系?是一個時鐘內傳輸兩個像素的數據嗎? 雙路LVDS信號是一種在高速數據傳輸上應用廣泛的接口,它利用微小的電壓擺動來傳輸數據。在雙路LVDS信號中,數據被分成

2023-10-18 15:38:22 972

972 LVDS(Low Voltage Differential Signaling)接口是一種低電壓差分信號傳輸LVDS(Low Voltage Differential Signaling)接口是一種

2024-01-18 11:20:09 314

314

電子發燒友App

電子發燒友App

評論