在FPGA調試過程中,除了邏輯代碼本身的質量之外,F(xiàn)PGA板子上PCB走線、接插件質量等因素的影響也非常重要。在剛上板調試不順利的時候,不妨拿示波器看一下信號的質量,比如時鐘信號的質量、差分信號

2020-11-20 12:11:30 4454

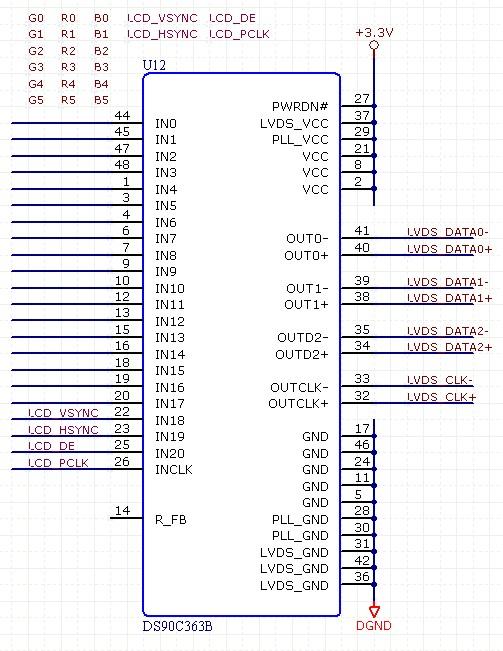

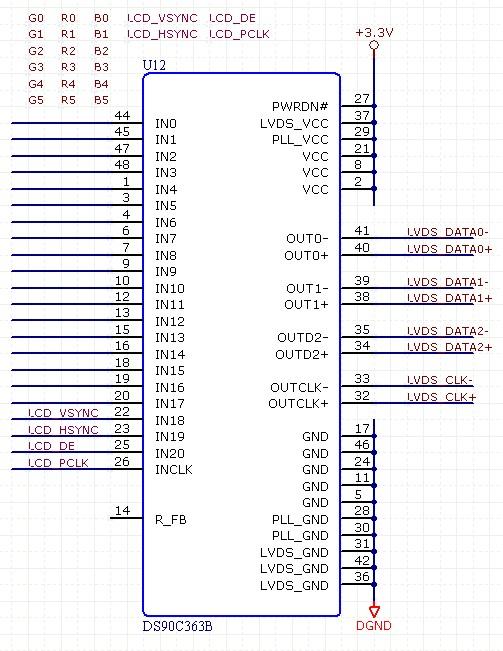

4454 這種接口電路中,采用單路方式傳輸,每個基色信號采用6位數(shù)據,共18位RGB數(shù)據,因此,也稱18位或18bit LVDS接口。此,也稱18位或18bit LVDS接口。

2023-03-28 11:46:23 2931

2931 LVDS是一種低擺幅的差分信號技術,它使得信號能在差分PCB線對或平衡電纜上以幾百Mbps的速率傳輸,其低壓幅和低電流驅動輸出實現(xiàn)了低噪聲和低功耗。

2023-10-02 16:44:00 589

589

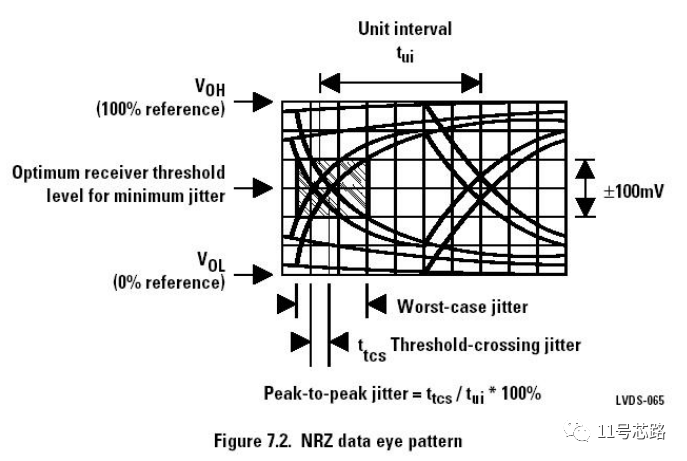

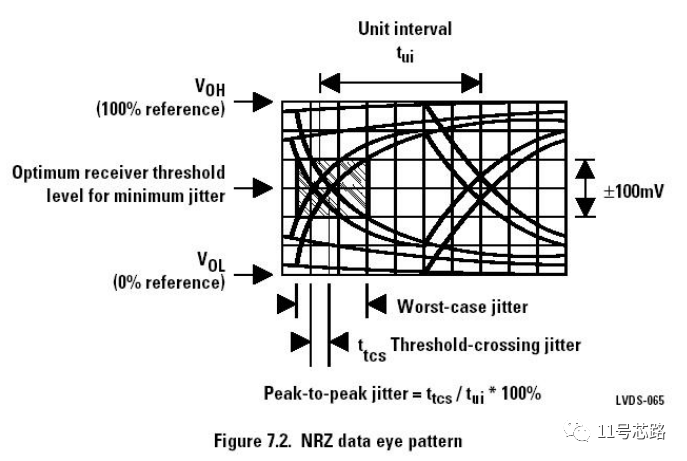

示波器屏幕上看到的圖形就稱為眼圖。示波器一般測量的信號是一些位或某一段時間的波形,更多的反映的是細節(jié)信息,而眼圖則反映的是鏈路上傳輸?shù)乃袛?shù)字信號的整體特征。觀察眼圖的方法是:用一個示波器跨接在接收

2020-03-02 18:19:16

最近接手一個LVDS信號轉接板制作的任務,本人對于設計高頻layout一點都不懂,完全是小白的概念,查了些資料了解LVDS要設計特性阻抗,知道了LVDS特性阻抗為100Ω,首先說明一下情況,信號

2018-12-16 16:55:27

本帖最后由 eehome 于 *** 編輯

我的單色屏,視頻信號是LVDS現(xiàn)在我換成了彩屏,彩屏僅支持AV輸入我想在彩屏上顯示以前單色屏的內容所以就得把LVDS信號轉為AV信號求大神幫忙啊!!!

2012-09-23 13:44:52

請教大家, 怎么樣測量LVDS的具體定義。 在沒有屏規(guī)格書,并不知道這5組LVDS那組是什么信號,且哪個是+ -信號, 我們應該怎么去測量, 首先時鐘我們可以測量出來,那么其他4組怎么去區(qū)分D0+

2015-10-10 15:23:27

你好,我一直試圖在論壇中找到對我的懷疑的答案,但我找不到確切的答案。我們目前正在為VC709開發(fā)套件設計FMC擴展板,我有幾個問題:1.我們需要使用差分(LVDS)和單端信號(3.3V)。兩種信號

2019-09-20 11:56:39

用什么方式能夠做雙路LVDS信號的切換,損耗最小

2023-05-15 16:49:33

LVDS:Low-Voltage Differential Signaling 低電壓差分信號。一種信號傳輸模式,是一種電平標準,LVDS接口又稱RS-644總線接口,是一種數(shù)據傳輸和接口

2016-04-15 16:13:33

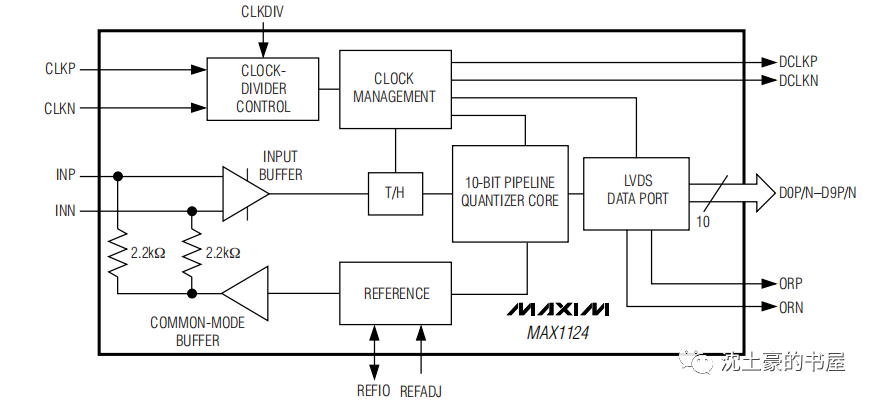

LVDS接口常常與控制和調節(jié)系統(tǒng)一起使用,大數(shù)據量必須在電子電路之間或短電纜之間發(fā)送。它還能將時鐘信號非常快速地 分配給完整應用中的不同器件,從而使相應器件同步。工業(yè)測量應用和控制系統(tǒng)中的模擬前端

2019-08-02 07:16:56

看到的圖形就稱為眼圖。示波器一般測量的信號是一些位或某一段時間的波形,更多的反映的是細節(jié)信息,而眼圖則反映的是鏈路上傳輸?shù)乃袛?shù)字信號的整體特征。如果示波器的整個顯示屏幕寬度為100ns,則表示在

2020-09-25 11:54:26

,但是在線徑粗細發(fā)生變化的時候,會發(fā)生一些反射的現(xiàn)象。拐角方式對于線的粗細變化情況,直角是最差的,45度角好一些,圓角是最好的。但是圓角對PCB設計來講處理比較麻煩,所以一般是看信號的敏感程度來定,一

2018-09-18 15:55:57

老師給的一些應用實例

2013-08-13 10:04:05

最近用到的一些東西,分享一下!

2014-06-15 11:32:28

眼圖及眼圖在信號測試中的運用

2015-05-21 23:42:52

本文介紹了什么是眼圖,眼圖是如何構建的,觸發(fā)是生成眼圖的一個共同方法。然后描述了使用不同的方式切割眼圖,可以獲得更多深入的信息。同時還討論了一些發(fā)射機、傳輸鏈路和接收機測試的基本方法。本文的目的是為了工程師掌握眼圖這個新領域的基本概念。

2019-07-12 07:30:00

眼圖測試測試項目: >消光比>眼交叉比>信號上升時間與下降時間>Q因子(Q Factor)>平均功率>抖動測試環(huán)境: 在實時示波器中通常使用連續(xù)比特位的眼圖生成

2019-10-10 14:36:04

華為編寫的介紹眼圖基本知識的資料,介紹如何從眼圖的中看出一些量化的數(shù)據如信號的上升、下降時間、交叉點位置、消光比、Q因子、信噪比、抖動等,以及如何從各個方面來衡量一個眼圖的優(yōu)劣。

2012-08-02 15:14:23

本帖最后由 sdf1994 于 2014-10-25 23:02 編輯

這是關于Arduino的一些教程

2014-10-25 22:55:23

各位大神,小弟這邊先謝過了,真的很急!目前我需要使用FPGA技術來處理一款1對時鐘LVDS信號和8對數(shù)據LVDS信號攝像頭模組,我這邊只能對并口信號和MIPI信號輸出的攝像頭模組進行測試調焦,對于LVDS信號的模組沒有相關技術,請大神幫忙啊!!!非常感謝!!!可付報酬!!!

2014-07-17 16:40:58

親愛的Xilinx人,我有一些簡單的問題要問。我正在使用Virtex 6 SX475T進行PCB設計。我正在考慮添加一個擴展端口,它有2對CML和6對LVDS信號。從用戶指南,我認為一個GTX銀行

2020-06-13 08:38:27

:Android 12-1.0.0

內核:5.10.72

另外,我們并沒有直接從SOC端(通過USB-HUB)連接到USB主機連接器,那么IMX8是否支持 眼圖測試的一致性模式?

我找到了一些關于 USB 眼圖的文檔,但無法下載,如果有人能提供正確的文檔鏈接,我將不勝感激。

2023-05-04 06:00:08

一些資料,希望可以幫到你們

2016-06-24 23:50:45

SI工程師給出的約束規(guī)則來完成布局布線的,這些也就是俗稱的“拉線工”。他們重復而機械的完成一塊塊PCB設計,一段時間設計后,他們中的一些或許已經有了這樣的一些經驗:哪些要做等長,哪些要走粗、哪些要平行

2016-12-20 17:34:18

以下是USB底層信號的一些定義及時序圖,雖然很簡潔,但能理解后,對后續(xù)的USB學習是很有幫助的,特推薦給大家!BTW,本月(4月20號周六)在深圳有一場很接地氣、很容易入門的USB線下、小型技術交流

2019-04-08 16:30:26

本帖最后由 912293097 于 2012-10-25 21:58 編輯

分享一些avr的一些資料

2012-10-25 21:54:52

labview的一些文章

2012-05-26 21:43:40

labview的一些文章

2012-09-24 17:44:36

,各種電子產品的PCB設計,積累了非常多的一些經驗,對于一些電子工程師來說,可以起到一個借鑒和參考的作用,也希望下面的一些經驗或者技巧能夠幫助電子工程師在產品的設計中應對PCB設計面臨的各種挑戰(zhàn)

2012-04-27 16:01:01

的周期同步,這時示波器屏幕上看到的圖形就稱為眼圖。示波器一般測量的信號是一些位或某一段時間的波形,更多的反映的是細節(jié)信息,而眼圖則反映的是鏈路上傳輸?shù)乃袛?shù)字信號的整體特征。 3、眼圖和實時波形的區(qū)別

2019-07-12 05:00:00

作為儀器廠商目前唯一支持的。 8、快速眼圖的測量 (一鍵式眼圖測量) 當我們需要測量眼圖時,需要先進行一系列的設置后才能形成波形的眼圖,比如波形的大小調整、信號速率的設定以及閾值的設定等。對于一些

2019-07-12 05:30:00

值抖動或截至目前所測得的時間間隔誤差 (TIE)(比較圖3所示的眼圖和直方圖)。有一些抖動是隨機圖3. ADN4651的眼圖和直方圖相比之下,確定性抖動(DJ)的為了完整地估算特定誤碼率下的總抖動

2018-10-30 14:44:43

純當作一個開關器件來看,會出現(xiàn)許多問題。在這里總一下問題和對出現(xiàn)問題的一些原因做一些分析。個人知識有限,很多地方思慮難免有所不足,希望能夠與網上各位一起學習交流。目前我們一般將H橋驅動當作電機或步進

2021-09-13 08:14:12

可靠地采集數(shù)據。2. 常用術語在數(shù)字電路系統(tǒng)中,定時是最重要的因素之一。 數(shù)字通信的可靠性和精確度均取決于定時的質量。 然而,在實際應用中,任何事物都不是理想的。 以下是一些可以幫助您理解特定數(shù)字信號

2019-06-12 08:00:00

安川伺服調試的一些經驗在查找慣量比的過程中看到的,這是伺服電機的驅動過程中發(fā)生的問題,首先應當匹配慣量,伺服電機應當考慮剛性,還有速度,速度高,慣量還會大。再生電阻還是不知道怎么配置。 安川伺服調試的一些經驗: 1、 安川伺服在低剛性(1~4)負載應用時,慣量比顯得非常重要,以同步帶結構而論

2021-09-07 08:05:06

嗨, 我計劃在我的設計中使用SERDES(LVDS)作為背板。我已經瀏覽了virtex5用戶指南中的advnced IO部分,并看過ISERDES_NODELAY和OSERDES宏。我已經看到了一些

2020-07-13 15:54:49

本人最近在做一個項目,從核心板出單8路的LVDS信號,意圖轉成VGA信號,直接輸出到顯示器上。請問大家有沒有什么好的方案提供。謝謝各位了,好心人總會有好回報的。LVDS頻率是50HZ,最高支持1280*800.

2017-07-10 11:37:32

BANK VCCIO為2.5V,下載后,分別測出兩個差分引腳的電壓波形,奇怪的是兩個引腳的電平不滿足LVDS的電平范圍(1.0v-1.4v),而且兩個信號的VPP幅值還不一樣,一個是2.95一個是2.0

2018-04-03 18:39:33

1、rk3288點亮lvds屏幕之前有點亮過23.6寸的雙8液晶屏,這次手上剛好有塊10.1寸屏幕,記錄一下過程。屏幕的型號。修改firefly-rk3288.dts 設備樹信息一個通道,16.7M=2^24,即r,g,b各8位信號寬度原作者:風見暗含

2022-05-11 14:16:02

1、怎樣學習使用Altium Designer、Proteus、Keil等與電子相關的一些軟件?是看指導書好,還是看視頻教程好?有沒有必要全面熟悉所有功能的實現(xiàn)方法,還是熟悉常用的一些功能就好?2

2013-08-28 12:36:25

芯片的,不知有無錯誤?如下圖:3. 想問下工程師是否可以給我們一些有益的建議呢,非常感謝! 請工程師指點,非常感謝!

2019-05-22 07:26:16

分享一些資料

2019-03-13 17:31:05

fofa,鐘馗之眼,shodan等等一系列的公網設備搜索引擎,其中fofa和shodan使用的最多,本文就來整理一些shodan的搜索語法Shodan:www.shodan.ioPs:均來自互聯(lián)網

2021-07-12 06:33:01

分享一些實例,免得大家不好找

2014-07-15 15:32:37

的內部驅動器和接收器是否足夠?另外,我應該使用一些電線作為從一個電路板到另一個電路板的接地,還是沒有必要,因為lvds信號是相互參照的?最后,在設計中我是否應該采取任何其他預防措施(除了通常的阻抗匹配

2019-06-24 15:44:23

的協(xié)議會定義特殊的碼型(常見的碼型如8B/10B編碼中的K28.5)用于字對齊處理。另一些帶源同步時鐘的LVDS接口,通常會利用低頻的源同步時鐘來攜帶字對齊信息,用于接收端的正確恢復。FPGA對上述兩種

2019-07-29 07:03:50

`基于labview的信號采集于分析系統(tǒng)的一些資料`

2015-03-23 16:33:36

你好,我正在嘗試生成LVDS信號。在代碼中我使用PS的1Mhz時鐘。但是有一些時間問題。我不知道如何解決它。體系結構TDC_EvaluationSignal的行為是signal

2020-05-07 09:31:42

大家好我正在使用Xilinx Spartan 3e芯片。我可以在嚴格的輸入信號或嚴格的輸出上使用LVDS。但有沒有人知道如何編碼verilog在雙向信號上使用LVDS標準?非常感謝你花時間陪伴。以上

2019-01-08 10:17:47

你好,現(xiàn)在我正在考慮如何通過I2S接收一些信號。即使這些信號不是聽覺信號,但它們都與I2S接口通信。但是時鐘速率大約為40.96Mbps。我只想通過HS U***接口接收/存儲/保存/轉儲到PC上

2019-08-14 07:05:51

本片文章包含了定時器的一些使用,包括下面五個實驗:1.測量信號的脈寬2.PWM 輸出3.PWM 互補輸出4.PWM 輸入5.電容按鍵檢測

2021-08-16 07:00:43

嗨,我試圖產生一些隨機SPI信號在各種SPI時鐘速率。我使用的PIC是PIC16LF1618。當MCU運行在16 MHz時,SPI模塊可以在4 MHz產生時鐘。然而,當使用鎖相環(huán)(X4)以

2019-08-27 13:09:50

可靠地采集數(shù)據。2. 常用術語在數(shù)字電路系統(tǒng)中,定時是最重要的因素之一。 數(shù)字通信的可靠性和精確度均取決于定時的質量。 然而,在實際應用中,任何事物都不是理想的。 以下是一些可以幫助您理解特定數(shù)字信號

2016-01-18 15:31:09

小弟目前大一學生準備接觸ARM在論壇里潛水幾天 很多事情不知道想請教下各位學長們。小弟目前會C語言, 應該屬于入門級別的C語言還有PCB繪制用的DXP, 還掌握了51單片機的一些技巧在以及VB

2015-06-22 20:06:10

是否可以在放置后手動路由一些關鍵信號,但在路由之前?我有一些非常關鍵的信號,我想用最好的路徑進行路由,但是如果我使用已實現(xiàn)的設計,我必須解決現(xiàn)有的路由(或者手動取消路由它們!)。看起來如果我可以加載

2018-11-05 11:41:09

此前一個項目。它有一些MAP問題。如下:位置:1333- 具有輸入/輸出編程的IOB鎖定到不支持此類值的Bank 1標準:名稱= LVDS_25,VREF = NR,VCCO = 2.50,TERM

2018-10-15 11:53:42

某些比特。? 眼圖很好,可以說明信號品質沒有問題嗎?當然可以。代表整體。4、眼圖的衡量指標在對于一個眼圖進行好和壞的評估時,通常都有一些常見的衡量指標,比如眼高,眼寬,抖動,占空比等,如上圖。通過對眼

2018-09-14 21:12:08

設計人員應該同等重視的問題。今天整理本人接觸的電源完整性PI的一些原理,從不的角度去看PI,會有不同的理解,下面開始嘍!!!提到互連的電源設計,可能首先想到的電源分配網絡(Power

2021-11-15 07:20:09

發(fā)生變化的時候,會發(fā)生一些反射的現(xiàn)象。拐角方式對于線的粗細變化情況,直角是最差的,45度角好一些,圓角是最好的。但是圓角對PCB設計來講處理比較麻煩,所以一般是看信號的敏感程度來定,一般的信號用45度角

2017-03-27 13:32:46

發(fā)生變化的時候,會發(fā)生一些反射的現(xiàn)象。拐角方式對于線的粗細變化情況,直角是最差的,45度角好一些,圓角是最好的。但是圓角對PCB設計來講處理比較麻煩,所以一般是看信號的敏感程度來定,一般的信號用45度角

2016-11-04 10:42:42

請教一些關于CC2541F256這顆芯片的一些問題。 1、該芯片是使用32M的外部晶振作為時鐘倍頻到2.4G作為藍牙信號發(fā)射出去,我們的整機做了500套發(fā)現(xiàn)所有整機頻率有偏移,落在-20KHZ到

2021-08-02 11:44:05

各位專家好,我需要使用C6678處理信號,該芯片有提供數(shù)據處理的一些函數(shù)那么,類似FFT變換,巴特沃茲濾波器等。有沒有文檔介紹這些函數(shù)用法以及需要包含哪些庫,如果有在哪里下載?麻煩提供下,非常感謝。

2018-07-24 07:24:19

你好,有人以前在PSoC 5LP上使用LVDS嗎?或者有人做了一些可以用在PSoC 5LP上實現(xiàn)LVDS的東西嗎?至少有一些建議是很好的。謝謝大家, 以上來自于百度翻譯 以下為原文Hello

2019-07-29 14:48:38

之間的單端I / O.我可以將一些差分信號對配置為單端信號嗎?或者它們是硬編碼的。我還注意到一些連接到FPGA(U1)的信號看起來不像差分信號對。它們是我可以自由使用的單端唱法嗎?例如,在表

2019-09-30 06:11:58

如何對LVDS接口屏的頻率進行設置呢?如何對LVDS接口屏的時序參數(shù)進行設置呢?

2022-03-04 07:34:04

考慮。下面我根據自己平時維修的一些經驗與朋友們談談我對替換電容的一些看法。在強電電路中更換電容時要注意的事項

2021-11-16 07:47:06

步一些技術的發(fā)展方向和趨勢。還有是許多功能實現(xiàn)的算法本身,是非常值得研究和學習的。 因此關注本攔的朋友,希望您的目的首先是為自己做些技術儲備,如果想馬上應用在產品設計中,可能不會非常順利的。 下面做

2012-11-16 15:34:58

為什么眼圖里會有兩個波信號, 如果是傳輸一個信號的話不是因該只有0或者1嗎?謝謝指教 ;)

2011-08-10 14:00:52

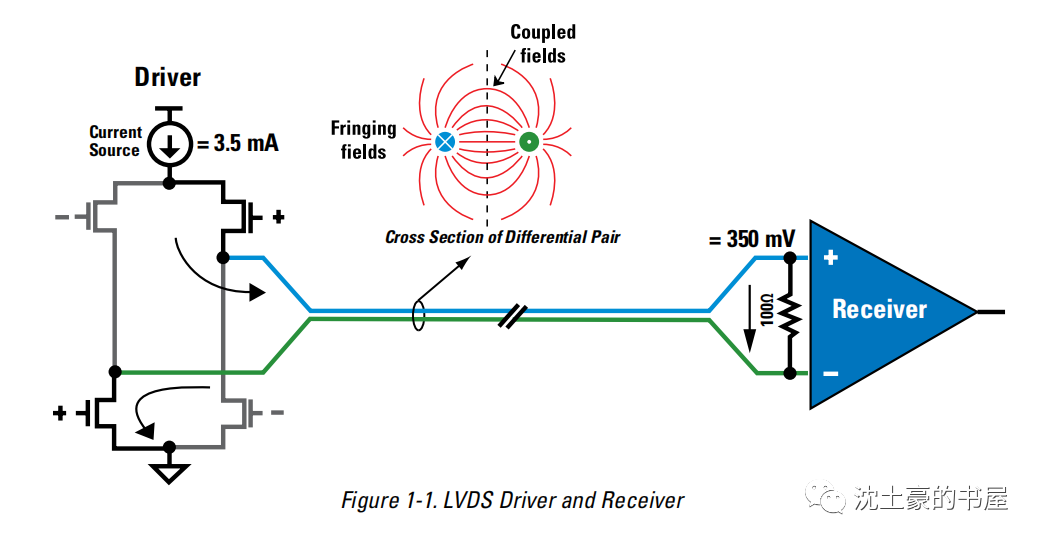

1 LVDS信號介紹LVDS:Low Voltage Differential Signaling,低電壓差分信號。LVDS傳輸支持速率一般在155Mbps(大約為77MHZ)以上。LVDS是一種低擺幅的差分信號技術,它使得信號能在差

2008-10-16 13:44:45 153

153 基于低電壓差分信號(LVDS)的高速信號傳輸

2010-12-17 17:21:46 40

40 什么是lvds信號

LVDS:Low Voltage Differential Signaling,低電壓差分信號。LVDS傳輸支持速率一般在155Mbps(大約為77MHZ)以上。LVDS是一種低擺幅的差分信號

2008-10-16 13:49:11 7844

7844 LVDS信號電平特性

LVDS物理接口使用1.2V偏置電壓作為基準,提供大約400mV擺幅。LVDS驅動器由一個驅動差分線對的電流源組成(通常電

2008-10-16 13:50:25 16632

16632 LVDS差分信號抗噪特性

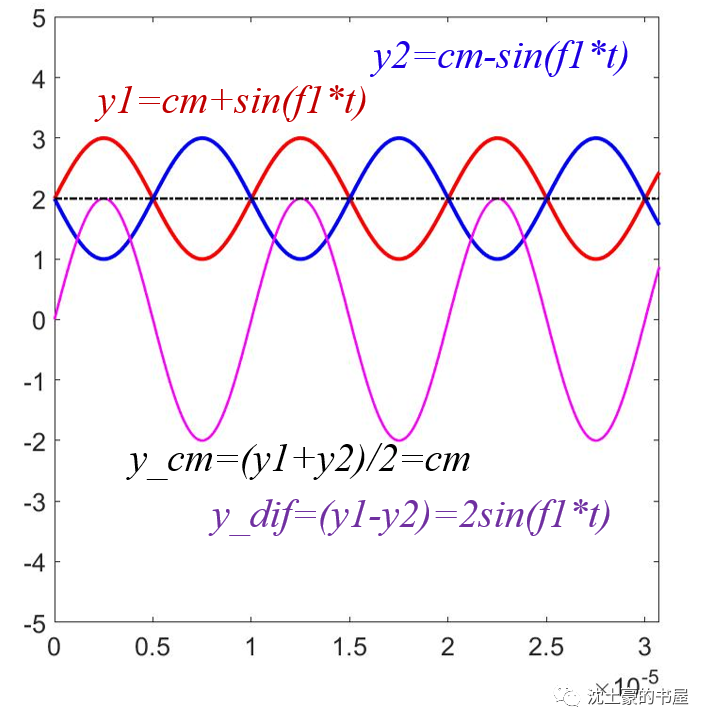

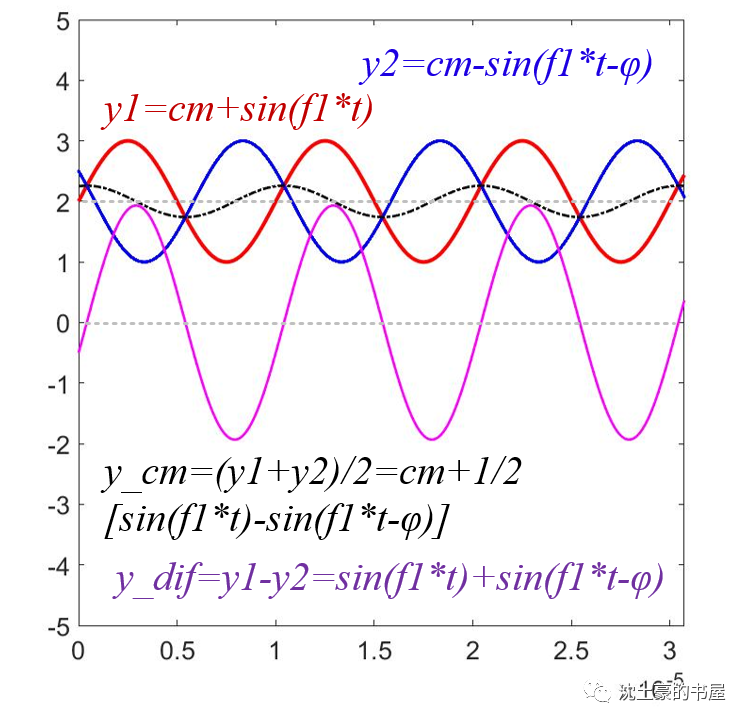

從差分信號傳輸線路上可以看出,若是理想狀況,線路沒有干擾時,在發(fā)送側,可以形象理解為:

2008-10-16 13:53:16 1507

1507 LVDS信號的PCB設計

1 LVDS信號的工作原理和特點 對于高速電路,尤其是高速數(shù)據總線,常用的器件一般有:ECL、BTL、GTL和GTL+等。這些器件的工藝成

2008-10-16 13:57:52 3359

3359 摘要:ANSI EIA/TIA-644標準定義的低電壓差分信號(LVDS)非常適合包括時鐘分配、點對點以及多點之間的信號傳輸。本文描述了使用LVDS將高速通訊信號分配到多個目的端的方法。

2009-04-24 16:05:19 1273

1273

摘要:ANSI EIA/TIA-644標準定義的低電壓差分信號(LVDS)非常適合包括時鐘分配、點對點以及多點之間的信號傳輸。本文描述了使用LVDS將高速通訊信號分配到多個目的端的方法。

2009-05-01 11:14:27 1655

1655

本文描述TI 的客戶在不用 LVDS (低壓差分信號傳輸)驅動器時,如何采用LVDS 接收器于其他驅動器配合解決一些簡單的問題。

2011-07-18 15:21:36 30

30 文中以基于FPGA設計的高速信號下載器為例,從LVDS的PCB設計,約束設置和信號完整性仿真等多方面研究LVDS信號的實現(xiàn)。

2012-04-20 10:37:02 58

58 低電壓差分信號(LVDS)是一種高速點到點應用通信標準。多點LVDS (M-LVDS)則是一種面向多點應用的類似標準。LVDS和M-LVDS均使用差分信號,通過這種雙線式通信方法,接收器將根據兩個互補

2013-08-22 16:09:00 92

92 它差分信號標準類似,LVDS由于消除了磁場,因而比單端信號輻射的噪聲要低得多。同時外來噪聲作為共模信號耦合到兩根線上(即兩根線上的噪聲電平相同),因此它的抗噪聲能力比單端信號要強得多。另外,LVDS驅動器的輸出采用電流驅動方式(圖1),與其它差分信號標準中的電壓

2017-04-06 16:11:31 6

6 GM8827C實現(xiàn)以7:1的壓縮比將27位CMOS/TTL信號(RGB 8位和HSYNC、VSYNC、 DE)換成串行 LVDS 輸出數(shù)據流。輸入時鐘經內部鎖相后,同頻率輸出,同時轉換為 LVDS

2021-11-30 21:06:05 8

8 ANSI EIA/TIA-644 低壓差分信號 (LVDS) 標準比更傳統(tǒng)的 ECL、PECL 和 CML 標準提供更低的功率和更低的噪聲發(fā)射,用于高速信號分配。本應用筆記比較了這些通信標準的一些特性,并討論了LVDS標準的一些優(yōu)點。

2023-03-29 11:05:07 662

662

本應用筆記討論了EIA/TIA-644低壓差分信號(LVDS)標準在3G移動通信中的應用。LVDS具有低功耗和低輻射特性,非常適合WCDMA、EDGE和cdma2000?基站中的高速時鐘和信號分配。提供MAX9205串行器、MAX9206解串器、MAX9150多端口中繼器和MAX9152交叉點開關。

2023-03-29 11:14:33 750

750

LVDS (Low Voltage Differential Signaling)是一種小振幅差分信號技術,它使用非常低的幅度信號 (250mV~450mv)通過一對平行的PCB走線或平衡電纜傳輸數(shù)據是一種專業(yè)的低電壓差分信號

2023-04-06 09:46:43 1286

1286 LVDS發(fā)送芯片的輸入信號來自主控芯片,輸入信號包含RGB數(shù)據信號、時鐘信號和控制信號三大類。

2023-10-17 17:28:13 583

583

LVDS傳輸?shù)氖鞘裁?b class="flag-6" style="color: red">信號?判斷LVDS信號正常的方法 一、LVDS傳輸?shù)氖鞘裁?b class="flag-6" style="color: red">信號? LVDS是一種低電壓差分信號,有兩種電壓狀態(tài),即高電平和低電平,它類似于RS485協(xié)議。LVDS信號作為一種數(shù)字信號

2023-10-18 15:38:13 2929

2929 什么是LVDS和RSDS圖象信號?幫忙解釋一下LVDS和RSDS這兩種傳輸協(xié)議吧? LVDS和RSDS都是用于傳輸數(shù)字圖像信號的串行通信協(xié)議。它們都是由電子工業(yè)界制定的標準,旨在提高圖像傳輸速度

2023-10-18 15:38:16 1232

1232 什么叫做LVDS信號?請問TTL信號與LVDS信號有什么區(qū)別? LVDS信號 LVDS(Low Voltage Differential Signaling)又稱低壓差分信號傳輸技術,是一種采用

2023-10-18 15:38:18 1265

1265 LVDS中的時鐘脈沖信號是干什么的? LVDS(Low Voltage Differential Signaling)中的時鐘脈沖信號(Clock)是用于同步數(shù)據傳輸?shù)模钦麄€LVDS接口的重要

2023-10-18 15:38:20 662

662 兩個獨立的信號流傳輸。這兩個信號流被稱為“正”和“反”信號,每個信號流包含一個有效數(shù)據線和一個共享地線。雙路LVDS接口在圖形和視頻傳輸中得到廣泛應用,通常用于解決一些高速傳輸需要,比如在某些具有高像素密度的液晶顯示器(LCD)中

2023-10-18 15:38:22 972

972

電子發(fā)燒友App

電子發(fā)燒友App

評論