2022 年 4?月 14?日,中國北京訊?- 全球半導體解決方案供應商瑞薩電子(TSE:6723)今日宣布,率先推出符合PCIe Gen6嚴格標準的時鐘緩沖器和多路復用器。作為業(yè)內(nèi)先進的時鐘

2022-04-14 15:33:49 1941

1941

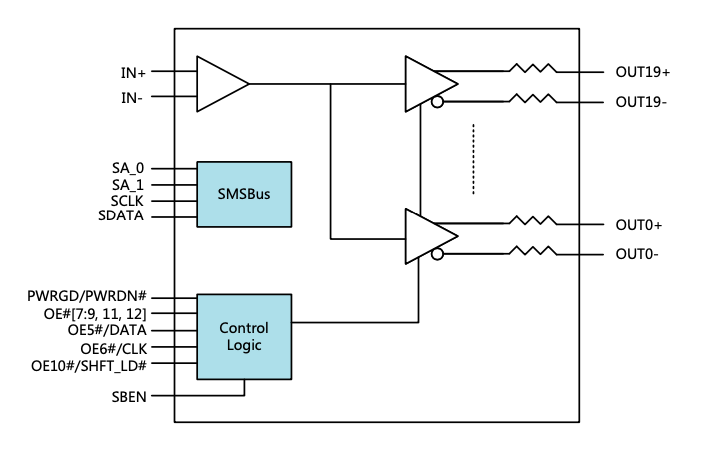

Silicon Laboratories (芯科實驗室有限公司, NASDAQ: SLAB)今日宣布推出業(yè)界首款通用時鐘緩沖器(clock buffer),可以用單顆IC替代多顆LVPECL、LVDS、CML、HCSL和LVCMOS緩沖器,而無需多個不同格式緩沖器

2012-11-06 09:08:20 2237

2237 20路輸出PCIe時鐘緩沖器是下一代服務器、數(shù)據(jù)中心、存儲設(shè)備及其他PCIe應用的理想選擇。

2019-07-01 16:36:40 1028

1028 畢設(shè)題目 :75mhz雙路時鐘緩沖器,求助

2021-02-27 21:45:00

差分信號傳輸?shù)膬?yōu)勢就是通過成對的差分線傳輸一個信號,只要它們一直親密無間、步調(diào)一致,在接收端就能夠消除掉沿途中遇到的任何干擾,原理參見下面的圖示。差分時鐘傳輸降低噪聲在PCB板上走線避不開的就是因

2019-05-15 05:26:22

NB7V33MMNGEVB,差分時鐘分頻器評估板。 NB7V33M是一個4分頻時鐘分頻器,具有異步復位功能。差分時鐘輸入包含內(nèi)部50歐姆端接電阻,可接受LVPECL,CML和LVDS邏輯電平

2019-02-21 09:44:22

大家好,在我的項目中,我有差分時鐘輸入。當我實現(xiàn)我的設(shè)計時,我打開了實現(xiàn)的文件。我已經(jīng)習慣了I / O端口planninn菜單欄和從那里分配的引腳號和類型。另一方面,時鐘輸入僅顯示為一個輸入

2020-08-05 09:56:08

我用xilinxA735T,pcs的差分時鐘管腳輸入一個差分時鐘,使用IBUFDS_GTE2得到一個單端時鐘,把這個單端時鐘引到外部管腳,用示波器沒有看到。各位大神幫忙指點一下

2016-06-02 09:53:17

的。在I / O規(guī)劃布局中,我可以看到該工具將這些信號視為單端信號。這是我在XPS中開發(fā)的自定義IP。有幾個差分時鐘信號和一些差分數(shù)據(jù)信號進入。我懷疑它希望輸入緩沖區(qū)位于IP的頂層。這些輸入緩沖區(qū)在

2018-11-02 11:38:13

ADCLK846 / PCBZ,ADCLK846評估板是一款高性能時鐘扇出緩沖器。評估板采用高品質(zhì)Rogers介電材料制造。傳輸線路徑盡可能差分地保持接近100歐姆

2019-02-21 09:54:43

AKD8181D,AK8181時鐘扇出緩沖器評估板。因此,很容易評估DC / AC特性并確認產(chǎn)品功能

2020-08-25 15:26:54

(30)FPGA原語設(shè)計(單端時鐘轉(zhuǎn)差分時鐘)1.1 目錄1)目錄2)FPGA簡介3)Verilog HDL簡介4)FPGA原語設(shè)計(單端時鐘轉(zhuǎn)差分時鐘)5)結(jié)語1.2 FPGA簡介FPGA

2022-02-23 06:32:02

NB7V32MMNGEVB,差分時鐘分頻器評估板。 NB7V32M是一個差分2分頻時鐘分頻器,具有異步復位功能。差分時鐘輸入包含內(nèi)部50歐姆端接電阻,可接受LVPECL,CML和LVDS邏輯電平

2019-02-20 09:41:47

如果輸入時鐘時差分時鐘信號,如何編寫testbench?

2014-09-15 19:37:38

SI53159-EVB,用于PoE無線接入點的100至210MHz時鐘發(fā)生器評估板。 Si53159是一款九端口PCIe時鐘緩沖器,符合PCIe Gen1,Gen2和Gen3標準

2020-08-27 12:20:38

`請問什么是音頻緩沖器?`

2019-08-23 16:27:28

100fs-300fs之間?

疑問3:是不是使用PLL類型的時鐘發(fā)生器芯片帶來的抖動誤差會比較大?針對14位的ADC輸入差分時鐘有此類型的參考嗎?

模擬輸入部分:

疑問1:參考文檔中使用AD8138差分驅(qū)動芯片

2023-12-22 08:19:31

具備SSTL_18輸入與輸出的25 位可配置寄存緩沖器的特性及應用25 位 1:1 或14 位 1:2 可配置寄存緩沖器適用于 1.7 V 至 1.9 V 的 VCC 工作環(huán)境。就 1:1 引腳配置

2009-10-28 14:41:58

嗨,我有一個來自2.5V LVDS時鐘緩沖器的時鐘(http://www.onsemi.com/pub_link/Collat??eral/MC100EP210S-D.PDF),我想在FPGA中使

2020-07-24 15:16:28

高端時鐘緩沖器用戶不再需要面對抖動與電流的折衷

2021-04-06 06:24:31

中,一個時鐘源要驅(qū)動多個器件,因此可使用時鐘緩沖器(通常稱為扇出緩沖器)來復制信號源,提供更高的激勵電平。圖 1. 使用扇出緩沖器創(chuàng)建大量單輸入頻率副本LMK00304 扇出緩沖器就是一個很好的例子

2022-11-21 07:25:28

大家好 我在設(shè)計中使用virtex -4 FPGA做了一個項目。從外部到我的FPGA只有單端時鐘。但是,連接到FPGA的AD需要幾個差分時鐘。如何實現(xiàn)這個功能? 據(jù)我所知,DCM原語確實提供了兩種

2019-01-21 08:52:16

你好我正在使用ML605板,差分時鐘輸入產(chǎn)生一個全局使用的時鐘。但是當試圖約束時鐘時,我不知道如何設(shè)置它。有什么建議么?謝謝

2019-10-28 07:21:01

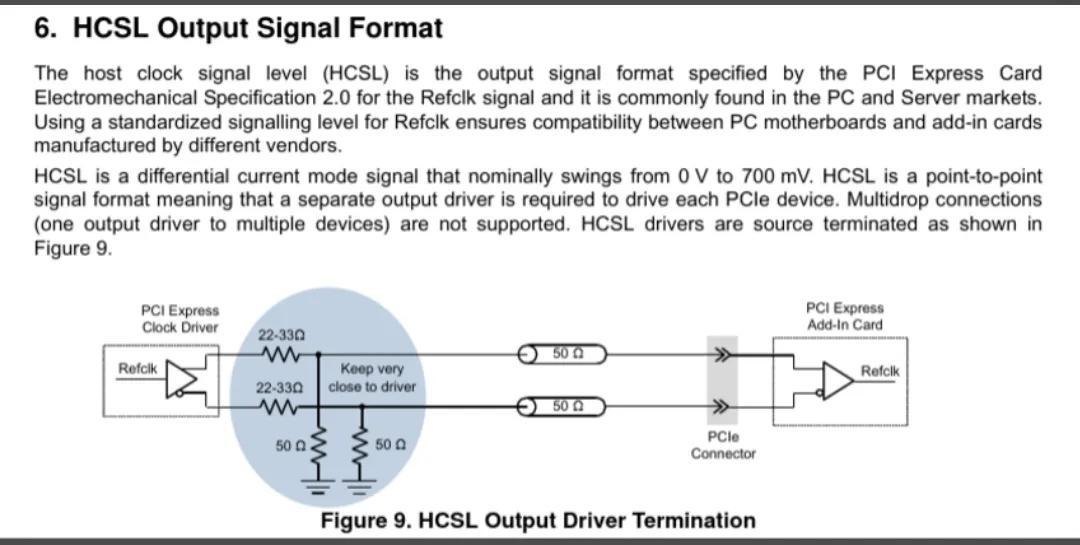

沿使其與ZDB輸出同步的多PCIe參考時鐘產(chǎn)生器)。 例如,NB3N1200K/NB3W1200L零延遲緩沖器(ZDB)帶12路HCSL/NMOS推挽輸出,特性包括:支持DIF SRC時鐘;12個差

2018-10-09 11:38:19

嗨,我是第一次在Fpga工作。我為所有32個收發(fā)器提供125 MHz差分時鐘。現(xiàn)在我需要為I / O bank提供125 MHz差分時鐘。有沒有辦法使用GTX時鐘用于這個目的(正如我讀到的,MRCC

2020-07-15 09:48:46

我從賽靈思購買了ML405板。我需要在Virtex4中使用MGT做一些事情。從IP核生成器生成的文件中,看起來參考時鐘由GT11CLK從一對差分時鐘輸入生成。但是我找不到ML405上的差分時鐘源,我

2019-08-15 06:04:11

的不確定性,導致抖動增加。在實際系統(tǒng)中,一個時鐘源要驅(qū)動多個器件,因此可使用時鐘緩沖器(通常稱為扇出緩沖器)來復制信號源,提供更高的激勵電平。圖 1. 使用扇出緩沖器創(chuàng)建大量單輸入頻率副本LMK00304

2018-09-13 10:11:44

RS2CG5705B是一款符合PCI Express 3.0和以太網(wǎng)要求的擴頻時鐘發(fā)生器。該電路用于PC或嵌入式系統(tǒng),以顯著減少電磁干擾(EMI)。RS2CG5705B提供4對差分(HCSL)或

2024-01-24 17:31:16

有沒有哪位大佬知道國產(chǎn)的高速差分時鐘緩沖芯片型號以及單端時鐘轉(zhuǎn)差分時鐘的時鐘轉(zhuǎn)換芯片

2020-04-03 15:43:18

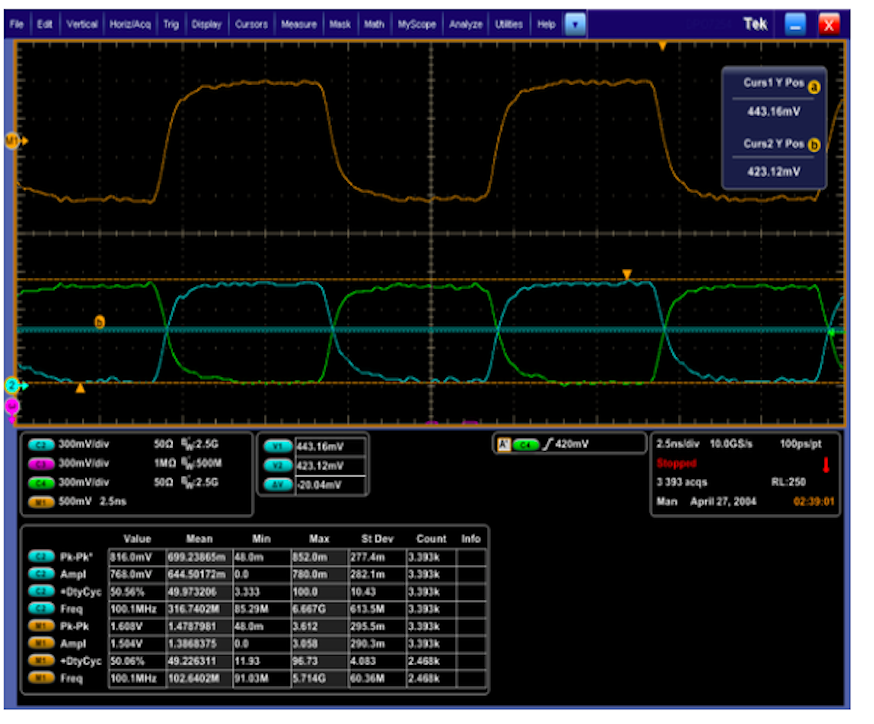

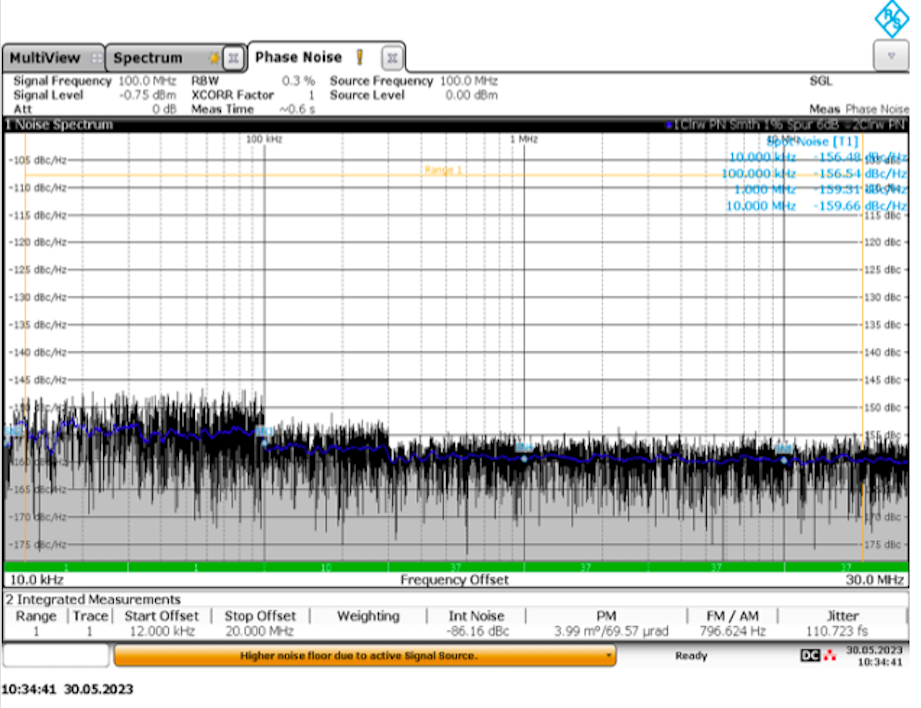

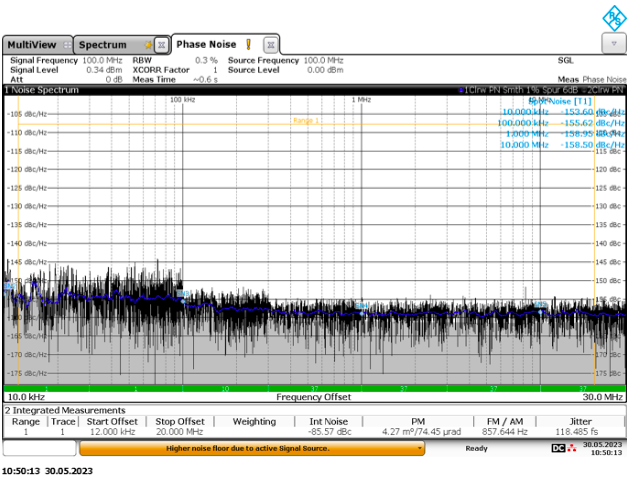

需求。作為該最新博客系列的開篇文章,我將幫助您了解如何正確測量時鐘緩沖器的附加抖動。為什么抖動很重要?在當今數(shù)據(jù)通信、有線及無線基礎(chǔ)設(shè)施以及其它高速應用等高級系統(tǒng)中,時鐘抖動是整體系統(tǒng)性能的關(guān)鍵因素。要

2018-09-13 14:38:43

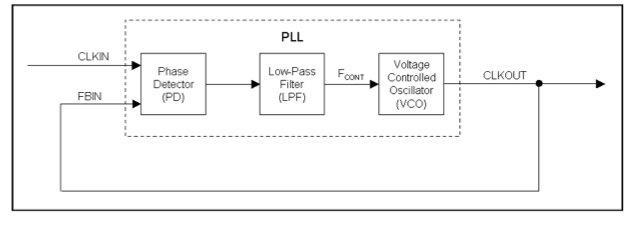

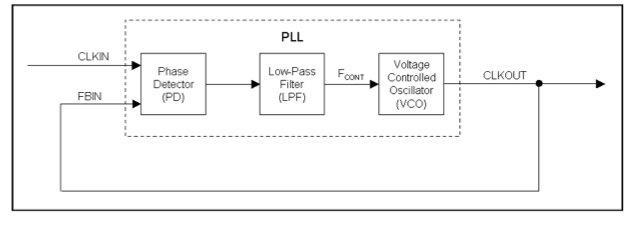

怎么設(shè)計一種用于多路輸出時鐘緩沖器中的鎖相環(huán)?鎖相環(huán)主要結(jié)構(gòu)包括哪些?

2021-04-20 06:27:26

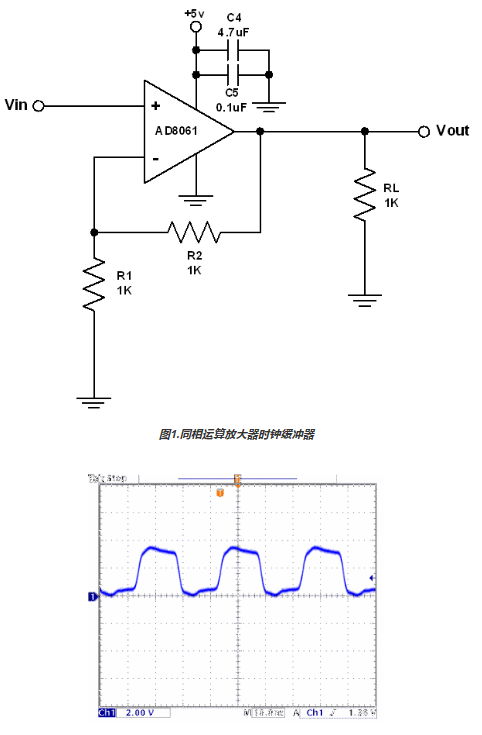

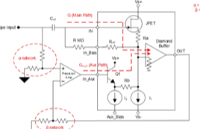

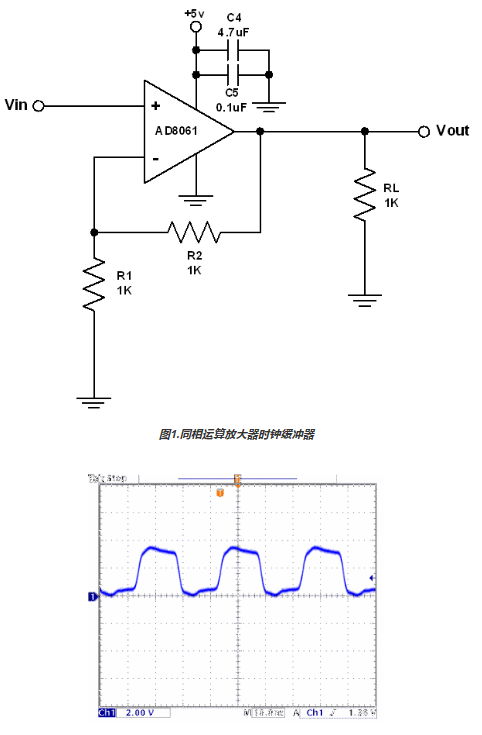

與傳統(tǒng)的時鐘緩沖器相比,高速運算放大器有哪些優(yōu)勢?怎樣去設(shè)計一個靈活的時鐘緩沖器?

2021-04-14 06:35:37

嗨,大家好! 我遇到了一個問題,希望能幫助我。當我使用chipcope分析我的設(shè)計時,我發(fā)現(xiàn)全局差分時鐘引腳與chipcope端口沒有連接,因為它沒有端口與芯片內(nèi)的差分時鐘引腳相連,但它

2020-06-12 14:22:16

了就是下雨了。今天咱們來看看零延時緩沖器吧。也是由緩沖一詞想到的。它是指一種可以將一個時鐘信號扇出成多個時鐘信號,并使這些輸出之間有零延時和很低的偏斜的器件。此器件很適合用于要求輸入到輸出和輸出到輸入

2014-05-20 17:32:38

`請問高速緩沖器是什么?`

2019-08-23 16:32:59

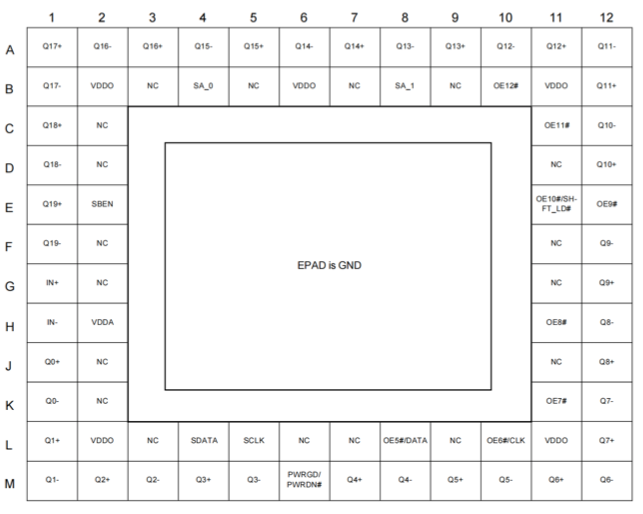

US5D310是一款支持2.1GHz、2組10路差分輸出的時鐘緩沖器,每組輸出可獨立配置,適用于高頻、低抖動時鐘分配和電平轉(zhuǎn)換。完全兼容

2021-09-27 16:54:19

US5D308是一款支持2.1GHz、2組8路差分輸出的時鐘緩沖器,每組輸出可獨立配置,適用于高頻、低抖動時鐘分配和電平轉(zhuǎn)換。完全兼容TI

2021-09-30 10:13:18

US5D306是一款支持2.1GHz、2組6路差分輸出的時鐘緩沖器,每組輸出可獨立配置,適用于高頻、低抖動時鐘分配和電平轉(zhuǎn)換。完全兼容TI LMK00306

2021-09-30 13:51:29

US5D304是一款支持2.1GHz、4路差分輸出的時鐘緩沖器,適用于高頻、低抖動時鐘分配和電平轉(zhuǎn)換。完全兼容TI LMK00304。

2021-09-30 14:00:06

US5D210是一款支持2.1GHz、1分10路LVDS差分輸出的時鐘緩沖器,適用于高頻、低抖動時鐘分配和電平轉(zhuǎn)換。完全兼容IDT 5T9310

2021-09-30 14:09:18

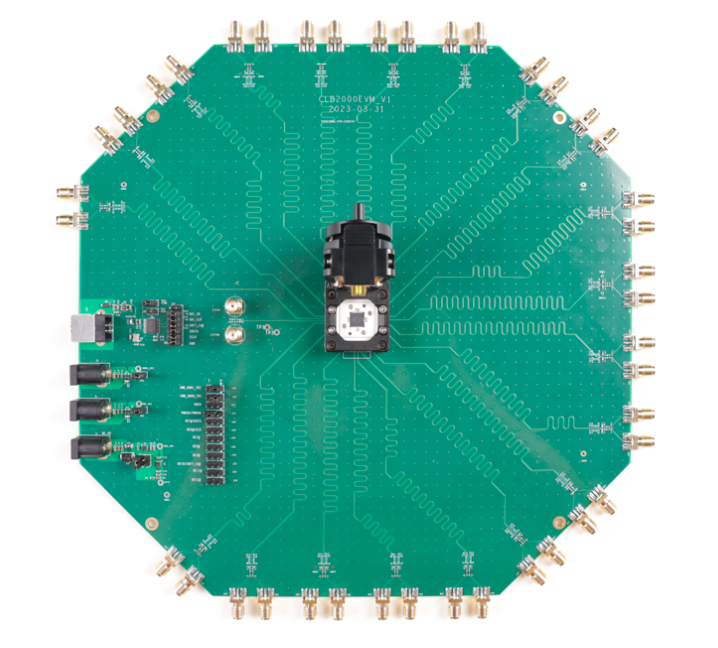

符合 DB2000QL 標準、適用于第 1 代到第 5 代 PCIe® 的 20 路輸出時鐘緩沖器 Function Clock buffer, Differential

2022-11-30 16:58:52

時鐘緩沖器芯片 10路單端buffer是一款高性能、低噪聲的LVCMOS房出緩沖器,此緩沖器可以從單端、差分或晶體輸入中分配出10路超低抖動時鐘。典型應用場景:· RRU基準分布· SONET

2024-01-26 11:09:00

MAX19996 具有片內(nèi)LO緩沖器的完全集成、2000MHz至3000MHz下變頻混頻器

Maxim推出具有片內(nèi)LO緩沖器的完全集成、2000MHz至3000MHz下變頻混頻器MAX19996。器件采用Maxim

2008-10-09 08:17:31 721

721 TI推出正弦至正弦波時鐘緩沖器

日前,德州儀器 (TI) 宣布推出業(yè)界最小型 4 通道、低功耗、低抖動正弦至正弦波時鐘緩沖器。作為正弦波時鐘緩沖器系列產(chǎn)品中的首款

2009-11-30 10:53:51 815

815 TI新推高集成正弦波時鐘緩沖器可顯著降低成本,節(jié)省板級空間

日前,德州儀器 (TI) 宣布推出業(yè)界最小型 4 通道、低功耗、低抖動正弦至正弦波時鐘緩沖器。作為正弦

2009-12-01 08:43:11 1112

1112 緩沖器,緩沖器是什么?

buffer 中文譯名: 緩沖,緩沖器,緩沖液 解釋:1、 電信設(shè)備。在數(shù)據(jù)傳輸中,用來彌補不同數(shù)據(jù)處

2010-03-08 13:30:11 2253

2253 緩沖器,緩沖器基本原理是什么?

最基本線路構(gòu)成的門電路存在著抗干擾性能差和不對稱等缺點。為了克服這些缺點,可以在輸出或輸

2011-09-03 19:10:46 9257

9257 Silicon Laboratories (芯科實驗室有限公司)日前宣布擴展其PCI Express(PCIe)時鐘發(fā)生器和時鐘緩沖器產(chǎn)品組合。

2012-02-02 09:31:56 1395

1395 日前,德州儀器 (TI) 宣布推出 2 款最新通用時鐘緩沖器系列,進一步壯大其高性能時鐘緩沖器產(chǎn)品陣營。CDCLVC1310 LVCMOS 時鐘緩沖器可在晶振模式下實現(xiàn) –169 dBc/Hz 的業(yè)界領(lǐng)先相位噪聲

2012-04-05 08:47:28 1062

1062 中國,北京-2014年12月4日-為互聯(lián)網(wǎng)基礎(chǔ)設(shè)施提供高性能時鐘解決方案的領(lǐng)導廠商Silicon Labs(芯科實驗室有限公司,NASDAQ:SLAB)今天宣布推出PCI Express(PCIe) Gen1/2/3扇出緩沖器,此產(chǎn)品為包括服務器、存儲器和交換機在內(nèi)的數(shù)據(jù)中心應用而設(shè)計。

2014-12-04 10:54:49 1004

1004 三態(tài)緩沖器三態(tài)緩沖器三態(tài)緩沖器三態(tài)緩沖器三態(tài)緩沖器三態(tài)緩沖器三態(tài)緩沖器

2015-11-16 11:59:30 0

0 LMK0033x是德州儀器(TI)推出的業(yè)界最低抖動的PCIe時鐘扇形緩沖器。現(xiàn)在就讓德儀的工程師向你介紹它的具體情況吧!

2018-06-13 11:52:00 4883

4883 EngineerIt-測量時鐘扇出緩沖器的殘余噪聲

2018-08-13 00:23:00 3233

3233 面向下一代數(shù)據(jù)中心應用的四款全新20路微分時鐘緩沖器,遠超PCIe?第五代(Gen 5)防抖標準。新推出的ZL40292(終端電阻85Ω)和ZL40293(終端電阻100Ω)專門依據(jù)最新的DB2000Q規(guī)格設(shè)計,而ZL40294

2019-07-02 14:48:10 5207

5207 本應用報告介紹了實現(xiàn) IDT 基于 PLL 的零延遲緩沖器的輸入?yún)⒖?b class="flag-6" style="color: red">時鐘和輸出時鐘之間定義的相位關(guān)系的不同方法。該報告重點介紹了 PLL 反饋環(huán)路中不同走線長度和反饋時鐘輸入端的電容負載對生成早期

2021-06-15 10:48:41 2103

2103

電子發(fā)燒友網(wǎng)站提供《DC1954A 時鐘緩沖器參考設(shè)計.pdf》資料免費下載

2020-12-31 04:50:23 8

8 電子發(fā)燒友網(wǎng)站提供《DC1954A 時鐘緩沖器參考設(shè)計.pdf》資料免費下載

2020-12-31 04:54:37 9

9 電子發(fā)燒友網(wǎng)站提供《NB6N11SMNGEVB 時鐘緩沖器參考設(shè)計.pdf》資料免費下載

2020-12-31 04:57:05 11

11 電子發(fā)燒友網(wǎng)站提供《NB6L611MNGEVB 時鐘緩沖器參考設(shè)計.pdf》資料免費下載

2020-12-31 04:58:58 11

11 電子發(fā)燒友網(wǎng)站提供《NB6L72MMNGEVB 時鐘緩沖器參考設(shè)計.pdf》資料免費下載

2020-12-31 05:00:15 12

12 電子發(fā)燒友網(wǎng)站提供《NB6L11SMNGEVB 時鐘緩沖器參考設(shè)計.pdf》資料免費下載

2020-12-31 05:01:04 9

9 電子發(fā)燒友網(wǎng)站提供《NB6L14MMNGEVB 時鐘緩沖器參考設(shè)計.pdf》資料免費下載

2020-12-31 05:01:59 11

11 電子發(fā)燒友網(wǎng)站提供《ADCLK846/PCBZ 時鐘緩沖器參考設(shè)計.pdf》資料免費下載

2020-12-31 05:02:52 7

7 電子發(fā)燒友網(wǎng)站提供《ADCLK944/PCBZ 時鐘緩沖器參考設(shè)計.pdf》資料免費下載

2020-12-31 05:03:49 12

12 電子發(fā)燒友網(wǎng)站提供《NB7L14MNGEVB 時鐘緩沖器參考設(shè)計.pdf》資料免費下載

2020-12-31 05:04:39 13

13 電子發(fā)燒友網(wǎng)站提供《NB6N14SMNGEVB 時鐘緩沖器參考設(shè)計.pdf》資料免費下載

2020-12-31 05:05:23 9

9 本文將探討與全新BUF802 Hi-Z緩沖器單芯片實施相比,分立式緩沖器復合環(huán)路實施存在的設(shè)計難題。

2022-02-11 11:58:48 2745

2745

全球半導體解決方案供應商瑞薩電子(TSE:6723)近日宣布,率先推出符合PCIe Gen6嚴格標準的時鐘緩沖器和多路復用器。

2022-04-15 11:18:51 1253

1253 IDT 還提供另一個更簡單的 CMOS 緩沖器系列,即5PB11xx系列,由五個時鐘扇出緩沖器成員組成,其中最后兩位數(shù)字代表輸出數(shù)量。這些緩沖器是非常高性能、低抖動、低偏移和傳播延遲、非常低功耗的直接 CMOS 扇出緩沖器。

2022-05-05 15:41:13 1500

1500

KOYUELEC光與電子提供技術(shù)支持有容微電子GM50301:超低附加抖動差分輸出時鐘緩沖器

2022-05-07 11:38:45 2271

2271 KOYUELEC光與電子提供技術(shù)支持,有容微電子GM50101:超低附加抖動時鐘緩沖器。

2022-05-07 11:40:15 1070

1070 什么是時鐘緩沖器(Buffer)?時鐘緩沖器(Buffer)參數(shù)解析 什么是時鐘緩沖器(Buffer)?我們先把這個概念搞清楚。 時鐘緩沖器就是常說的Clock Buffer,通常是指基于非PLL

2022-10-18 18:36:54 18409

18409

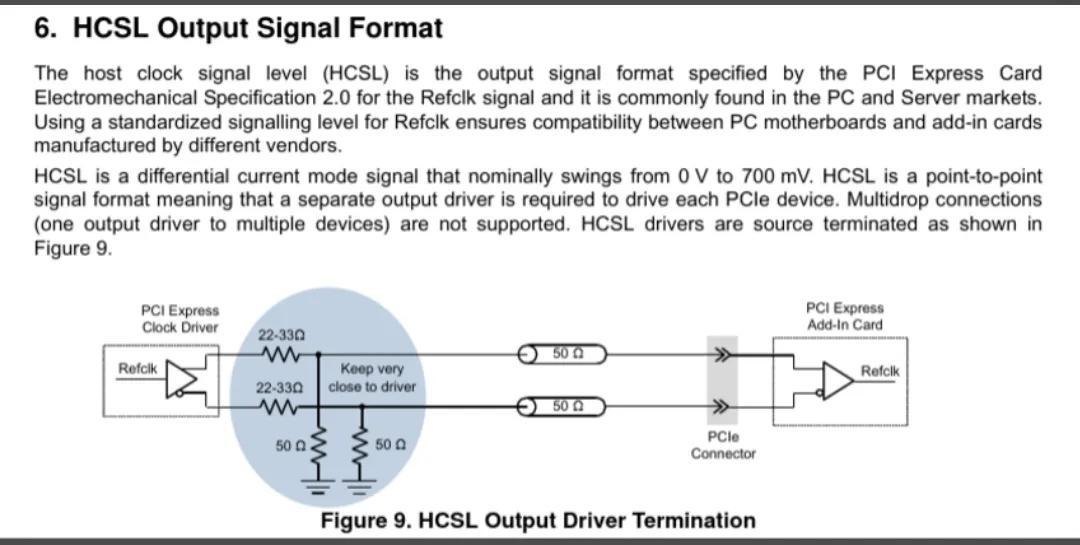

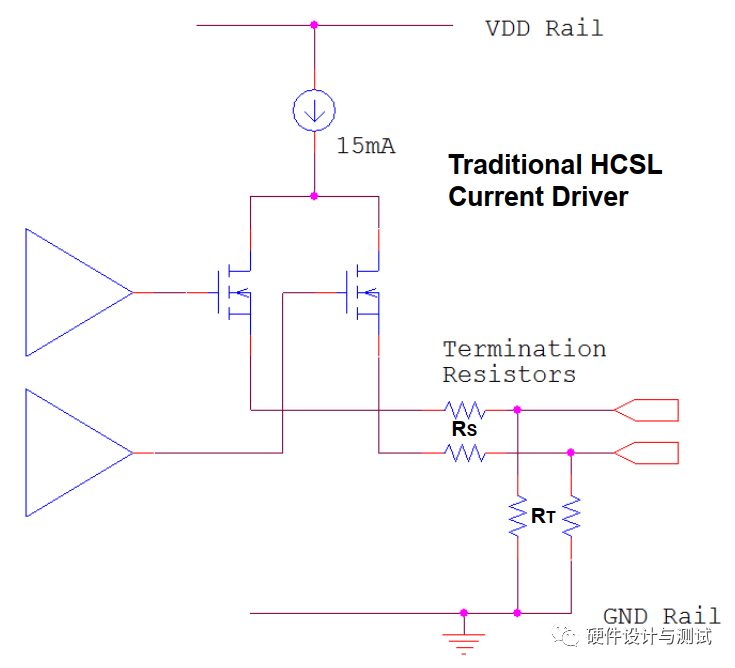

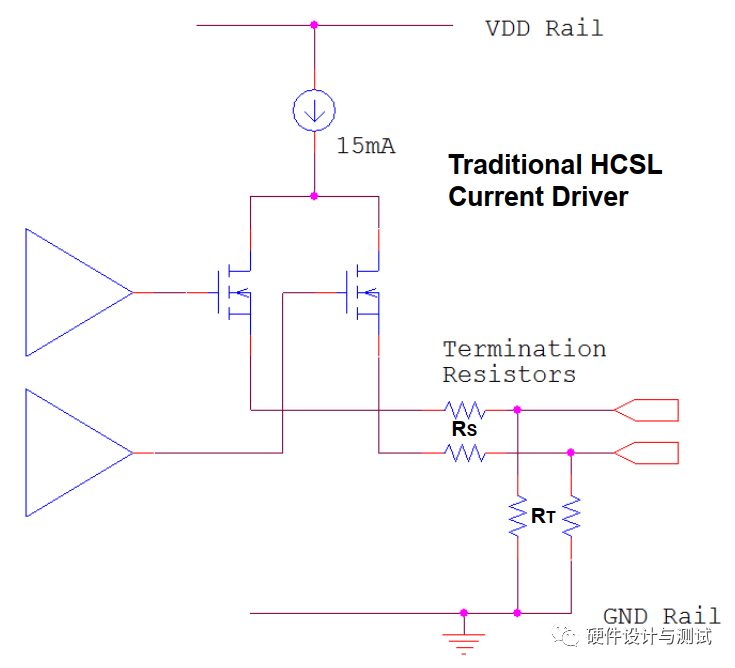

HCSL(HCSL--High?speed Current Steering Logic)一般用于PCIE參考時鐘的電平類型,根據(jù)規(guī)范需要下拉電路,如下圖HCSL之間的DC耦合。HCSL為電流輸出驅(qū)動,輸出結(jié)構(gòu)由通常通過50Ω電阻器接地的15 mA開關(guān)電流源驅(qū)動。 標稱信號擺幅為750 mV。

2023-04-20 11:39:38 1707

1707

液壓緩沖器強度是否能夠調(diào)節(jié),取決于液壓緩沖器的種類,目前市面上較為常用的液壓緩沖器包括可調(diào)液壓緩沖器、不可調(diào)液壓緩沖器,這兩種緩沖器調(diào)節(jié)強度的實際效果是不一樣的。

2023-04-24 16:12:01 2158

2158 HMC7043是一種高性能時鐘緩沖器,用于為具有并行或串行(JESD204B型)接口的高速數(shù)據(jù)轉(zhuǎn)換器分配超低相位噪聲參考。

2023-05-31 10:47:57 1636

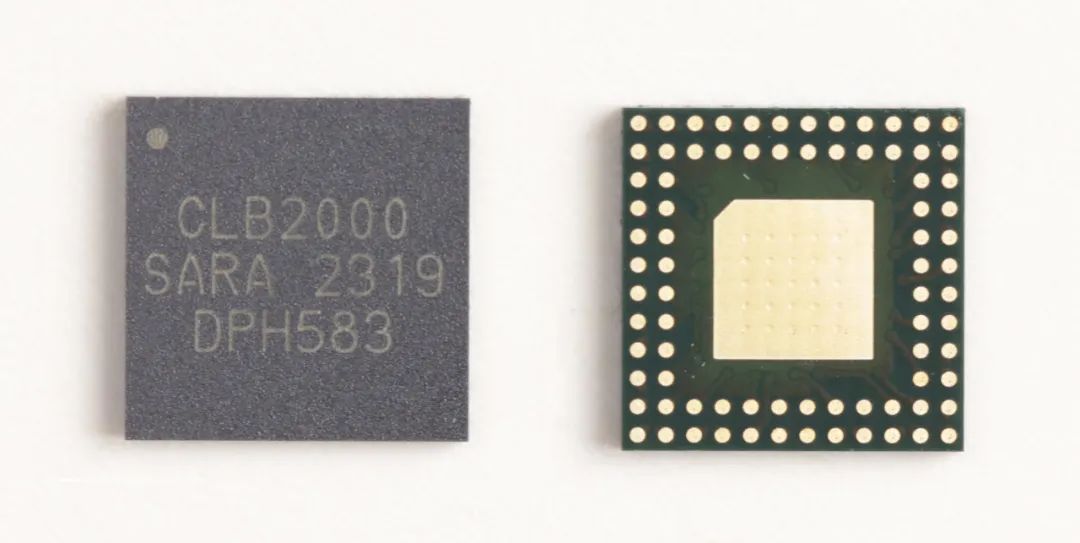

1636 高性能的時鐘器件是高帶寬、高速率、高算力、大模型的基礎(chǔ)。核芯互聯(lián)近日推出面向下一代數(shù)據(jù)中心應用的超低抖動全新20路LP-HCSL差分時鐘緩沖器CLB2000,其業(yè)界領(lǐng)先的附加抖動性能遠超PCIe Gen 5和PCIe Gen 6的標準。

2023-06-08 15:29:55 805

805

在消費電子應用中,與典型的時鐘緩沖應用相比,其頻率往往較低,要求也更低,廉價的高速運算放大器(~100 MHz帶寬)可以為傳統(tǒng)時鐘緩沖器提供有吸引力的替代方案。高速放大器可能比傳統(tǒng)時鐘緩沖器便宜,但它們可以適應各種設(shè)計配置。

2023-06-17 17:29:14 706

706

時鐘緩沖器選型目錄

2021-11-19 16:38:53 789

789

Diodes(達爾科技)是全球主要的差分時鐘IC供應商。Diodes的差分時鐘訊號緩沖器產(chǎn)品組合涵蓋了多種不同輸出訊號(LVPECL,LVDS,HCSL,LowpowerHCSL)與輸出端口數(shù)

2022-10-19 11:08:24 350

350

HCSL:高速電流控制邏輯(High-speed Current Steering Logic)是Intel為PCIe參考時鐘定義的差分時鐘,用于PCIe2.0電氣規(guī)范中定義對RefClk時鐘所定義

2023-09-15 14:39:54 2447

2447

電子發(fā)燒友網(wǎng)站提供《低傾斜1到4時鐘緩沖器524S數(shù)據(jù)表.pdf》資料免費下載

2023-12-21 10:37:32 0

0 電子發(fā)燒友網(wǎng)站提供《551S低傾斜1到4時鐘緩沖器數(shù)據(jù)表.pdf》資料免費下載

2023-12-21 10:41:18 0

0 等應用已集成越來越多的PCIe終端,矽力杰新一代高性能PCIe時鐘緩沖器SQ82100可以為系統(tǒng)提供20路超低附加抖動的LP-HCSL參考時鐘,能夠簡化系統(tǒng)布局,進一步提高

2023-12-20 08:19:38 240

240

電子發(fā)燒友App

電子發(fā)燒友App

評論