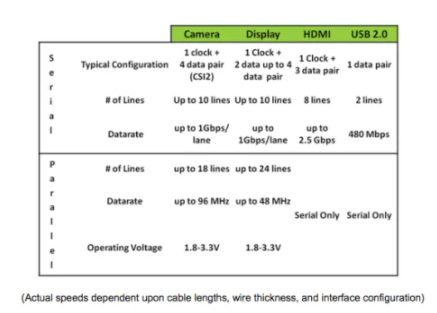

現(xiàn)在CMOS傳感器的分辨率越來越大,對應(yīng)的,對數(shù)據(jù)傳輸接口的要求也越來越高。根據(jù)熊貓君有限的實現(xiàn)和調(diào)試經(jīng)驗,基本上遇到了:

①多通道HiSPi接口:主要是Aptina(現(xiàn)已經(jīng)被安森美收購),常用的有1080P60的AR0331(3.1M),3664×2748P15的MT9J003,3984×2712P80(開窗輸出最高可達(dá)1200fps)的AR1011等;

②多通道LVDS接口:主要有索尼系列、安森美的Python系列、國產(chǎn)如長光辰芯和德國viimagic系列等,至少熊貓君用過的IMX172/IMX122/IMX185/

IMX236、安森美Python全系列和VII9222等都是LVDS輸出;

③MIPI接口:多用于手機(jī),一些監(jiān)控用的CMOS如Sony IMX185、OV14810等也帶;

④CCIR656:一般低分辨率的會帶CCIR656接口,也有一些廠家的高分?jǐn)z像頭也帶,比如OV14810;

⑤并行接口:較早設(shè)計的CMOS許多都是直接并口輸出,比如Aptina的MT9M031、MT9J003都帶有并口輸出;

熊貓君在這里想討論的是前三種接口的實現(xiàn),它們是業(yè)界應(yīng)用最廣泛而且對FPGA資源有著共性要求。

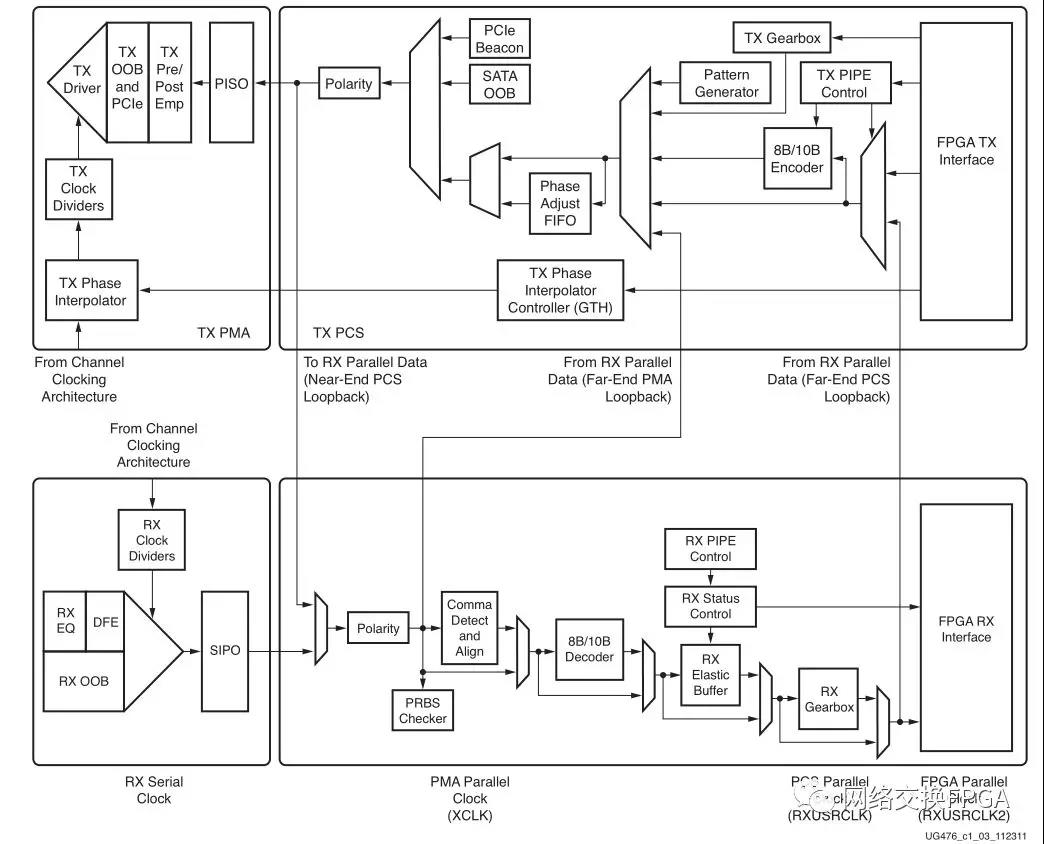

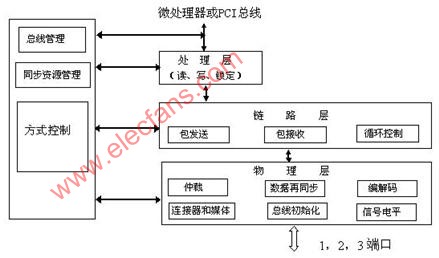

無論是HiSPi、LVDS還是MIPI,其核心思想就是要實現(xiàn)將高速串行信號恢復(fù)成并行數(shù)據(jù)。這將會用到XilinxFPGA IOB上的一個重要的資源——ISERDES。

實現(xiàn)串行信號的并行化,光有ISERDES還不行,還需要用到IOBANK上的延時模塊IDELAYCTRL和IOB上的IODELAYE以及相關(guān)的相位訓(xùn)練算法。

1 Xilinx的IO資源

本節(jié)對用到的IO資源作簡要的介紹。

1.1 IDELAYCTRL資源

在電壓、溫度等因素變化時,可能會影響到系統(tǒng)的時序,此時IDELAYCTRL模塊就可以連續(xù)補償時鐘域內(nèi)所有個體的delay taps (IDELAY/ODELAY)。如果使用了IOB上的IDELAY或ODELAY資源,那么就必須使用IDELAYCTRL資源。請注意,整個IO BANK里面只有一個IDELAYCTRL。

IDELAYCTRL很重要的一個輸入項就是參考時鐘REFCLK,補償時鐘域內(nèi)所有模塊的時序參考,這個時鐘必須由BUFG或BUFH驅(qū)動。REFCLK必須保證在FIDELAYCTRL_REF+IDELAYCTRL_REF_PRECISION(MHz)ppm才能保證IDELAY/ODELAY的延時分辨率:

(TIDELAYRESOLUTION=1/(32x 2 x FREF))

1.2 IDELAYE2邏輯

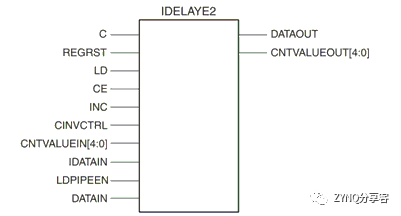

IDELAYE2邏輯是一個31抽頭的循環(huán)延時補償模塊,對輸入的信號進(jìn)行指定分辨率的延時,F(xiàn)PGA可以直接訪問。Tap延時分辨率由IDELAYCTRL的參考時鐘提供持續(xù)補償。圖(1)是IDELAYE2接口示意圖,表(1)是對這些接口的描述,表(2)是對邏輯參數(shù)的描述。

圖(1 )IDELAYE2****接口示意圖。

表(1 )IDELAYE2****接口描述

表(2 )IDELAYE2****邏輯參數(shù)描述

以下以VAR_LOAD模式為例說明延時的時序動作,如圖(2)所示。

圖(2 )延時時序動作模型

a)Clock Event 0:

在LD有效前,CNTVALUEOUT輸出為未知值;

b)Clock Event 1:

在C的上升沿采樣到LD有效,此時DATAOUT延時CNTVALUEIN指定的延時Taps,改變tap Setting到Tap2,CNTVALUEOUT更新到新的Tap值;

c)Clock Event 2:

INC和CE有效,此時指定了增量操作,Tap值加1,DATAOUT輸出從Tap2更新到Tap3,CNTVALUEOUT更新到新的Tap值;

d)Clock Event 3

LD有效,DATAOUT輸出延時更新到Tap10,CNTVALUEOUT更新到新的Tap值。

1.3 ISERDESE2邏輯

輸入串轉(zhuǎn)并邏輯可以看做是OSERDESE2的逆過程,在SDR模式下可支持2-、3-、4-、5-、6-和7-的串并轉(zhuǎn)換,在DDR模式下可支持2-、4-、6-、8-的串并轉(zhuǎn)換,級聯(lián)DDR模式下還可擴(kuò)展到10-和14-。每一個ISERDESE2包括:

a)專門的串并轉(zhuǎn)換器;

b)Bitslip子模塊用于源同步接口;

c)專用的可支持strobe-based的存儲接口。

圖(3)是ISERDESE2的結(jié)構(gòu)示意圖。表(3)是ISERDESE2接口描述,表(4)示ISERDESE2的參數(shù)描述。

圖(3 )ISERDESE2****結(jié)構(gòu)示意圖

表(3 ) ISERDESE2

表(4)ISERDESE2的參數(shù)描述

(1) 時鐘方案

CLK和CLK_DIV必須是嚴(yán)格對齊的時鐘,雖然允許使用BUFIO/BUFR,但任然有可能存在相位問題。圖(5)時采用BUFIO/BUFR的方案。

圖(5 )采用BUFIO/BUFR****的時鐘方案

一般的,根據(jù)接口類型的差異,時鐘必須滿足以下的約束:

①networking interface

a)CLK→BUFIO;CLKDIV→BUFR;

b)CLK→MMCM/PLL;CLKDIV→和CLK相同的MMCM/PLL的CLKOUT[0:6]的輸出,使用MMCM時CLK和CLKDIV必須使用相同的驅(qū)動BUF;

c)CLK→BUFG;CLKDIV→BUFG。

②MEMORY Interface Type

a)CLK→BUFIO, OCLK→BUFIO,或CLKDIV→BUFR;

b)CLK→MMCM或PLL, OCLK→MMCM,或CLKDIV由同一個MMCM/PLL的CLKOUT[0:6]驅(qū)動;

c)CLK→BUFG,CLKDIV→不同的BUFG。

OCLK和CLKDIV的輸入相位必須是嚴(yán)格對齊的,CLK和OCLK之間不要求相位關(guān)系。From CLK to OCLK的時鐘域必須進(jìn)行補償。

其他接口類型的時鐘方案參考文檔UG471。

(2) BitSlip子模塊

BitSlip用于調(diào)整并行寄存器輸出串行數(shù)據(jù)的位置。在SDR模式下,每一個BitSlip脈沖讓輸出pattern的數(shù)據(jù)左移1bit;在DDR模式下,第一個BitSlip右移1bit,第二個BitSlip左移3bit,依次進(jìn)行,移動規(guī)律如圖(6)所示。BitSlip一定是和CLKDIV同步的一個脈沖。

圖(6 )BitSlip****訓(xùn)練移位規(guī)律

在上面所介紹的資源中,IDELAYE2是動態(tài)相位對其訓(xùn)練的神器,ISERDESE2實現(xiàn)串并轉(zhuǎn)換,其Bitslip功能是實現(xiàn)并行化數(shù)據(jù)對齊的關(guān)鍵。

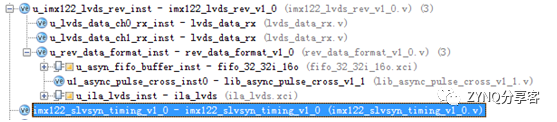

2 LVDS高速接口實現(xiàn)實例

因為MIPI接口有其完整的物理層協(xié)議,因此不在這里講具體實現(xiàn),本文以Sony的IMX122 CMOS為例,聊一聊高速LVDS(HiSPi類似,只是電平標(biāo)準(zhǔn)有一點區(qū)別)接口在Xilinx 7系列FPGA和Zynq SoC上的實現(xiàn)。

2.1 需求分析

以Sony IMX122 CMOS為例,配置在1080P分辨率可輸出30fps。CMOS在初始化完成后輸出兩通道穩(wěn)定的LVDS數(shù)據(jù),LVDS接收模塊在收到配置完成信號后開始工作。因此,這個LVDS接收模塊需要實現(xiàn):

① CMOS工作在Slave模式下,向CMOS發(fā)出參考時鐘(INCK)、行同步(XHS)、幀同步(XVS)信號;

② 接收LVDS數(shù)據(jù)并將它恢復(fù)成為指定的圖像數(shù)據(jù)格式;

③ 提供測試信息接口。

2.2 IMX122 CMOS輸出特性

本小節(jié)簡介IMX122 CMOS的一些特性。

2.2.1 同步時序要求

在Slave模式下需要向CMOS提供周期穩(wěn)定的XHS和XVS信號,兩者的時序要求如圖7所示。在產(chǎn)生同步時序時需要注意以下要點:

① XVS和XHS必須是穩(wěn)定的周期性信號;

② XVS和XHS信號的低電平保持時間為4~100個INCK;

③ XHS可以和XVS同時拉低,也可延時一個時鐘周期拉低。

圖7Slave模式下同步時序

2.2.2 輸出數(shù)據(jù)率

在串行SDR LVDS模式下以12bit模式輸出,數(shù)據(jù)率為891Mbps,每個通道的數(shù)據(jù)率為445.5Mbps。

2.2.3 Sync Code格式

在串行輸出模式下,CMOS通過輸出固定的Sync Code來指示圖像的有效幀、行信息,接收器需通過查找這些Sync Code來恢復(fù)圖像。IMX122可提供兩種模式的Sync Code,這里配置為SyncCode1,其具體定義如圖8所示。

圖8 IMX122 Sync Code定義

2.2.4 輸出圖像組織形式

IMX122在1080P讀出模式下,輸入?yún)⒖紩r鐘INCK是37.125MHz。一幀圖像輸出固定為1125行,每行1100 INCK(29.63μs),有效輸出為1984×1105。圖像輸出的時序如圖9所示,圖10是輸出數(shù)據(jù)編碼規(guī)則。

圖9 IMX122 LVDS模式輸出時序

圖10 IMX122 12-bit 2通道輸出編碼格式

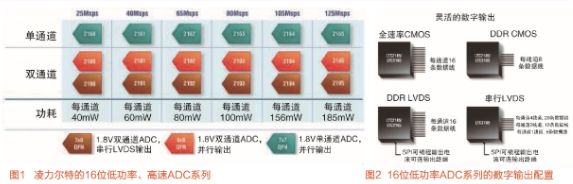

2.3 設(shè)計思路和模塊結(jié)構(gòu)

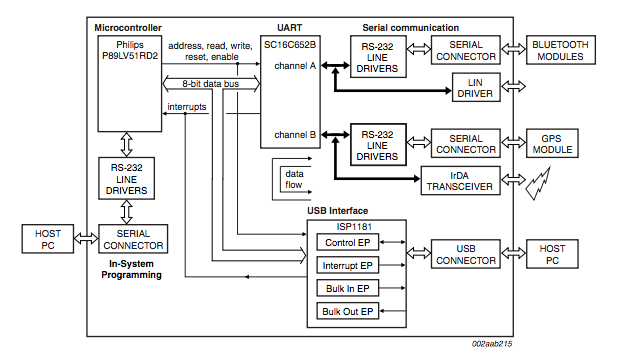

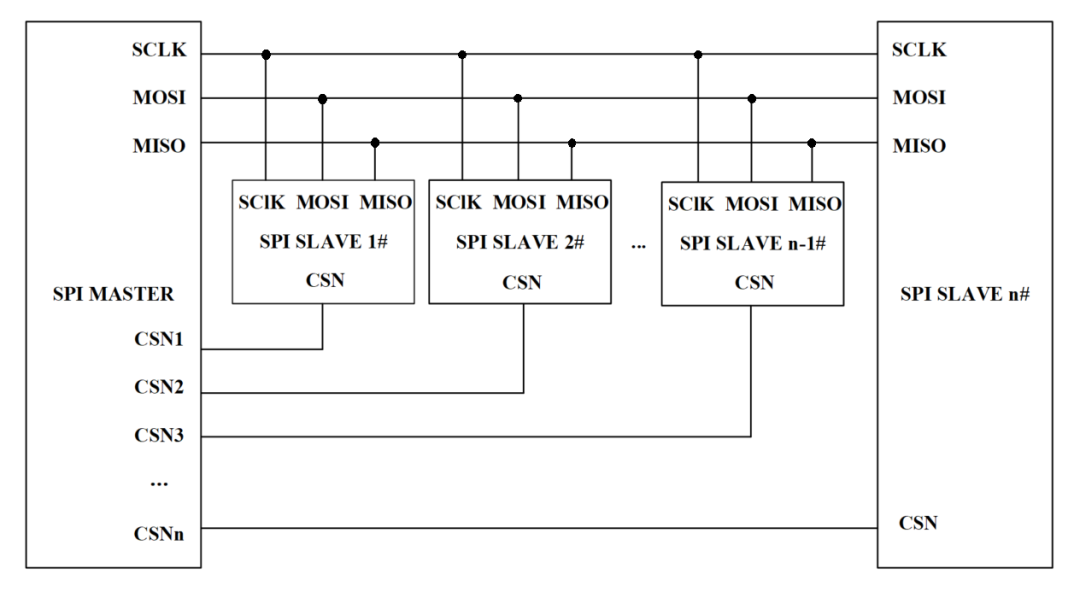

Slave模式下工作的CMOS在XVS和XHS的同步下按照固定時序穩(wěn)定輸出LVDS圖像數(shù)據(jù)。LVDS串行數(shù)據(jù)按照一定的方式進(jìn)行編碼,接收模塊應(yīng)先將串行數(shù)據(jù)解碼恢復(fù)成為并行數(shù)據(jù),再根據(jù)數(shù)據(jù)的排列方式格式化輸出。因此,整個模塊可以劃分為時序同步、LVDS接收解碼(串轉(zhuǎn)并)和數(shù)據(jù)格式化輸出三個部分。整個LVDS接收模塊的結(jié)構(gòu)如圖11所示。

圖11 LVDS接收模塊頂層圖

① CMOS輸入?yún)⒖紩r鐘(INCK)為37.125MHz;

② CMOS輸出LVDS數(shù)據(jù)為445.5MHz SDR型;

③ 時序發(fā)生器由74.25MHz發(fā)生30fps的XVS、XHS信號;

④ LVDS數(shù)據(jù)接收解碼模塊將數(shù)據(jù)恢復(fù)為8bit@55.6875MHz并行格式(DATA[7:0]);

⑤ 格式化輸出模塊通過搜索同步頭的狀態(tài)確定是否發(fā)出bit_slip,并根據(jù)CMOS的數(shù)據(jù)格式和同步信號格式化輸出12bit@74.25MHz像素數(shù)據(jù)(PIX_DATA[11:0]);

⑥ IDELAYCTRL以Ref_clk為基準(zhǔn)對整個IO BANK進(jìn)行輸入延時控制。

2.3.1 時序同步

同步時序由內(nèi)部74.25MHz計數(shù)產(chǎn)生。按照圖7所示時序即可。

2.3.2 LVDS接收解碼

LVDS接收的主要工作是將串行的數(shù)據(jù)轉(zhuǎn)為并行數(shù)據(jù)并進(jìn)行自動相位調(diào)節(jié),移位寄存器抽頭調(diào)整(Bitslip)。Xilinx Artix7系列FPGA提供串轉(zhuǎn)并模塊ISERDES和IO延時模塊IODELAYE2,ISERDES性能可在415Mb/s~1200Mb/s之間,IODELAYE2的延時參考時鐘可以是200MHz(1tap≈78ps)或300MHz(1tap≈52ps)。

(1)Artix7 FPGA時鐘特性

在Artix7系列器件里,MMCM可驅(qū)動BUFIO、BUFR、BUFH和BUFG,PLL只能驅(qū)動BUFH和BUFG。ZYNQ-7020采用Artix7 Speed-1器件,時鐘網(wǎng)絡(luò)的最高性能如下表5所示。

**表****5 Artix7 Speed-1 **器件時鐘性能

(2)LVDS接收時鐘選擇

①LVDS解碼串行參考時鐘選擇

從表1可以知道,采用BUFG最高時鐘性能為464MHz。IMX122 1080P串行模式下兩通道LVDS每通道的輸出數(shù)據(jù)率為445.5Mbps(SDR),接近BUFG的極限值,因此這里作一個變通處理,使用222.75MHz時鐘按照DDR****方式對串行數(shù)據(jù)進(jìn)行采樣。

②IODELAYE2 延時參考時鐘選擇

延時參考時鐘選擇的原則是在LVDS數(shù)據(jù)時鐘周期內(nèi),可調(diào)節(jié)的Tap數(shù)盡量的多。IMX122輸出的數(shù)據(jù)周期為2.245ns,調(diào)節(jié)一個周期采用200MHz參考時鐘需要28taps,采用300MHz參考時鐘需要43個Taps,而IODELAYE2的調(diào)節(jié)Tap數(shù)為0~31,故只能**選擇****200MHz** 的參考時鐘 。

(3)LVDS數(shù)據(jù)接收模塊時鐘

因CMOS IMX122不輸出LVDS bit時鐘,F(xiàn)PGA使用內(nèi)部時鐘來接收解碼LVDS數(shù)據(jù)。如圖12所示,與LVDS相關(guān)的時鐘由同一個MMCM產(chǎn)生以保證其相位的一致性。其中:

① 37.125MHz,為CMOS工作參考時鐘;

② 55.6875MHz,提供給IODELAYE2.C、ISERDES2.CLKDIV、補償狀態(tài)機(jī)及解碼后的字節(jié)數(shù)據(jù)參考時鐘;

③ 74.25MHz,產(chǎn)生30fps的CMOS同步參考時序和12bit像素參考時鐘;

④ 222.75MHz,以DDR模式接收的DDR位參考時鐘;

圖12 LVDS數(shù)據(jù)接收模塊結(jié)構(gòu)

IMX122輸出兩路LVDS數(shù)據(jù),每個通道的接收邏輯相同,對每一通道而言,數(shù)據(jù)流路徑如下:

a)LVDS差分對通過IBUFDS_DIFF_OUT,得到位數(shù)據(jù)(記為Master)及與其反相的數(shù)據(jù)(記為Slave);

b)Master和Slave分別進(jìn)入各自的IODELAYE2和ISERDES2得到各自的并行數(shù)據(jù)送到補償算法狀態(tài)機(jī)進(jìn)行動態(tài)相位調(diào)整并反饋各自的延時值到IODELAYE2。根據(jù)IMX122的LVDS編碼特點,ISERDES2按照1:8作串并轉(zhuǎn)換最為合適;

c)數(shù)據(jù)格式化輸出模塊根據(jù)查找Sync Code的情況調(diào)整bitslip;

d)補償模塊根據(jù)數(shù)據(jù)調(diào)整的情況輸出解碼后的8-bit并行數(shù)據(jù)。

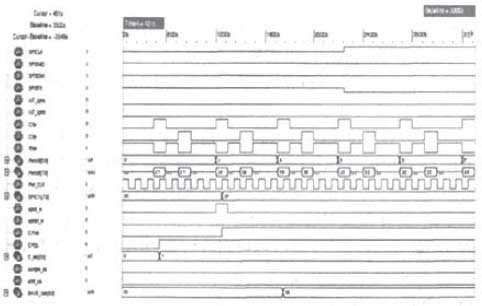

2.3.3 動態(tài)相位補償

動態(tài)相位補償原理如下:

① 初始化時,Master數(shù)據(jù)延時假定設(shè)為數(shù)據(jù)眼圖的中間位置,Slave和Master的延時相隔半個數(shù)據(jù)周期。

② 在Master和Slave的數(shù)據(jù)不全為零或不全為壹時啟動動態(tài)相位補償算法。相位補償?shù)幕驹硎牵喝绻鸐aster和Slave采樣到的數(shù)據(jù)相同,則說明采樣太靠后,延時減少一個Tap(如圖13[a]);如果Master和Slave采樣到的數(shù)據(jù)不同,則說明采樣點太靠前,延時增加一個Tap(如圖13[b])。

圖13采樣點延時示意圖

③如果延時Tap值為最小或最大位置時,則交換Master和Slave的的參考關(guān)系,同時輸出數(shù)據(jù)作相應(yīng)調(diào)整;

2.3.4 數(shù)據(jù)格式化輸出

該模塊的工作是將收到的串轉(zhuǎn)并數(shù)據(jù)的基礎(chǔ)上搜索Sync Code、并組織成12-bit的像素數(shù)據(jù)按照給定時序格式化輸出。

(1)Sync Code搜索

Sync Code搜索采用的策略是,邏輯在不停的查找在一幀數(shù)據(jù)里是否存在圖3-2所示的的特定數(shù)據(jù),如果這些同步碼都能找到,則表示接收邏輯串轉(zhuǎn)并的輸出位順序正常,不再需要bitslip;若沒有找到全部的同步碼,則在下一幀開始的時候(XVS上升沿)給出一個bitslip脈沖調(diào)整輸出,直到找到完整的Sync Code。

兩路LVDS通道分別單獨進(jìn)行Sync Code搜索,若32次bitslip 后任然沒有找到Sync Code ,則報告CMOS 輸出錯誤 。

(2)格式化輸出

格式化輸出模塊完成將CMOS輸出的數(shù)據(jù)解碼成12-bit Pixel數(shù)據(jù)并按照視頻格式時序輸出,結(jié)構(gòu)如圖14所示。

圖14 格式化輸出邏輯結(jié)構(gòu)

對格式化輸出的詳細(xì)實現(xiàn)過程這里不贅述。

2.3.5 接收模塊頂層文件描述

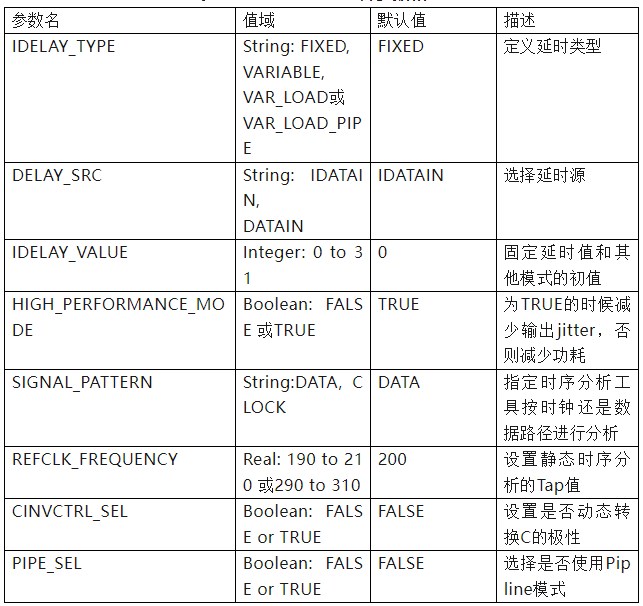

IMX122-LVDS接收模塊由4個文件構(gòu)成,分別是imx122_lvds_rev_v1_0、lvds_data_rx、rev_data_format_v1_0和imx122_slvsyn_timing_v1_0構(gòu)成,它們的層析結(jié)構(gòu)如圖15所示。

圖15 LVDS接收模塊文件結(jié)構(gòu)

注1:藍(lán)色的imx122_slvsyn_timing_v1_0不屬于LVDS接收內(nèi)容,但CMOS在SLAVE模式下必須由它提供同步信號后才能正常輸出。

電子發(fā)燒友App

電子發(fā)燒友App

評論