PCI/PCIe軟件界面

1

配置空間

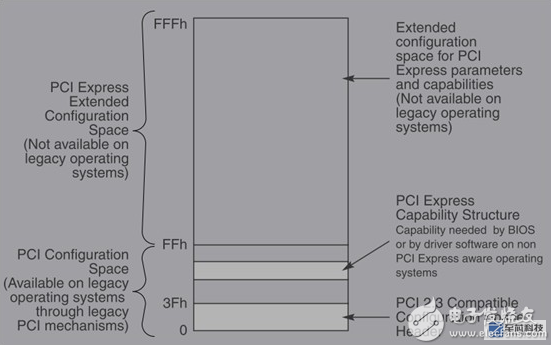

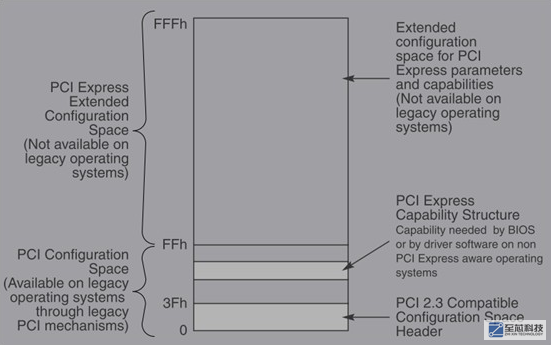

PCI spec規(guī)定了PCI設(shè)備必須提供的單獨(dú)地址空間:配置空間(configuration space),前64個(gè)字節(jié)(其地址范圍為0x000x3F)是所有PCI設(shè)備必須支持的(有不少簡(jiǎn)單的設(shè)備也僅支持這些),此外PCI/PCI-X還擴(kuò)展了0x400xFF這段配置空間,在這段空間主要存放一些與MSI或者M(jìn)SI-X中斷機(jī)制和電源管理相關(guān)的Capability結(jié)構(gòu)。

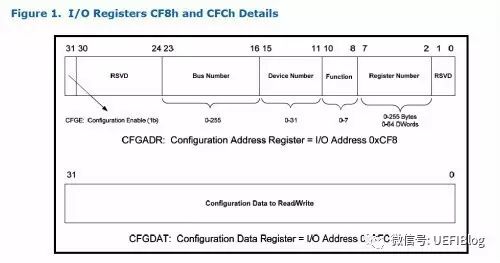

前文提到過(guò),PCI配置空間和內(nèi)存空間是分離的,那么如何訪問(wèn)這段空間呢?我們首先要對(duì)所有的PCI設(shè)備進(jìn)行編碼以避免沖突,通常我們是以三段編碼來(lái)區(qū)分PCI設(shè)備,即Bus Number, Device Number和Function Number,以后我們簡(jiǎn)稱他們?yōu)锽DF。有了BDF我們既可以唯一確定某一PCI設(shè)備。不同的芯片廠商訪問(wèn)配置空間的方法略有不同,我們以Intel的芯片組為例,其使用IO空間的CF8h/CFCh地址來(lái)訪問(wèn)PCI設(shè)備的配置寄存器:

CF8h: CONFIG_ADDRESS 。PCI配置空間地址端口。

CFCh: CONFIG_DATA 。PCI配置空間數(shù)據(jù)端口。

CONFIG_ADDRESS寄存器格式:

31 位:Enabled位。

23:16 位:總線編號(hào)。

15:11 位:設(shè)備編號(hào)。

10: 8 位:功能編號(hào)。

7: 2 位:配置空間寄存器編號(hào)。

1: 0 位:恒為“00”。這是因?yàn)镃F8h、CFCh端口是32位端口。

如上,在CONFIG_ADDRESS端口填入BDF,即可以在CONFIG_DATA上寫入或者讀出PCI配置空間的內(nèi)容。

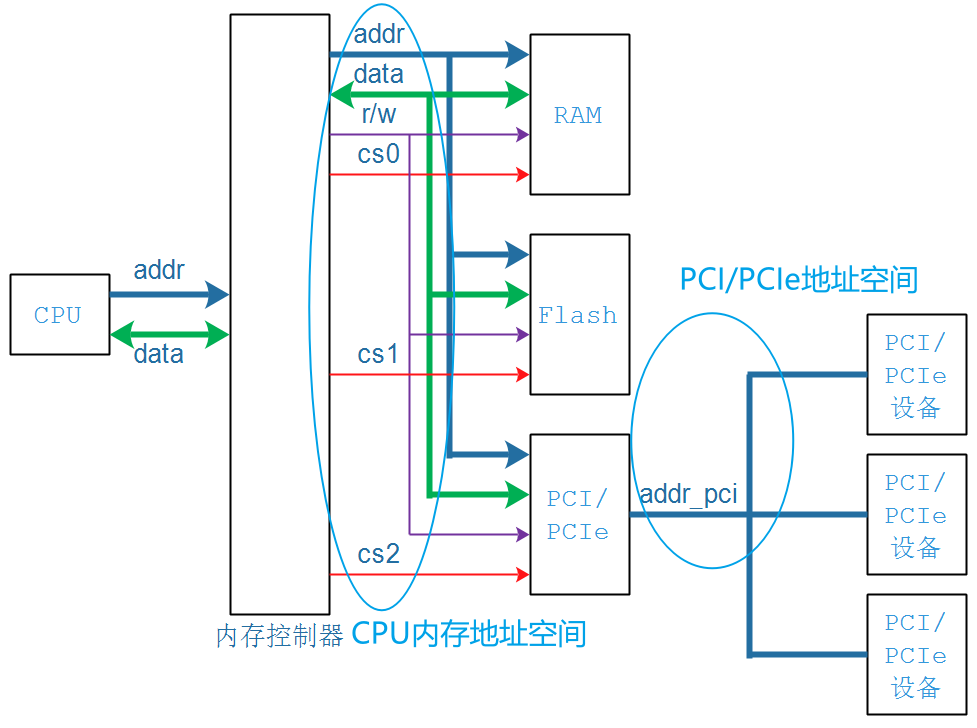

PCIe規(guī)范在PCI規(guī)范的基礎(chǔ)上,將配置空間擴(kuò)展到4KB。原來(lái)的CF8/CFC方法仍然可以訪問(wèn)所有PCIe設(shè)備配置空間的頭255B,但是該方法訪問(wèn)不了剩下的(4K-255)配置空間。怎么辦呢?Intel提供了另外一種PCIe配置空間訪問(wèn)方法:通過(guò)將配置空間映射到Memory map IO(MMIO)空間,對(duì)PCIe配置空間可以像對(duì)內(nèi)存一樣進(jìn)行讀寫訪問(wèn)了。如圖

這樣再加上PCI板子上的RAM或者ROM,整個(gè)PCIe Device空間如下圖:

MMIO這段空間有256MB,因?yàn)榘凑誔CIe規(guī)范,支持最多256個(gè)buses,每個(gè)Bus支持最多32個(gè)PCI devices,每個(gè)device支持最多8個(gè)function,也就是說(shuō):占用內(nèi)存的最大值為:256 * 32 * 8 * 4K = 256MB。在臺(tái)式機(jī)上我們很多時(shí)候覺(jué)得占用256MB空間太浪費(fèi)(造成4G以下memory可用空間變少,雖然實(shí)際memory可以映射到4G以上,但對(duì)32位OS影響很大),PCI Bus也沒(méi)有那么多,所以可以設(shè)置成最低64MB,即最多64個(gè)Bus。那么這個(gè)256MB的MMIO空間在在哪里呢?我們以Intel的Haswell平臺(tái)為例:

其中PCIEXBAR就是這個(gè)MMIO的起始位置,在4G下面占據(jù)64MB/128MB/256MB空間(4G以上部分不在本文范圍內(nèi),我們今后會(huì)詳細(xì)介紹固件中的內(nèi)存布局),其具體位置可以由平臺(tái)進(jìn)行設(shè)置,設(shè)置寄存器一般在Root complex(下文簡(jiǎn)稱RC)中。

如果大家忘記RC,可以參考前文硬件部分的典型PCIe框圖。RC是PCIe體系結(jié)構(gòu)的一個(gè)重要組成部件,也是一個(gè)較為混亂的概念。RC的提出與x86處理器系統(tǒng)密切相關(guān),PCIe總線規(guī)范中涉及的RC也以x86處理器為例進(jìn)行說(shuō)明,而且一些在PCIe總線規(guī)范中出現(xiàn)的最新功能也在Intel的x86處理器系統(tǒng)中率先實(shí)現(xiàn)。事實(shí)上,只有x86處理器才存在PCIe總線規(guī)范定義的“標(biāo)準(zhǔn)RC”,而在多數(shù)處理器系統(tǒng),并不含有在PCIe總線規(guī)范中涉及的,與RC相關(guān)的全部概念。

在x86處理器系統(tǒng)中,RC內(nèi)部集成了一些PCI設(shè)備、RCRB(RC Register Block)和Event Collector等組成部件。其中RCRB由一系列的寄存器組成的大雜燴,而僅存在于x86處理器中;而Event Collector用來(lái)處理來(lái)自PCIe設(shè)備的錯(cuò)誤消息報(bào)文和PME消息報(bào)文。RCRB的訪問(wèn)基地址一般在LPC設(shè)備寄存器上設(shè)置。

如果將RC中的RCRB、內(nèi)置的PCI設(shè)備和Event Collector去除,該RC的主要功能與PCI總線中的Host Bridge類似,其主要作用是完成存儲(chǔ)器域到PCI總線域的地址轉(zhuǎn)換。但是隨著虛擬化技術(shù)的引入,尤其是引入MR-IOV技術(shù)之后,RC的實(shí)現(xiàn)變得異常復(fù)雜。

2

BAR空間

現(xiàn)在我們來(lái)看看在配置空間里具體有些什么。我們以一個(gè)一般的type 0(非Bridge)設(shè)備為例:

其中Device ID和Vendor ID是區(qū)分不同設(shè)備的關(guān)鍵,OS和UEFI在很多時(shí)候就是通過(guò)匹配他們來(lái)找到不同的設(shè)備驅(qū)動(dòng)。為了保證其唯一性,Vendor ID應(yīng)當(dāng)向PCI特別興趣小組(PCI SIG)申請(qǐng)而得到。

我們重點(diǎn)來(lái)了解一下這些Base Address Registers(BAR)。BAR是PCI配置空間中從0x10 到 0x24的6個(gè)register,用來(lái)定義PCI需要的配置空間大小以及配置PCI設(shè)備占用的地址空間。

每個(gè)PCI設(shè)備在BAR中描述自己需要占用多少地址空間,UEFI通過(guò)所有設(shè)備的這些信息構(gòu)建一張完整的關(guān)系圖,描述系統(tǒng)中資源的分配情況,然后在合理的將地址空間配置給每個(gè)PCI設(shè)備。

BAR在bit0來(lái)表示該設(shè)備是映射到memory還是IO,bar的bit0是readonly的,也就是說(shuō),設(shè)備寄存器是映射到memory還是IO是由設(shè)備制造商決定的,其他人無(wú)法修改。

下圖是BAR寄存器的結(jié)構(gòu),分別是Memory和IO:

BAR通過(guò)將某些位設(shè)置為只讀,且0來(lái)表示需要的地址空間大小,比如一個(gè)PCI設(shè)備需要占用1MB的地址空間,那么這個(gè)BAR就需要實(shí)現(xiàn)高12bit是可讀寫的,而20-4bit是只讀且位0。地址空間大小的計(jì)算方法如下:

a. 向BAR寄存器寫全1

** b.** 讀回寄存器里面的值,然后clear 上圖中特殊編碼的值,(IO 中bit0,bit1, memory中bit0-3)。

c. 對(duì)讀回來(lái)的值去反,加一就得到了該設(shè)備需要占用的地址內(nèi)存空間。

這樣我們就可以在構(gòu)建一張大表,用于記錄所有PCI設(shè)備所需要的空間。這也是PCI枚舉的主要任務(wù)之一。另外別忘記設(shè)置Command寄存器enable這些BARs。

3

PCI橋設(shè)備

PCI橋在PCI設(shè)備樹(shù)中起到呈上起下的作用。一個(gè)PCI-to-PCI橋它的配置空間如下:

注意其中的三組綠色的BUS Number和多組黃色的BASE/Limit對(duì),它決定了橋和橋下面的PCI設(shè)備子樹(shù)相應(yīng)/被分配的Bus和各種資源大小和位置。這些值都是由PCI枚舉程序來(lái)設(shè)置的。

4

Capabilities結(jié)構(gòu)

PCI-X和PCIe總線規(guī)范要求其設(shè)備必須支持Capabilities結(jié)構(gòu)。在PCI總線的基本配置空間中,包含一個(gè)Capabilities Pointer寄存器,該寄存器存放Capabilities結(jié)構(gòu)鏈表的頭指針。在一個(gè)PCIe設(shè)備中,可能含有多個(gè)Capability結(jié)構(gòu),這些寄存器組成一個(gè)鏈表,其結(jié)構(gòu)如圖:

PCIe的各種特性如Max Payload、Complete Timeout(CTO)等等都通過(guò)這個(gè)鏈表鏈接在一起,Capabilities ID由PCIe spec規(guī)定。鏈表的好處是如果你不關(guān)心這個(gè)Capabilities(或不知道怎么處理),直接跳過(guò),處理關(guān)心的即可,兼容性比較好。

5

PCI枚舉

PCI枚舉是個(gè)不斷遞歸調(diào)用發(fā)現(xiàn)新設(shè)備的過(guò)程,PCI枚舉簡(jiǎn)單來(lái)說(shuō)主要包括下面幾個(gè)步驟:

**A. **利用深度優(yōu)先算法遍歷整個(gè)PCI設(shè)備樹(shù)。從Root Complex出發(fā),尋找設(shè)備和橋。發(fā)現(xiàn)橋后設(shè)置Bus,會(huì)發(fā)現(xiàn)一個(gè)PCI設(shè)備子樹(shù),遞歸回到A)

**B. **遞歸的過(guò)程中通過(guò)讀取BARs,記錄所有MMIO和IO的需求情況并予以滿足。

**C. **設(shè)置必要的Capabilities

在整個(gè)過(guò)程結(jié)束后,一顆完整的資源分配完畢的樹(shù)就建立好了。

7

地址譯碼

在PCI總線中定義了兩種“地址譯碼”方式,一個(gè)是正向譯碼,一個(gè)是負(fù)向譯碼。當(dāng)訪問(wèn)Bus N時(shí),其下的所有PCI設(shè)備都將對(duì)出現(xiàn)在地址周期中的PCI總線地址進(jìn)行譯碼。如果這個(gè)地址在某個(gè)PCI設(shè)備的BAR空間中命中時(shí),這個(gè)PCI設(shè)備將接收這個(gè)PCI總線請(qǐng)求。這個(gè)過(guò)程也被稱為PCI總線的正向譯碼,這種方式也是大多數(shù)PCI設(shè)備所采用的譯碼方式。

但是在PCI總線上的某些設(shè)備,如PCI-to-(E)ISA橋(或LPC)并不使用正向譯碼接收來(lái)自PCI總線的請(qǐng)求, PCI BUS N上的總線事務(wù)在三個(gè)時(shí)鐘周期后,沒(méi)有得到任何PCI設(shè)備響應(yīng)時(shí)(即總線請(qǐng)求的PCI總線地址不在這些設(shè)備的BAR空間中),PCI-to-ISA橋?qū)⒈粍?dòng)地接收這個(gè)數(shù)據(jù)請(qǐng)求。這個(gè)過(guò)程被稱為PCI總線的負(fù)向譯碼。可以進(jìn)行負(fù)向譯碼的設(shè)備也被稱為負(fù)向譯碼設(shè)備。

在PCI總線中,除了PCI-to-(E)ISA橋可以作為負(fù)向譯碼設(shè)備,PCI橋也可以作為負(fù)向譯碼設(shè)備,但是PCI橋并不是在任何時(shí)候都可以作為負(fù)向譯碼設(shè)備。在絕大多數(shù)情況下,PCI橋無(wú)論是處理“來(lái)自上游總線(upstream)”,還是處理“來(lái)自下游總線(downstream)”的總線事務(wù)時(shí),都使用正向譯碼方式。如圖:

在某些特殊應(yīng)用中,PCI橋也可以作為負(fù)向譯碼設(shè)備。PCI總線規(guī)定使用負(fù)向譯碼的PCI橋,其Base Class Code寄存器為0x06,Sub Class Code寄存器為0x04,而Interface寄存器為0x01;使用正向譯碼方式的PCI橋的Interface寄存器為0x00。

如筆記本在連接Dock插座時(shí),也使用了PCI橋。因?yàn)樵诖蠖鄶?shù)情況下,筆記本與Dock插座是分離使用的,而且Dock插座上連接的設(shè)備多為慢速設(shè)備,此時(shí)用于連接Dock插座的PCI橋使用負(fù)向譯碼。在該橋管理的設(shè)備并不參與處理器系統(tǒng)對(duì)PCI總線的枚舉過(guò)程。當(dāng)筆記本插入到Dock之后,系統(tǒng)軟件并不需要重新枚舉Dock中的設(shè)備并為這些設(shè)備分配系統(tǒng)資源,而僅需要使用負(fù)向譯碼PCI橋管理好其下的設(shè)備即可,從而極大降低了Dock對(duì)系統(tǒng)軟件的影響。

UEFI對(duì)PCI/PCIe的支持

UEFI對(duì)于PCI總線的支持包括以下三個(gè)方面:

1) 提供分配PCI設(shè)備資源的協(xié)議(Protocol)。

2) 提供訪問(wèn)PCI設(shè)備的協(xié)議(Protocol)。

3) 提供PCI枚舉器,枚舉PCI總線上的設(shè)備以及分配設(shè)備所需的資源。

4) 提供各種Lib,方便驅(qū)動(dòng)程序訪問(wèn)PCI/PCIe配置空間或者M(jìn)MIO/IO空間。

1

PCI驅(qū)動(dòng)

UEFI BIOS提供了兩個(gè)主要的模塊來(lái)支持PCI總線,一個(gè)是PCI Host Bridge控制器驅(qū)動(dòng),另一個(gè)是PCI總線驅(qū)動(dòng)。

PCI Host Bridge控制器驅(qū)動(dòng)是跟特定的平臺(tái)硬件綁定的。根據(jù)系統(tǒng)實(shí)際I/O空間和memory map,為PCI設(shè)備指定I/O空間和Memory空間的范圍,并且產(chǎn)生PCI Host Bridge Resource Allocation 協(xié)議(Protocol)供PCI總線驅(qū)動(dòng)使用。該驅(qū)動(dòng)還對(duì)HostBridge控制器下所有RootBridge設(shè)備產(chǎn)生句柄(Handle),該句柄上安裝了PciRootBridgeIoProtocol。PCI總線驅(qū)動(dòng)則利用PciRootBridgeIo Protocol枚舉系統(tǒng)中所有PCI設(shè)備,發(fā)現(xiàn)并獲得PCI設(shè)備的Option Rom,并且調(diào)用PCI Host Bridge Resource Allocation 協(xié)議(Protocol)分配PCI設(shè)備資源。PCI Host Bridge Resource Allocation協(xié)議的實(shí)現(xiàn)是跟特定的芯和平臺(tái)相結(jié)合的,畢竟只有平臺(tái)所有者才知道資源從哪里來(lái)和有多少。每一個(gè)PCI HostBridge Controller下面可以接一個(gè)或者多個(gè)PCI root bridges,PCI Root Bridge會(huì)產(chǎn)生PCI local Bus。PCI設(shè)備驅(qū)動(dòng)不會(huì)使用PCI Root Bridge I/O協(xié)議訪問(wèn)PCI設(shè)備,而是會(huì)使用PCI總線驅(qū)動(dòng)為PCI設(shè)備產(chǎn)生的PCI IO Protocol來(lái)訪問(wèn)PCI設(shè)備的IO/MEMORY空間和配置空間。PCI Root Bridge I/O協(xié)議(Protocol)是安裝在RootBridge設(shè)備的句柄上(handle),同時(shí)在該handle上也會(huì)有表明RootBridge設(shè)備的DevicePath協(xié)議(Protocol),如下圖所示

PCI總線驅(qū)動(dòng)在BDS階段會(huì)枚舉整個(gè)PCI設(shè)備樹(shù)并分配資源(BUS,MMIO和IO等),它還會(huì)在不同的枚舉點(diǎn)調(diào)用Notify event通知平臺(tái),平臺(tái)的Hook可以掛接在這些點(diǎn)上做些特殊的動(dòng)作。具體各種點(diǎn)的定義請(qǐng)參閱UEFI spec。

PCI bus驅(qū)動(dòng)在這里:https://github.com/tianocore/edk2/tree/master/MdeModulePkg/Bus/Pci/PciBusDxe

2

PCI Lib

在MdePackage下有很多PCI lib。有Cf8/CFC形式訪問(wèn)配置空間的,有PCIe方式訪問(wèn)的。都有些許不同。注意Cf8/CFC只能訪問(wèn)255以內(nèi)的,而PCIe方式訪問(wèn)的要配置正確PCIe base address PCD。

結(jié)語(yǔ)

本篇沒(méi)有介紹下列內(nèi)容,以后有機(jī)會(huì)再補(bǔ)。

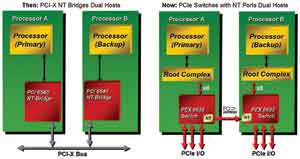

- Non-transparent bridge

- LPC

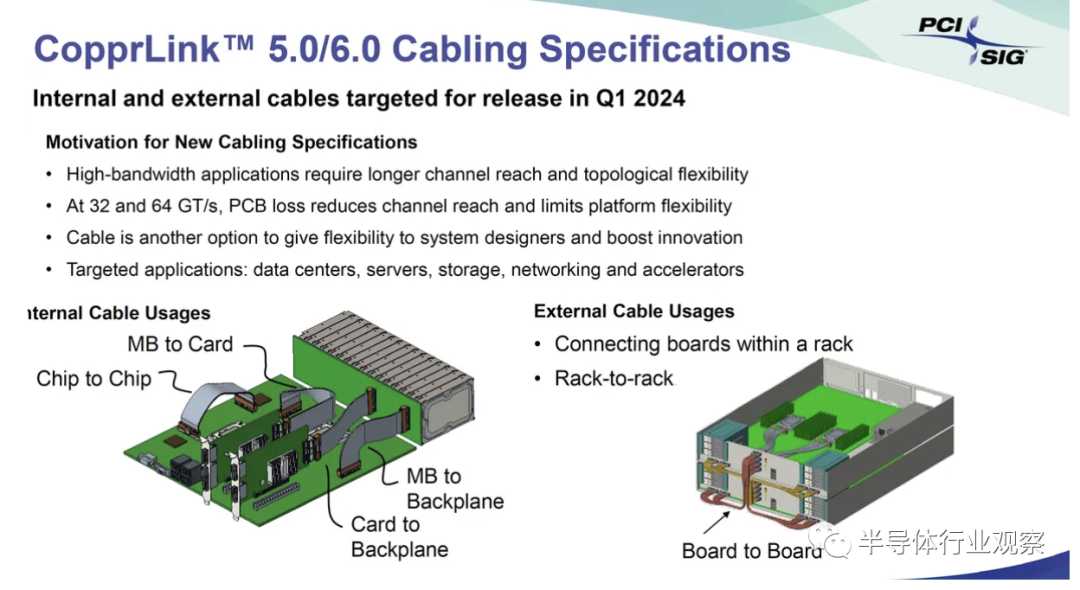

- 各種PCIe的feature

- MSI中斷處理

如果你還覺(jué)得意猶未盡,仔細(xì)思考一下下面這些問(wèn)題并找找資料有助于你更深入了解PCI/PCIe

1. 前文說(shuō)過(guò),PCIe的速度和Lane的數(shù)目是在Training的時(shí)候由Root Port和EndPoint協(xié)調(diào)得到的。那這個(gè)Training的過(guò)程發(fā)生在什么時(shí)候呢? (提示,Hard Strap,Soft Strap, Wait for BIOS/Bifurcation)。

2. UEFI PCI Bus枚舉發(fā)生在BDS階段,很靠后。那我們?nèi)绻谛酒跏蓟A段需要對(duì)PCI設(shè)備MMIO空間的寄存器甚至Bridge后面的設(shè)備做些設(shè)置,該怎么辦呢?

電子發(fā)燒友App

電子發(fā)燒友App

評(píng)論