前言

之前和大家一起學習過AXI、AHB,這次來一起對Soc中的總線有個宏觀的學習。

總線提供了系統中各個設備之間一種互連的訪問共享硬件機制。

在數字系統中,總線承擔數據傳輸的任務如處理器和存儲器之間的數據傳輸。

總線的傳輸能力由總線的寬度和工作頻率決定。

總線的設計通常要考慮4個因素:

?總線寬度、?時鐘頻率、?仲裁機制、?傳輸類型。

總線連接的設備根據功能不同分為總線主設備和從設備。

?總線主設備可以發起一個傳輸任務?而從設備則對主設備發起的事務做出回應。

?有些設備既可以是總線的主設備,也可以是總線的從設備,如DMA控制器等。當總線上存在多個主設備時,這些主設備有可能在一段時間內同時需要競爭使用總線。

?這時需要一種仲裁機制來決定總線的使用。仲裁機制的差異會影響總線的利用效率和任一總線主設備所見到的遲滯。使用較多的仲裁機制有輪詢機制和按照優先級順序機制。

?在輪詢機制中,仲裁邏輯循環檢查各個主設備的使用請求,從而決定哪一個主設備使用總線,每個總線的主設備擁有相同的優先級,但重要的請求可能需要等待較大的延時后才能獲得總線的控制權。

?在按照優先級順序的仲裁機制中,各個主設備分配不同的優先級。在這種設計中,優先級高的主設備可以在較少延時下獲得總線的使用權。在仲裁機制中,有必要啟用某些保護機制,確保總線傳輸的正常進行。

例如,在傳輸數據過程中采用鎖定的機制,只有當前傳輸結束后才能重新啟動仲裁機制,確保該次傳輸的正常結束。這在多個主設備競爭訪問同一個資源時可以確保數據傳輸的正確性。

總線在傳輸數據時,可以采用不同的傳輸類型以適應不同的數據傳輸要求。在大多數總線中可以實現固定大小的數據塊傳輸和可變大小的數據塊傳輸。更加復雜和先進的總線行為還包括分離處理(Split Transactions)、原子處理(Atomic Transactions)等。

當從設備需要比較長的時間處理主設備的數據傳輸時,可以將總線的控制權交給其他主設備。當該從設備完成數據的處理后,從設備通知主設備可以繼續上次沒有完成的數據傳輸。

目前,各大IP提供商都先后推出了自己的總線標準。較有影響力的片上總線標準有ARM公司的AMBA總線、IBM公司的CoreConnect總線、Silicore Corp的Wishbone總線和Altera的Avalon總線等。

SoC設計的一個重要特點是基于IP核的復用。

為解決眾多IP核復用的問題需要一個快速的連接方案,由此產生了開放核協議(OCP)。

OCP是由OCP-IP組織定義的一種標準化的IP 核接口(Interface)或插座(Socket),以便任何帶有這一接口的IP都可以在SoC內直接點對點的連接,或通過帶有這一標準接口的總線進行互連。

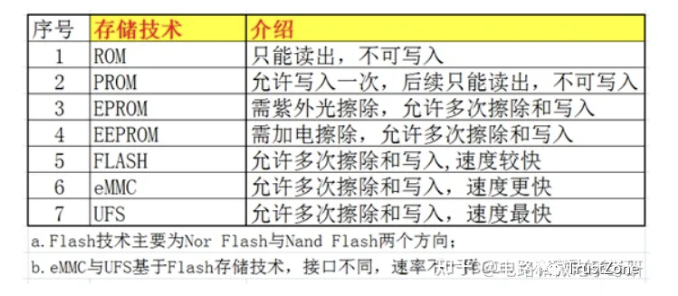

1 AMBA總線

AMBA總線是ARM公司開發的片上總線標準,目前已經到了3.0版本。AMBA總線標準包括

?AHB(Advanced High-performance Bus)總線、

?ASB (Advanced System Bus)總線、

?APB(Advanced Peripheral Bus)總線

?AXI總線

AHB和ASB總線連接高性能系統模塊,ASB是舊版本的系統總線,使用三態總線,目前已被新版本的AHB總線所代替。AHB是AMBA2.0標準。

而AXI是最新推出的新一代AMBA3.0標準。

APB總線連接低速的外圍設備。

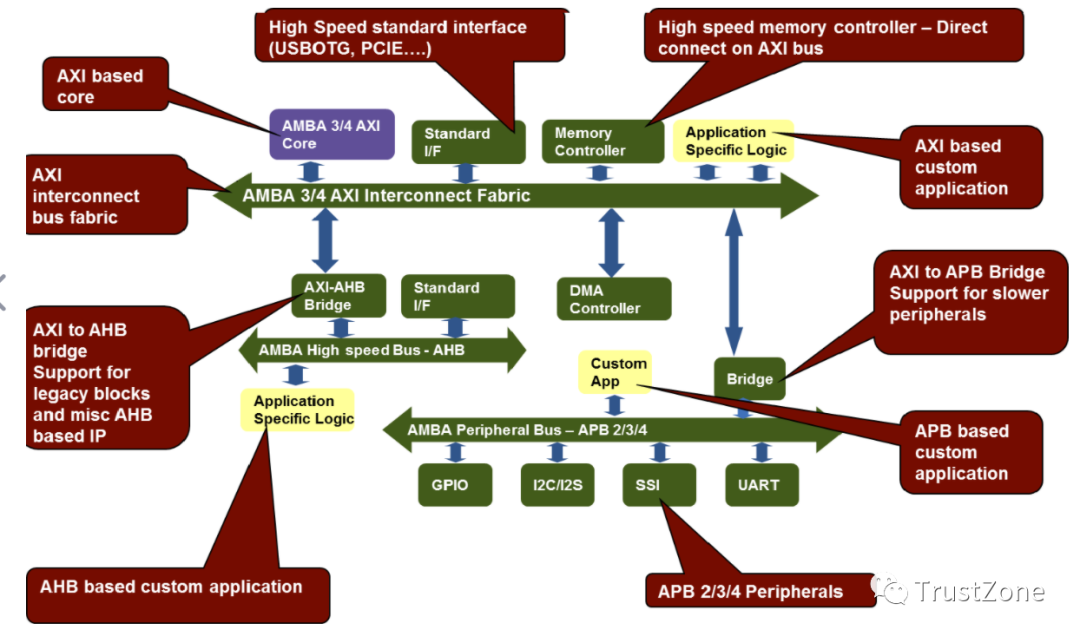

典型的AMBA系統結構如所示。

?

AHB總線連接的系統模塊有處理器、DMA控制器、片內存儲器、外部存儲器接口、LCD控制器等。

這些設備往往工作在較高時鐘頻率下,對系統的性能有較大影響。

AHB總線支持仲裁、突發傳輸、分離傳輸、流水操作、多主設備等復雜事務。

APB總線連接的外圍設備有UART接口、鍵盤、USB接口、鍵盤接口、時鐘模塊等。

APB沒有復雜事務實現,非流水線操作,可達到減少功耗和易于使用的目的。

最近幾年,隨著超大規模SoC的興起,嵌入式系統的性能需求越來越高,導致對片上總線的帶寬要求也越來越苛刻。雖然AHB總線的協議在理論上可以讓用戶不斷地增加總線位寬從而達到更大的帶寬,但是在節省功耗的前提下,用戶希望通過極小的總線寬度、極低的總線頻率來實現很高的數據吞吐量,也就是對協議傳輸效率的要求達到極致。

順應這種趨勢,ARM在2004年推出了AMBA3.0-AXI協議。AXI總線是一種多通道傳輸總線,將地址、讀數據、寫數據、握手信號在不同的通道中發送,不同訪問之間的順序可以打亂,用BUSID來表示各個訪問的歸屬。

Master在沒有得到返回數據的情況下可以發出多個讀寫操作。讀回的數據順序可以被打亂,同時還支持非對齊數據訪問。由于各個傳輸之間僅依靠傳輸ID來相互識別,沒有時序上的依賴關系,所以可以被插入寄存器來打斷限制頻率的關鍵路徑。那么從理論上講,AXI協議就沒有頻率上限了。

AXI總線還定義了在進出低功耗節電模式前后的握手協議。規定如何通知進入低功耗模式,何時關斷時鐘,何時開啟時鐘,如何退出低功耗模式。

這使得所有IP在進行功耗控制的設計時,有據可依,容易集成在統一的系統中。圖4-3所示為一種典型的基于AMBA 3 AXI總線協議的SoC結構實例。

AXI不僅繼承了AHB便于集成、便于實現和擴展的優點,還在設計上引入了指令亂序發射、結果亂序寫回等重大改進,使總線帶寬得到最大程度的利用,可進一步滿足高性能系統的大量數據存取的需求。

【AHB與AXI、APB的區別與聯系】[1]

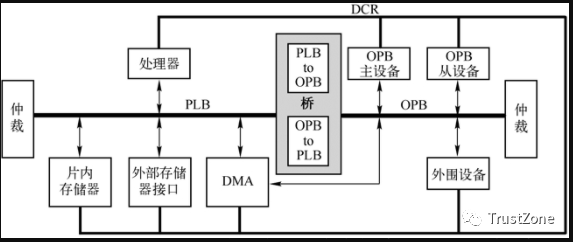

2 CoreConnect總線

CoreConnect是IBM開發的一套片上系統總線標準。CoreConnect總線包括

?PLB(Procesor Local Bus)總線、

?OPB(On-Chip Peripheral Bus)總線、

?DCR(Device Control Register)總線。

圖4-4所示為CoreConnect的總線結構圖。

在CoreConnect總線中,

?PLB總線連接高性能設備如處理器、存儲器接口、DMA等。

?OPB總線連接低性能設備,如各種外圍接口等。OPB總線減少了外圍設備對于PLB性能的影響。在PLB和OPB之間存在一個轉接的總線橋。PLB到OPB總線橋實現了PLB總線上主設備到OPB總線上從設備的數據傳輸。它在PLB總線上是從設備,但在OPB總線上卻成為主設備。與之相對應,OPB到PLB的橋在OPB上是從設備,但會作為PLB總線的主設備,實現OPB總線上的主設備到PLB總線的從設備的數據傳輸。

?DCR總線主要用來訪問和配置PLB和OPB總線設備的狀態和控制寄存器。DCR總線結構實現了在PLB或OPB傳輸之外的數據傳輸。在PLB或OPB總線上的主設備都需要經過總線仲裁設備來獲取對于總線的控制權。

3 Wishbone總線

Wishbone總線是由Silicore公司推出的片上總線標準。這種總線具有簡單、靈活和開放的特點,現在已經被OpenCores采用并組織維護。

在AMBA或CoreConnect總線中,高速設備和低速設備分別在不同的總線上。

而在Wishbone中,所有核都連接在同一標準接口上。

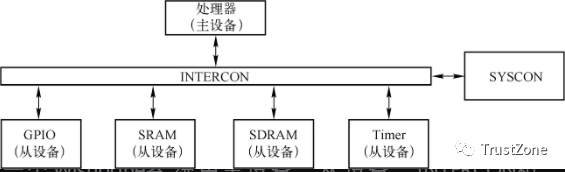

當需要時,系統設計者可以選擇在一個微處理器核上實現兩個接口,一個給高速設備,另一個給低速設備。Wishbone總線的結構如圖4-5所示。

一個Wishbone系統由主設備、從設備、INTERCON和SYSCON組成。

其中INTERCON定義了主設備和從設備之間的連接方式,而SYSCON用來產生系統時鐘和復位信號。

在Wishbone中有4種不同的連接方式可以使用,它們分別是點對點、數據流、共享總線和交叉連接方式。

4 AVALON總線

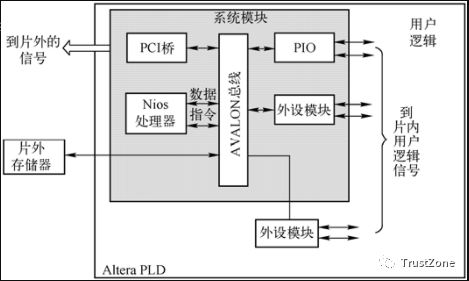

AVALON總線主要應用在FPGA中,作為SOPC(System On a Programmable Chip)中的片上總線。AVALON總線是Altera推出Nios核時開發的片上總線,系統結構如圖4-6所示。

在AVALON總線中,主設備之間通過仲裁機制決定是否獲得總線的控制權。

5 開放核協議

IP在SoC中的互連概括起來可以通過兩種方案解決,一種是采用標準的總線結構(如AMBA),另一種是定義一種通用的總線接口,而不限制總線的采用。

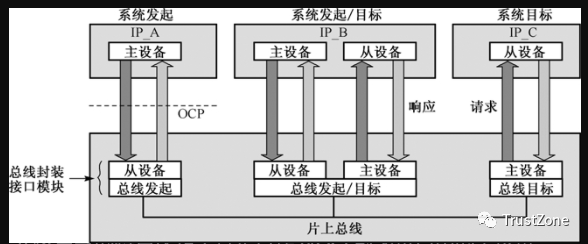

開放核協議(OCP,Open Core Protocol)是由OCP-IP組織定義的IP互聯協議。

它不是總線定義,而是在IP核之間的一種獨立于總線之外的高性能接口規范,這種方法提高了IP的重用率,進而可以減少設計時間、設計風險和制造成本。

一個IP核可以是處理器、外圍設備或片上總線。

OCP在兩個通信實體之間定義了點到點的接口。這兩個通信實體中,一個作為主設備,可以發起命令;另一個作為從設備,對主設備的命令做出回應。

該OPC結構如圖4-7所示。OCP是在國際IP標準組織(VISA)的虛擬接口標準VCI上的擴展。

OCP-IP組織還相繼開發了相應的IP接口自動生成工具,并提供一定的技術支持,使得OCP接口具有更好的實用價值。

IP核自身的特點決定了其是否作為OCP封裝接口中的主設備、從設備或兩者都是。

總線封裝接口模塊作為OCP的補充。在系統的數據傳輸過程中,系統的發起者(OCP主設備)輸出命令和數據到總線封裝接口模塊。

OCP并不規定總線的功能。總線封裝接口模塊設計中,需要將OCP請求轉換成總線傳輸。

OCP主設備負責將總線傳輸轉換成合法的OCP命令;OCP從設備接收主設備發出的命令,并做出回應。

6 復雜的片上總線結構

以上分析了目前使用較為廣泛的幾種標準總線結構。在實際的使用中,尤其在一些復雜的SoC設計中,往往會在這些總線協議的基礎上采用更加復雜的總線結構以滿足處理器、存儲器和其他與之相連的設備之間的相互矛盾。

下面以AMBA總線為例,分析兩種較為常見的總線結構。

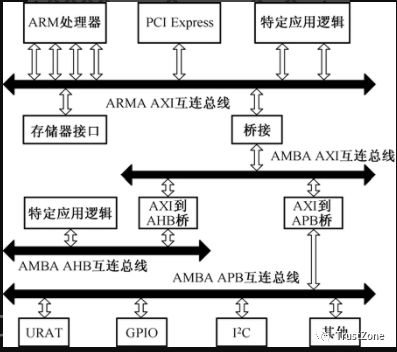

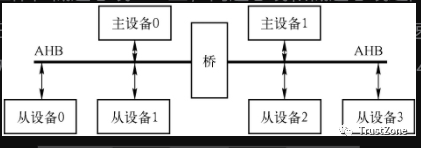

在AMBA總線中,高性能設備工作在高速總線AHB上,其他慢速設備工作在低速總線APB上,高速總線和低速總線之間通過橋連接在一起。

當高速總線上的設備比較多時,一條高速總線的設計無法滿足系統的要求,這時需要增加總線,如圖4-8所示。

在這種設計中,兩種總線主設備分別工作在不同的AHB總線上,但它們都可以訪問所有從設備。這樣兩個主設備在分別訪問本地總線的從設備時可以減少總線上的等待時間,提高總線的訪問效率。

當主設備訪問相鄰總線的從設備時需要通過總線橋進行,在這種設計中一般主設備訪問相鄰總線從設備的可能性較小。

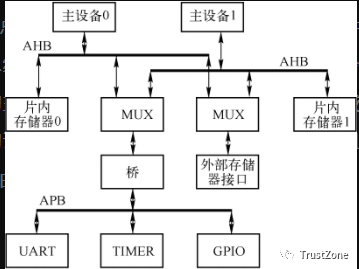

更加復雜的總線結構如圖4-9所示,在這種總線結構中,不但有兩條高速總線還有一條低速總線。

兩個片內存儲器分別只能由該總線上的主設備訪問。

兩個主設備對于低速總線或片外存儲器有共同的訪問權限,這時候需要增加總線的仲裁機制來決定在某個時刻由哪個主設備來訪問相應的從設備。

來源:TrustZone

審核編輯:劉清

電子發燒友App

電子發燒友App

評論