請(qǐng)教:我在使用c6678開發(fā)板,想使用邊界掃描測(cè)試的功能,不知道除了開發(fā)板硬件之外,是不是還需要其他硬件和軟件的配合?

2018-06-19 07:36:16

邊界掃描測(cè)試技術(shù) 不屬于 coresight架構(gòu),邊界掃描測(cè)試技術(shù) 被 coresight 架構(gòu) 使用.綜述聯(lián)合測(cè)試行動(dòng)組(Joint Test Action Group,簡(jiǎn)稱 JTAG)提出了邊界

2022-02-17 07:33:41

邊界掃描測(cè)試技術(shù)簡(jiǎn)介及原理 1. 簡(jiǎn)介 JTAG(Joint Test Action Group,聯(lián)合測(cè)試行動(dòng)小組)是1985年制定的檢測(cè)PCB和IC芯片的一個(gè)

2009-10-15 09:32:16

我用AVR單片機(jī)寫了一個(gè)邊界掃描的程序,用于檢測(cè)帶JTAG的器件。在調(diào)試程序的過(guò)程中遇到了一些問(wèn)題,不知有誰(shuí)對(duì)邊界掃描有過(guò)研究,可以幫我解決這些問(wèn)題。硬件:MEGA16,使用內(nèi)部8M時(shí)鐘,作控制器

2013-06-01 16:47:08

有做過(guò)邊界掃描控制器的大神嗎?想問(wèn)一下sn74act8990這個(gè)芯片有沒有人用過(guò)啊,怎么使用,謝謝啦

2017-07-10 17:50:00

本章介紹了 Cyclone? IV 器件所支持的邊界掃描測(cè)試 (BST) 功能。這些 BST 功能與Cyclone III 器件中的相類似,除非另有說(shuō)明。Cyclone IV 器件 (Cyclone

2017-11-14 10:50:26

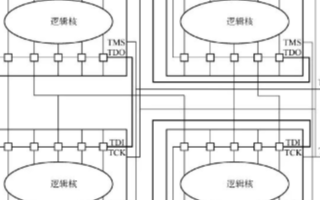

請(qǐng)教大家一個(gè)問(wèn)題,板子上有兩個(gè)FPGA,想用一個(gè)PROM配置,將PROM和兩個(gè)FPGA用邊界掃描下載方式連起來(lái)可以嗎? 就是下圖這種模式,可不可以再多串一個(gè)FPGA呢?

2014-03-24 15:53:09

FX3支持IEEE1149的邊界掃描測(cè)試嗎? 以上來(lái)自于百度翻譯 以下為原文Does the FX3 support boundary scan testing according to IEEE1149?

2019-01-24 12:59:15

我正在使用 IMX8m Plus 構(gòu)建定制板,我想使用邊界掃描來(lái)測(cè)試板的連接。為此,我正在 (8MPLUSLPD4-EVK) 上進(jìn)行試驗(yàn),以檢查 JTAG 連接以及進(jìn)入邊界掃描模式需要執(zhí)行的操作。我

2023-03-29 06:05:21

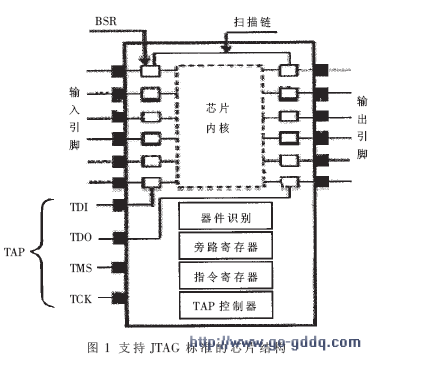

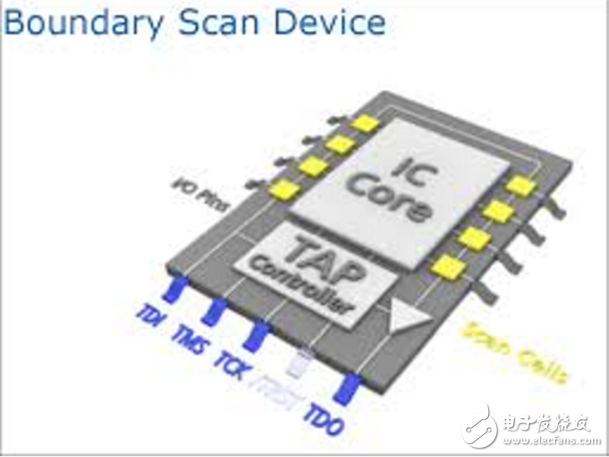

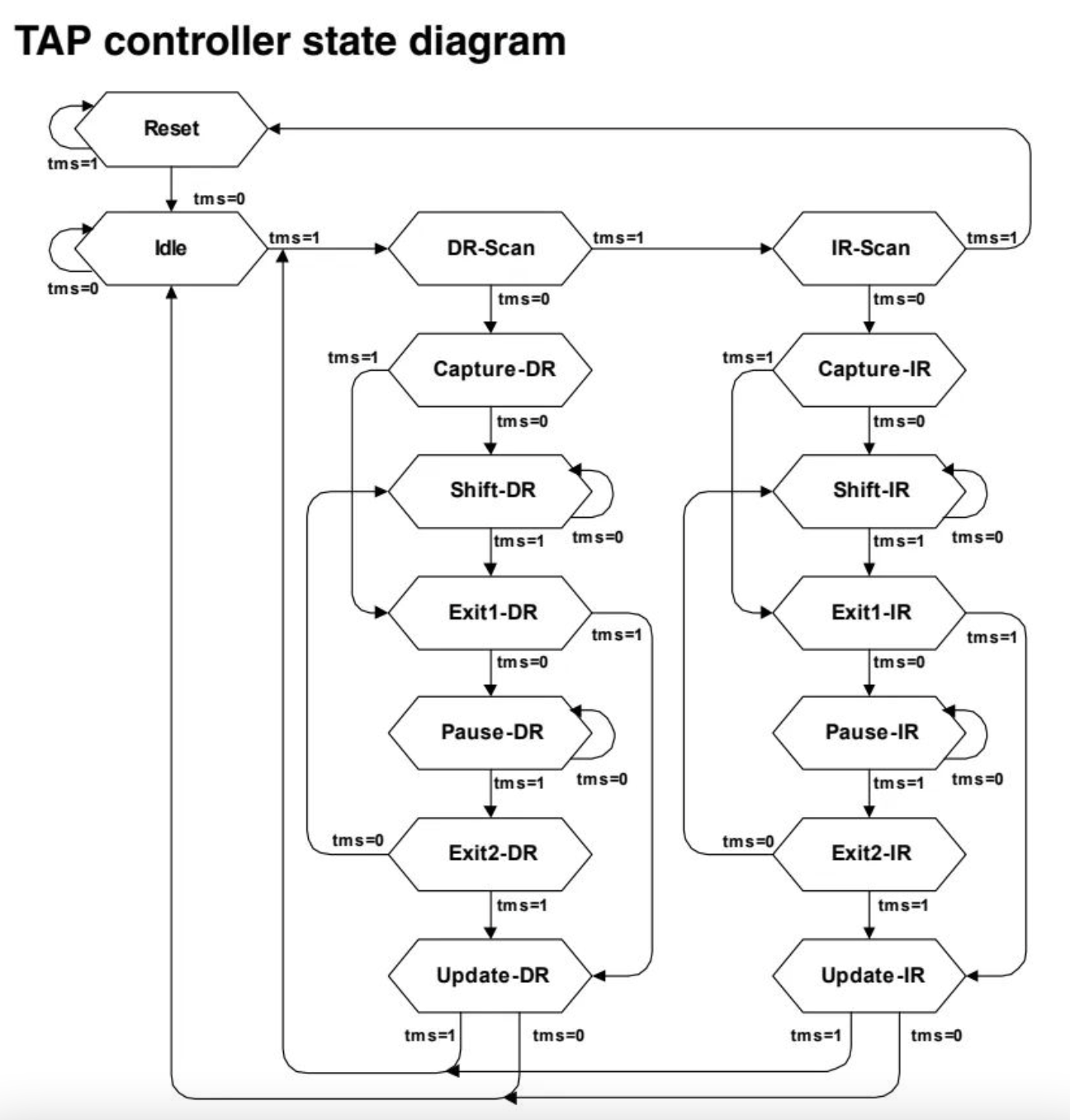

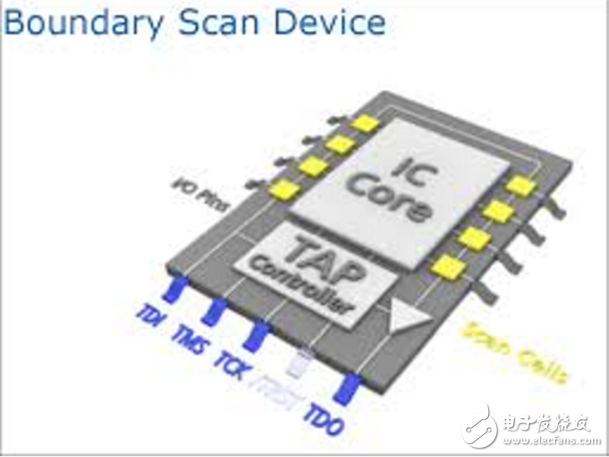

可以歸結(jié)為:在器件內(nèi)部定義一個(gè)TAP(Test Access Port,測(cè)試訪問(wèn)口),通過(guò)專用的JTAG測(cè)試工具對(duì)內(nèi)部節(jié)點(diǎn)進(jìn)行測(cè)試和調(diào)試。首先介紹一下邊界掃描和TAP的基本概念和內(nèi)容。1. 邊界掃描

2012-03-01 09:26:05

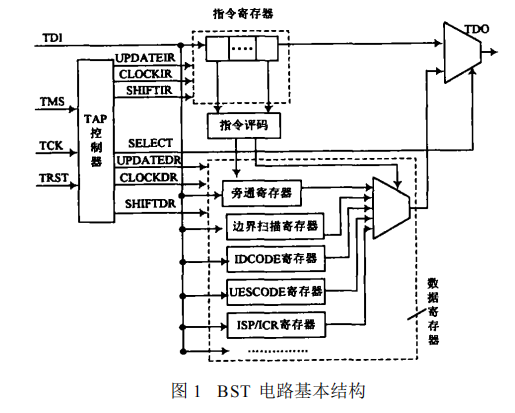

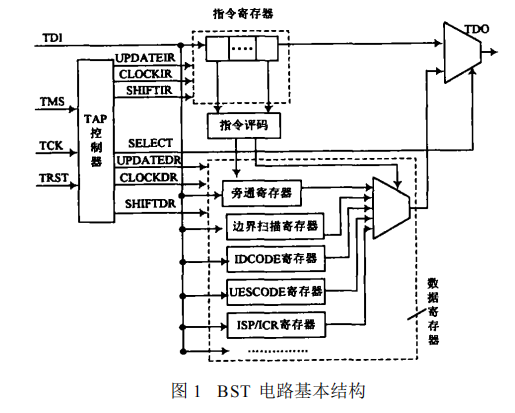

。現(xiàn)在一種新的測(cè)試技術(shù)——邊界掃描測(cè)試技術(shù)已逐步得到發(fā)展,大多數(shù)的ASIC電路和許多中等規(guī)模的設(shè)備已開始利用邊界掃描測(cè)試技術(shù)進(jìn)行設(shè)計(jì)。BST技術(shù)是按照IEEE1149.1標(biāo)準(zhǔn),提供了一套完整的測(cè)試方案。在

2018-09-10 16:50:00

和 RK3399 相似應(yīng)該是個(gè) M 核,很可能用作管理單元?串行 SW 調(diào)試口說(shuō)是主 APU 的,沒問(wèn)題。完整的 JTAG 是否有物理引腳邊界掃描能力?SW 天生為 1 對(duì) 1,無(wú)法在板級(jí)串聯(lián),肯定

2023-01-06 15:15:24

使用64bit(labtools)沖擊初始化邊界掃描中的鏈時(shí),彈出一個(gè)錯(cuò)誤對(duì)話框,說(shuō)沒有找到電纜,請(qǐng)檢查電纜設(shè)置。所以現(xiàn)在我卸載了xilinx 14.7并安裝了vivado 2015.3,在此我沒有發(fā)現(xiàn)影響64位來(lái)初始化邊界掃描中的鏈。請(qǐng)建議我如何處理。謝謝,Jeeva J.

2020-04-09 06:16:25

允許加載位文件,則相同的測(cè)試失敗。什么是配置V5可以殺死我的邊界掃描測(cè)試,其他所有東西保持相同?我認(rèn)為一旦芯片處于JTAG“測(cè)試模式”,邊界掃描寄存器就可以完全控制每個(gè)接口引腳。注意:我知道芯片成功處于測(cè)試模式,因?yàn)槲铱梢杂^察輸出引腳與邊界掃描的輸出數(shù)據(jù)之間的切換。

2020-06-03 14:06:20

摘要:本文設(shè)計(jì)了一套基于邊界掃描的電路板快速測(cè)試系統(tǒng),該系統(tǒng)利用計(jì)算機(jī)并行端口,通過(guò)適配器發(fā)送、接收測(cè)試向量,然后對(duì)采集數(shù)據(jù)進(jìn)行分析,顯示測(cè)試結(jié)果。本文主要介紹了該系統(tǒng)的硬件結(jié)構(gòu)、軟件思想和診斷

2018-09-10 16:28:11

嗨,大家好,是否有“白癡指南”如何為第三方設(shè)置Zynq 7000系列進(jìn)行邊界掃描?我有一個(gè)測(cè)試工作,但我得到間歇性的測(cè)試結(jié)果取決于Zynq在其啟動(dòng)過(guò)程中的位置。我的希望是將Zynq置于一個(gè)“自由切換

2019-04-17 08:56:32

我嘗試使用 Goepel 的 Cascon 為 LS1027 設(shè)置邊界掃描。合規(guī)性模式按照 BSDL 文件中的描述進(jìn)行設(shè)置。ID 寄存器是可訪問(wèn)的,我可以讀取正確的 ID。如果我切換到 SAMPLE

2023-03-31 06:52:45

邊界掃描是什么原理?如何利用FPGA作為載體來(lái)實(shí)現(xiàn)邊界掃描故障診斷儀的SOPC系統(tǒng)?

2021-04-12 06:07:03

一種基于多線程掃描的網(wǎng)絡(luò)拓?fù)?b class="flag-6" style="color: red">邊界監(jiān)測(cè)系統(tǒng)設(shè)計(jì)

2021-05-20 07:12:26

我想使用邊界掃描測(cè)試在 STM32F407VG 發(fā)現(xiàn)板上測(cè)試差分信號(hào)。我知道這個(gè) soc 支持邊界掃描測(cè)試,但是否也可以通過(guò)相同的方式測(cè)試/測(cè)量差分信號(hào)?

2023-01-31 08:28:49

嵌入式邊界掃描是什么?嵌入式邊界掃描系統(tǒng)主要有哪些結(jié)構(gòu)?怎樣去實(shí)現(xiàn)嵌入式邊界掃描系統(tǒng)?

2021-04-15 07:01:49

怎樣才能使JTAG邊界掃描與功能測(cè)試相結(jié)合

2021-05-06 07:56:42

現(xiàn)在打算使用新唐M451LG6AE芯片設(shè)計(jì)產(chǎn)品,因?yàn)樵诋a(chǎn)品生產(chǎn)后需要經(jīng)過(guò)ICT測(cè)試,ICT又需要使用芯片的邊界掃描功能。但是在手冊(cè)中沒有找到關(guān)于邊界掃描的描述,也不知道應(yīng)該預(yù)留哪幾個(gè)引腳來(lái)支持邊界掃描。

2023-06-26 06:15:37

各位大俠,有誰(shuí)了解邊界掃描工具的嚒?這個(gè)前景怎么樣?

2012-06-11 21:34:54

大家好,我正在使用 STM32F407G-DISC1 開發(fā)板。我有 ST-Link V2 外部調(diào)試器(我附上了哪個(gè)圖像),因?yàn)槲也幌胧褂冒遢d調(diào)試器。我想進(jìn)行邊界掃描測(cè)試。你能建議我有沒有免費(fèi)的工具可用于 STM32F4 進(jìn)行邊界掃描測(cè)試。

2023-01-31 08:33:02

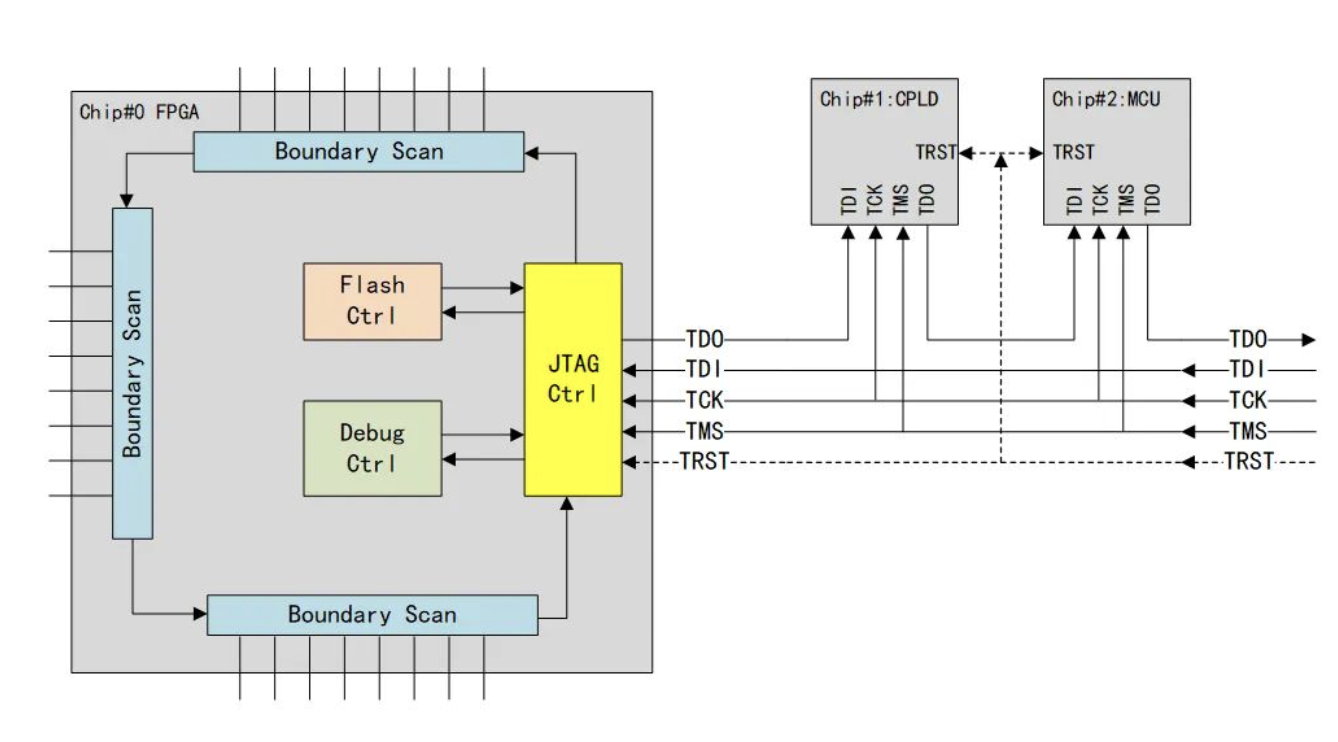

本文介紹支持JTAG標(biāo)準(zhǔn)的IC芯片結(jié)構(gòu),并以Xilinx公司的兩塊xc9572_ pc84芯片為例,探討并利用邊界掃描技術(shù)控制IC芯片處于某種特定功能模式的方法,并且針對(duì)IC芯片某種特定的功能模式設(shè)計(jì)該芯片的JTAG控制器。

2021-04-30 06:05:17

請(qǐng)問(wèn)T4081NSE7TTB是否支持1149.1邊界掃描?如果是的話,我可以有這個(gè)處理器的 bsdl 文件嗎?

2023-03-27 07:10:24

_ * Nutshell中的邊界掃描* _ ICT測(cè)試需要“測(cè)試訪問(wèn)”。這是指設(shè)計(jì)到PCB中的測(cè)試點(diǎn)(通常是焊盤或過(guò)孔),探針可以連接到測(cè)試點(diǎn)以提供被測(cè)板和測(cè)試儀之間的電氣連接。該測(cè)試標(biāo)準(zhǔn)由一個(gè)公司

2019-07-01 09:31:59

測(cè)試,從而利用JTAG邊界掃描架構(gòu)測(cè)試高速系統(tǒng)級(jí)芯片(SoC)的互連上發(fā)生的時(shí)延破壞。ALT="圖1:信號(hào)完整性故障模型。"> 互連中的信號(hào)完整性損耗對(duì)于數(shù)千兆赫茲高度

2009-10-13 17:17:59

分析邊界掃描測(cè)試技術(shù)的工作機(jī)制和對(duì)測(cè)試支撐系統(tǒng)的功能需求,提出一種基于USB總線的高速邊界掃描測(cè)試主控器的設(shè)計(jì)方案。利用CY7C68013作為USB2.0接口控制器,使用CPLD實(shí)現(xiàn)JTAG主控

2009-04-03 08:43:25 17

17 通過(guò)JTAG 實(shí)現(xiàn)對(duì)Flash 在線編程。首先, 介紹JTAG 的定義、結(jié)構(gòu)及引腳的定義, 并闡述JTAG 狀態(tài)機(jī)的工作原理。然后,介紹JTAG口的邊界掃描寄存器,給出實(shí)現(xiàn)JTAG在線寫Flash的電路, 和

2009-04-16 10:00:04 59

59 本文提出將廣泛用于測(cè)試領(lǐng)域的邊界掃描技術(shù)應(yīng)用在基于FPGA的計(jì)算機(jī)硬件實(shí)驗(yàn)課程中,利用邊界掃描技術(shù)解決FPGA的配置和測(cè)試兩大關(guān)鍵問(wèn)題。在PC機(jī)上編寫邊界掃描主控器的C語(yǔ)

2009-08-18 10:10:21 17

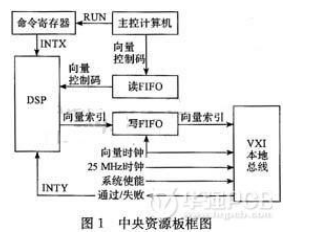

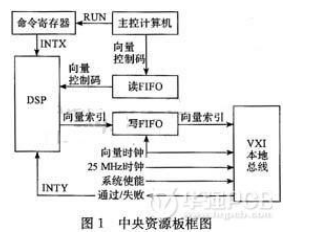

17 XI邊界掃描模塊接口電路的設(shè)計(jì):根據(jù)IEEE1149.X標(biāo)準(zhǔn)和VXI總線規(guī)范,采用EDA技術(shù)對(duì)VXI邊界掃描模塊的接口電路進(jìn)行了研究和設(shè)計(jì),通過(guò)仿真和實(shí)際測(cè)試驗(yàn)證了設(shè)計(jì)的正確性,很好地

2009-10-10 14:43:06 29

29 介紹了支持JTAG 標(biāo)準(zhǔn)的數(shù)字集成電路(IC)芯片結(jié)構(gòu)、故障測(cè)試模式和運(yùn)用邊界掃描故障測(cè)試的原理。實(shí)驗(yàn)中分析了數(shù)字IC 互連故障類型、一般故障診斷流程和互連故障的

2009-11-14 09:01:51 12

12 根據(jù)系統(tǒng)級(jí)邊界掃描測(cè)試技術(shù)的應(yīng)用需求,基于VXI總線的多功能邊界掃描測(cè)試控制器具備三種操作模式:IEEE1149.1 TAP模式、IEEE1149.5主控制器模式和從控制器模式。由上位機(jī)控制模件

2009-12-05 16:27:27 26

26 應(yīng)用于FPGA的邊界掃描設(shè)計(jì)蔣曉(中國(guó)電子科技集團(tuán) 38 研究所,合肥230031)摘要:針對(duì)在FPGA芯片中的應(yīng)用特點(diǎn),設(shè)計(jì)了一種邊界掃描電路,應(yīng)用于自行設(shè)計(jì)的FPGA新結(jié)構(gòu)之中

2009-12-14 11:27:14 22

22 本文設(shè)計(jì)了一套基于邊界掃描的電路板快速測(cè)試系統(tǒng),該系統(tǒng)利用計(jì)算機(jī)并行端口,通過(guò)適配器發(fā)送、接收測(cè)試向量,然后對(duì)采集數(shù)據(jù)進(jìn)行分析,顯示測(cè)試結(jié)果。本文主要介紹了

2010-01-20 11:35:57 20

20 JTAG邊界掃描技術(shù)設(shè)計(jì)方案

JTAG(Joint Test Action Group�聯(lián)合測(cè)試行動(dòng)小組)是一種國(guó)際標(biāo)準(zhǔn)測(cè)試協(xié)議IEEE 1149.1兼容),主要用于芯片內(nèi)部測(cè)試。現(xiàn)在多數(shù)的高級(jí)器

2010-03-04 14:40:05 29

29 摘要:本文介紹了支持JTAG標(biāo)準(zhǔn)的IC芯片結(jié)構(gòu)、以PC機(jī)作平臺(tái),針對(duì)由兩塊Xilinx公司的xc9572一pc84芯片所互連的PCB板,結(jié)舍邊界掃描技術(shù),探討了芯片級(jí)互連故障的測(cè)試與診斷策略。體

2010-05-14 09:00:17 13

13 分析了用于模數(shù)混合電路的邊界掃描測(cè)試技術(shù)的工作機(jī)制對(duì)測(cè)試主控系統(tǒng)的功能需求,提出了一種基于微機(jī)的符合IEEE1149.4標(biāo)準(zhǔn)的混合信號(hào)邊界掃描測(cè)試主控系統(tǒng)。所采用的廣義特征

2010-11-19 15:04:56 21

21 摘 要: 本文論述了邊界掃描技術(shù)的基本原理和邊界掃描在電路板測(cè)試及在FPGA、DSP器件中的應(yīng)用。介紹了為提高電路板的可測(cè)試性而采用邊界掃描技術(shù)進(jìn)行設(shè)計(jì)時(shí)應(yīng)注意的一些基本

2006-03-11 13:45:44 1602

1602

摘要: 結(jié)合自適應(yīng)算法、CX-TB導(dǎo)通測(cè)試算法以及二進(jìn)制計(jì)數(shù)測(cè)試序列,給出了用軟件控制EPM9320LC84邊界掃描鏈路,以輸出圖形并采集引腳對(duì)圖形的響應(yīng),然后通過(guò)比

2009-06-20 10:50:13 985

985

基于JTAG邊界掃描方式的重構(gòu)控制器的設(shè)計(jì)

引言

JTAG(聯(lián)合測(cè)試行動(dòng)小組)是一種國(guó)際標(biāo)準(zhǔn)測(cè)試協(xié)議(IEEE 1149.1兼容),目前主要用于芯片內(nèi)部測(cè)試。現(xiàn)在多數(shù)的

2010-02-06 10:48:07 1164

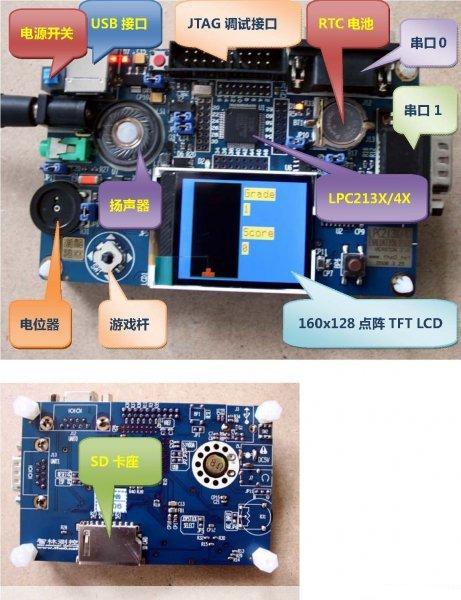

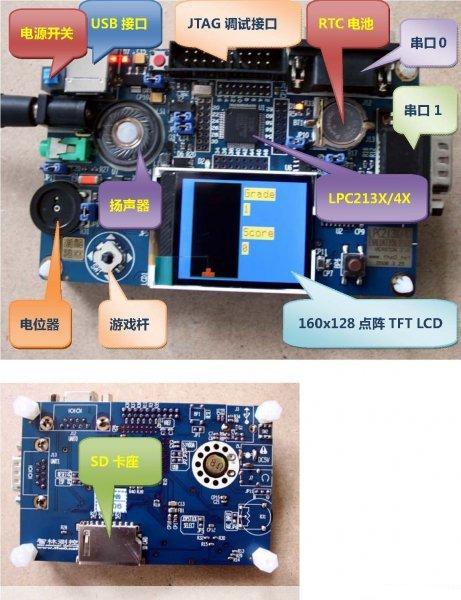

1164 基于JTAG仿真器的調(diào)試是目前ARM開發(fā)中采用最多的一種方式。大多數(shù)ARM設(shè)計(jì)采用了片上JTAG接口,并將其作為測(cè)試、調(diào)試方法的重要組成。

JTAG仿真器通過(guò)ARM芯片的JTAG邊界掃描

2010-06-30 15:20:03 3001

3001

本文針對(duì)當(dāng)前復(fù)雜數(shù)字電路板 快速測(cè)試難的現(xiàn)狀,設(shè)計(jì)了一套基于邊界掃描的電路板測(cè)試系統(tǒng),利用該系統(tǒng)可以對(duì)含有邊 界掃描接口的復(fù)雜數(shù)字電路板進(jìn)行快速診斷,幫助維修人員進(jìn)行

2011-05-18 10:04:58 1654

1654

介紹了支持JTAG 標(biāo)準(zhǔn)的IC 芯片結(jié)構(gòu)和故障測(cè)試的4-wire 串行總線,以及運(yùn)用 邊界掃描 故障診斷的原理。實(shí)驗(yàn)中分析了IC 故障類型、一般故障診斷流程和進(jìn)行掃描鏈本身完整性測(cè)試的方案

2011-07-04 15:08:47 30

30 分析了 邊界掃描 測(cè)試技術(shù)的工作機(jī)制對(duì)測(cè)試主控系統(tǒng)的功能需求, 提出了一種基于 USB總線 的低成本邊界掃描測(cè)試主控系統(tǒng)的硬件設(shè)計(jì)方案; 該系統(tǒng)以便攜式計(jì)算機(jī)為平臺(tái), 用FPGA 實(shí)現(xiàn)

2011-07-04 15:18:15 25

25 隨著支持IEEE1149.1標(biāo)準(zhǔn)的邊界掃描芯片的廣泛應(yīng)用,傳統(tǒng)的電路板測(cè)試方法如使用萬(wàn)用表、示波器探針,已不能滿足板級(jí)測(cè)試的需求,相反一種基于板級(jí)測(cè)試的邊界掃描技術(shù)得到了迅速發(fā)

2012-05-30 15:06:42 45

45 安捷倫科技公司(NYSE:A)日前宣布推出 Agilent x1149 邊界掃描分析儀。x1149 邊界掃描分析儀是一款功能廣泛、使用方便的電路板測(cè)試工具,能夠幫助用戶進(jìn)行電路板設(shè)計(jì)和驗(yàn)證

2013-02-20 11:06:20 4124

4124 邊界掃描測(cè)試的原理及應(yīng)用設(shè)計(jì),有需要的下來(lái)看看。

2016-02-16 18:25:44 24

24 電子專業(yè)單片機(jī)相關(guān)知識(shí)學(xué)習(xí)教材資料之Cyclone_IV器件的JTAG邊界掃描測(cè)試

2016-09-02 16:54:40 0

0 BSDL邊界掃描語(yǔ)言的邊界掃描是一個(gè)完善的測(cè)試技術(shù)。 邊界掃描在自當(dāng)聯(lián)合測(cè)試行動(dòng)組(JTAG)90年代初發(fā)明了一種解決方案來(lái)測(cè)試使用了許多新的印刷電路,正在開發(fā)和制造的地方幾乎沒有或根本沒有測(cè)試探針板的物理訪問(wèn)。

2017-04-19 14:49:48 7918

7918

0 引言 在現(xiàn)代雷達(dá)系統(tǒng)中,帶有DSP(數(shù)字信號(hào)處理器)芯片的數(shù)字電路板應(yīng)用很廣。DSP芯片基本支持IEEE 1149.1標(biāo)準(zhǔn),并且在電路板中形成了邊界掃描鏈,支持邊界掃描測(cè)試。 在DSP電路板中有

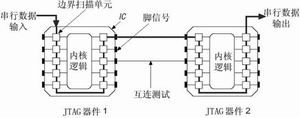

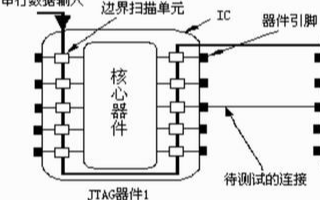

2017-11-03 15:11:40 3

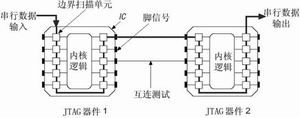

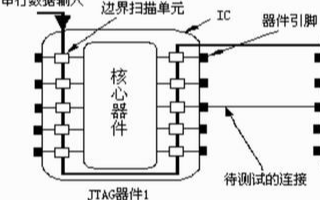

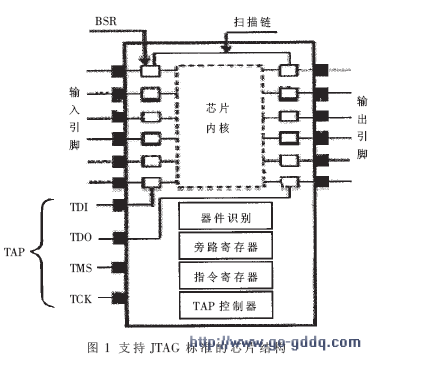

3 的測(cè)試系統(tǒng)方案及其實(shí)現(xiàn),并著重介紹了JTAG總線控制器的設(shè)計(jì)。 邊界掃描測(cè)試的基本原理 邊界掃描測(cè)試的物理基礎(chǔ)是IEEEll49.1測(cè)試總線和設(shè)計(jì)在集成電路內(nèi)的邊界掃描結(jié)構(gòu)。集成電路邊界結(jié)構(gòu)示意圖如圖1所示。

2017-12-01 10:50:16 19

19 的測(cè)試方法如ICT(In-Circuit Test)測(cè)試、功能測(cè)試等已無(wú)法滿足新型雷達(dá)數(shù)字電路測(cè)試及故障診斷的要求,邊界掃描[1]測(cè)試將成為今后雷達(dá)裝備數(shù)字電路故障診斷發(fā)展的主流技術(shù)。

2017-12-11 10:29:01 1560

1560

介紹了支持JTAG標(biāo)準(zhǔn)的IC芯片結(jié)構(gòu)、邊界掃描測(cè)試原理以及利用邊界掃描技術(shù)控制IC芯片處于特定功能模式的方法。針對(duì)IC芯片某種特定的功能模式給出了設(shè)計(jì)思路和方法,并用兩塊xc9572 pc84芯片

2018-05-10 16:52:00 5113

5113

邊界掃描測(cè)試有兩大優(yōu)點(diǎn) :一個(gè)是方便芯片的故障定位,迅速準(zhǔn)確地測(cè)試兩個(gè)芯片管腳的連接是否可靠,提高測(cè)試檢驗(yàn)效率;另一個(gè)是,具有 JTAG接口的芯片,內(nèi)置一些預(yù)先定義好的功能模式,通過(guò)邊界掃描通道來(lái)使芯片處于某個(gè)特定的功能模式,以提高系統(tǒng)控制的靈活性和方便系統(tǒng)設(shè)計(jì)。

2018-03-03 14:15:15 23574

23574

對(duì)于需要進(jìn)行IC元件測(cè)試的設(shè)計(jì)人員來(lái)說(shuō),只要根據(jù)TA P控制器的狀態(tài)機(jī),設(shè)計(jì)特定的控制邏輯,就可以進(jìn)行IC元件的邊界掃描測(cè)試或利用JTA G接口使IC元件處于某個(gè)特定的功能模式。

2018-03-03 14:26:08 6531

6531

多,元器件體積小,板的密度特別大,根本沒有辦法進(jìn)行下探針測(cè)試。一種新的測(cè)試技術(shù)產(chǎn)生了,聯(lián)合測(cè)試行為組織(Joint Test Action Group)簡(jiǎn)稱JTAG 定義這種新的測(cè)試方法即邊界掃描測(cè)試。

2018-05-03 17:48:18 5

5 本文的主要內(nèi)容介紹的是TI的產(chǎn)品C5535 ZHH的邊界掃描模型詳細(xì)資料概述

2018-05-04 16:35:05 4

4 本文檔的主要內(nèi)容介紹的是TI的產(chǎn)品TMS320VC5507 GHH BSDL Model DSP的邊界掃描模型的詳細(xì)資料概述

2018-05-04 16:58:31 15

15 本文檔的主要內(nèi)容介紹的是TI的產(chǎn)品TMS320C5515 ZCH BSDL Model DSP的邊界掃描模型的詳細(xì)資料概述

2018-05-04 17:05:02 12

12 本文檔的主要內(nèi)容介紹的是TI的產(chǎn)品VC5504 ZCH 的邊界掃描模型的詳細(xì)資料概述

2018-05-04 17:10:23 11

11 本文檔的主要內(nèi)容介紹是TI的產(chǎn)品TMS320VC5505 ZCH的邊界掃描模型的詳細(xì)資料概述

2018-05-04 17:14:48 5

5 安捷倫邊界掃描軟件包支持符合IEEE標(biāo)準(zhǔn)1149.1的數(shù)字設(shè)備的測(cè)試。測(cè)試開發(fā)人員可以有效和高效地測(cè)試數(shù)字設(shè)備,同時(shí)顯著減少測(cè)試開發(fā)時(shí)間。當(dāng)邊界掃描被實(shí)現(xiàn)時(shí),故障覆蓋和診斷可以增加。本章提供了關(guān)于邊界掃描和IEEE標(biāo)準(zhǔn)1149.1的概述和背景信息。

2018-12-04 08:00:00 0

0 邊界掃描技術(shù)的基本思想是在芯片管腳和內(nèi)部邏輯之間增加了串聯(lián)在一起的移位寄存器組,在邊界掃描測(cè)試模式下,寄存器單元在相應(yīng)的指令下控制引腳狀態(tài),從而對(duì)外部互連及內(nèi)部邏輯進(jìn)行測(cè)試。邊界掃描結(jié)構(gòu)定義了4個(gè)基本硬件單元:測(cè)試存取口(TAP)、TAP控制器、指令寄存器和測(cè)試數(shù)據(jù)寄存器組。

2019-04-25 15:09:57 1202

1202

會(huì)進(jìn)行邊界掃描測(cè)試,然后進(jìn)行全面的功能測(cè)試,以確保正確的實(shí)時(shí)數(shù)字和模擬性能。

2019-08-14 23:00:00 5123

5123 邊界掃描測(cè)試(Boundary scan)是為了解決印制電路板(PCB)上芯片與芯片之間的互連測(cè)試而提出的一種解決方案。它與內(nèi)部掃描有明顯的區(qū)別,前者是在電路的輸入/輸出端口增加掃描單元,并將這些

2020-04-13 17:31:16 10213

10213

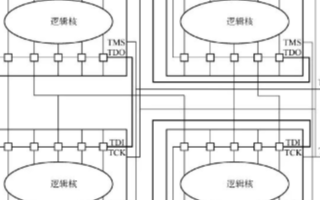

邊界掃描技術(shù)的核心思想是在器件內(nèi)部的核心邏輯與I/O引腳之間插入的邊界掃描單元,它在芯片正常工作時(shí)是“透明”的,不影響電路板的正常工作。各邊界掃描單元以串行方式連接成掃描鏈,通過(guò)掃描輸入端將測(cè)試矢量

2020-08-23 10:56:42 703

703

JTAG是Joint Test Action Group的縮寫,是IEEE 1149.1標(biāo)準(zhǔn)。使用JTAG的優(yōu)點(diǎn):JTAG的建立使得集成電路固定在PCB上,只通過(guò)邊界掃描便可以被測(cè)試。

2020-08-27 14:18:48 2860

2860 在進(jìn)行 PCB 組裝測(cè)試時(shí),通常將其視為增加的支出,而不是將其視為必不可少的質(zhì)量控制措施,從而為最終產(chǎn)品帶來(lái)巨大的價(jià)值。甚至在研究邊界掃描對(duì) PCB 組裝測(cè)試的好處之前,重要的是要回答為什么人們首先

2020-10-13 20:23:04 1256

1256 以新型雷達(dá)裝備數(shù)字電路維修保障為背景,提出了“MERGE(組合)”邊界掃描測(cè)試模型的建立方法,基于此方法,設(shè)計(jì)了完善的便攜式數(shù)字電路自動(dòng)測(cè)試系統(tǒng),解決了ICT 測(cè)試、功能測(cè)試及傳統(tǒng)邊界掃描測(cè)試TPS

2021-03-29 11:31:12 2110

2110

針對(duì)含DSP電路板的測(cè)試與診斷問(wèn)題,本文提出一種利用邊界掃描技術(shù)和傳統(tǒng)的外部輸入矢量測(cè)試相結(jié)合的方法,對(duì)含DSP電路板中的邊界掃描器件的器件及非邊界掃描器件進(jìn)行了測(cè)試。較大的改善了含DSP電路板的測(cè)試覆蓋率和定位精度,具有非常重要的實(shí)用價(jià)值。

2021-04-13 16:35:03 9

9 邊界掃描測(cè)試技術(shù) 不屬于 coresight架構(gòu),邊界掃描測(cè)試技術(shù) 被 coresight 架構(gòu) 使用.綜述 聯(lián)合測(cè)試行動(dòng)組(Joint Test Action Group,簡(jiǎn)稱 JTAG)提出

2021-12-20 19:47:33 20

20 邊界掃描,一種系統(tǒng)級(jí)嵌入式測(cè)試的使能技術(shù)

2022-11-15 19:33:58 0

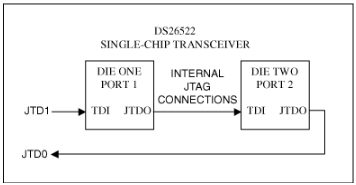

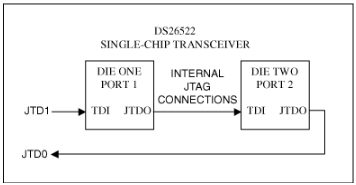

0 本應(yīng)用筆記描述了DS26522雙端口、單芯片收發(fā)器的JTAG硬件邊界掃描鏈。DS26522由兩個(gè)骰子組成,JTAG功能與兩個(gè)以菊花鏈方式連接在一起的獨(dú)立器件相同。本應(yīng)用筆記包含JTAG掃描鏈的完整細(xì)分,并解釋了如何訪問(wèn)邊界中的所有掃描單元。

2023-01-11 15:53:32 913

913

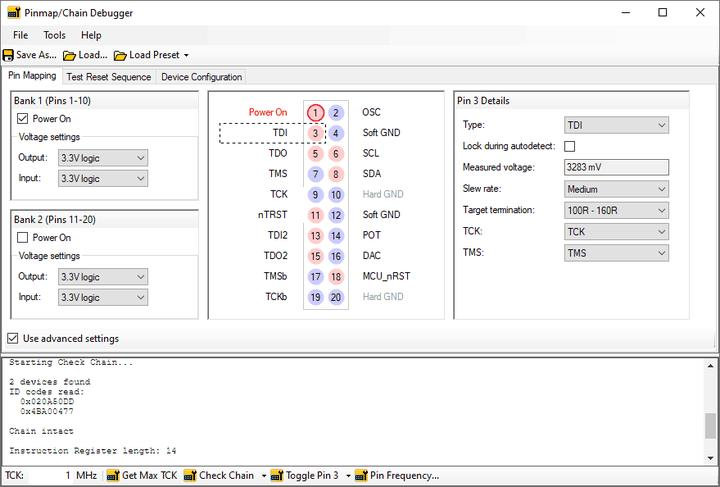

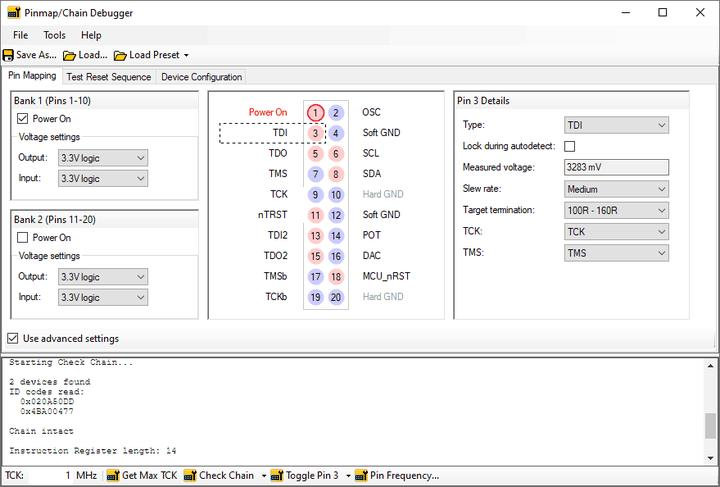

JTAG鏈調(diào)試器(JTAG Chain Debugger),隨XJTAG的安裝包一起安裝,是一個(gè)功能強(qiáng)大的工具,旨在幫助您解決JTAG鏈的問(wèn)題。

2023-07-19 14:41:07 318

318

電子發(fā)燒友網(wǎng)站提供《如何對(duì)基于μTrace和Trace32的LPC86x進(jìn)行邊界掃描.pdf》資料免費(fèi)下載

2023-08-17 10:22:25 1

1 BSDL文件可以在一些邊界掃描的軟件中被使用,如XJTAG,TopJTAG等等,通過(guò)加載對(duì)應(yīng)的BSDL文件可以實(shí)現(xiàn)對(duì)芯片外部所有管腳的讀取和控制。具體使用方法,我會(huì)在后面的文章介紹。

2023-09-10 10:15:09 446

446

前面兩篇文章介紹了邊界掃描的基本原理和BSDL文件,本文文章介紹邊界掃描測(cè)試實(shí)際使用的兩款軟件工具,在后面的實(shí)戰(zhàn)應(yīng)用部分,會(huì)演示基于STM32和FPGA的邊界掃描測(cè)試應(yīng)用。

2023-09-11 14:34:56 1278

1278

前面幾篇文章,介紹了關(guān)于JTAG邊界掃描的一些基礎(chǔ)知識(shí)和常用的調(diào)試軟件。

2023-09-12 12:27:33 585

585

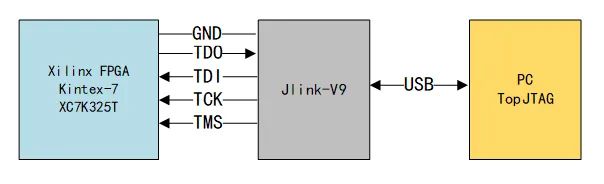

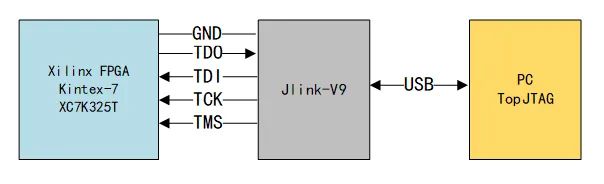

上一篇文章,介紹了基于STM32F103的JTAG邊界掃描應(yīng)用,演示了TopJTAG Probe軟件的應(yīng)用,以及邊界掃描的基本功能。本文介紹基于Xilinx FPGA的邊界掃描應(yīng)用,兩者幾乎是一樣。

2023-09-13 12:29:37 655

655

電子發(fā)燒友App

電子發(fā)燒友App

評(píng)論