PCIe總線作為處理器系統(tǒng)的局部總線,其作用與PCI總線類似,主要目的是為了連接處理器系統(tǒng)中的外部設(shè)備,當(dāng)然PCIe總線也可以連接其他處理器系統(tǒng)。

2023-02-23 09:39:22 1579

1579 本帖最后由 一只耳朵怪 于 2018-6-13 11:10 編輯

[tr=transparent]雙路千兆網(wǎng)絡(luò)PCIe收發(fā)卡[/tr][tr=transparent] 一、產(chǎn)品概述PCIe網(wǎng)絡(luò)

2018-06-12 16:33:28

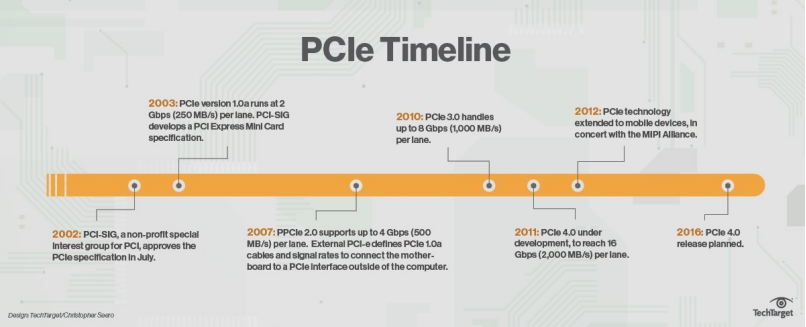

1.PCIE的發(fā)送和接收數(shù)據(jù)本工程的目的是在XC7K325tffg的平臺(tái)上實(shí)現(xiàn)pcie的數(shù)據(jù)發(fā)送和接收,速率8通道2.5GB/s,首先看下本工程的PCIE部分的結(jié)構(gòu):架構(gòu)各個(gè)模塊的作用PCIE部分

2019-12-26 10:46:09

1

PCIE基本概念1.1

PCIE拓?fù)?b class="flag-6" style="color: red">架構(gòu)圖1.2

PCIE Switch內(nèi)部結(jié)構(gòu)圖1.3

PCIE協(xié)議結(jié)構(gòu)圖2

PCIE枚舉原理2.1 Type0&Type1配置頭空間2.2 拓?fù)涫纠?/div>

2022-02-16 06:08:26

和AMBA ACE協(xié)議和ARM架構(gòu)。

該文檔涵蓋以下主題:

·本文檔中使用的術(shù)語說明。

·針對(duì)PCIe事務(wù)的ARM內(nèi)存類型使用指南。

·如何遵守ARM處理元件(PE)的PCIe事務(wù)的ARM內(nèi)存模型要求

2023-08-17 07:25:03

PCIe是什么?PCIe的架構(gòu)是由哪些部分組成的?PCIe總線和PCI總線有哪些不同之處呢?

2021-10-26 08:10:07

只提供一些 x8 插槽和幾個(gè) x4 插槽。為了節(jié)省成本,部分服務(wù)器廠商甚至使用了 x8 連接器,但卻僅將它們連接成 x4,這確實(shí)十分有趣。 大部分人(像我一樣的架構(gòu)師)都知道,PCIe 每發(fā)展一代

2021-01-07 17:31:57

和PCIe,走過近30年時(shí)光。其中Host發(fā)現(xiàn)與查找設(shè)備的方式卻一脈沿襲,今天我們先來聊一聊PCIe設(shè)備在一個(gè)系統(tǒng)中是如何發(fā)現(xiàn)與訪問的。首先我們來看一下在x86系統(tǒng)中,PCIe是什么樣的一個(gè)體系架構(gòu)。下圖

2021-05-25 09:22:48

一、概述常用單片機(jī)軟件架構(gòu)大體分三種:1. 前后臺(tái)順序執(zhí)行程序2. 時(shí)間片輪詢法3. 操作系統(tǒng)二、前后臺(tái)順序執(zhí)行程序所謂的前臺(tái),就是主動(dòng)去判斷處理某個(gè)事務(wù),這個(gè)是主循環(huán)里要做的事,也就是你代碼主要

2021-11-22 06:57:12

這里寫目錄標(biāo)題概述隔離式電源集中式電源架構(gòu)分布式電源架構(gòu):個(gè)人理解概述· 集中式電源架構(gòu)(CPA):效率高,但成本高,PCB占用面積大。· 分布式電源架構(gòu)(DPA):節(jié)省成本和PCB占用面積,需要

2021-11-11 07:07:46

CANOpen系列教程07_CANOpen協(xié)議概述

2020-12-31 06:10:32

目錄CMSIS軟件架構(gòu)庫文件說明CMSIS軟件架構(gòu)CMSIS概述? ? ?CMSIS軟件架構(gòu)由四層:用戶應(yīng)用層、操作系統(tǒng)及中間件接口層、CMSIS層和硬件層? ? ?由三部分構(gòu)成核內(nèi)外設(shè)訪問層

2021-12-22 07:34:50

協(xié)議及FPGA實(shí)現(xiàn)接下來就是高速接口高速接口FPGA中通過Serdes可以實(shí)現(xiàn)大部分高速接口。常見的就是PCIe和SRIO,在ZYNQ中還有AXI非常常用。對(duì)于PowerPC則可以使用PLB

2022-08-19 16:32:22

**一、IIC通信協(xié)議**(1)概述I2C(Inter-Integrated Circuit BUS) 集成電路總線,該總線由 NXP(原 PHILIPS)公司設(shè)計(jì),多用于主控制器和從器件間的主從

2021-11-22 07:51:52

多數(shù)分布式MAC協(xié)議采用載波偵聽或沖突避免機(jī)制并采用附加的信令控制消息來處理隱藏和暴露節(jié)點(diǎn)問題。基于競爭隨機(jī)訪問的MAC協(xié)議是節(jié)點(diǎn)需要發(fā)送數(shù)據(jù)時(shí),通過競爭方式使用無線信道。

2019-09-23 09:12:01

的PRST、 WAKE 、CLKREQ信號(hào)定義。這幾個(gè)信號(hào)(PRST、 WAKE 、CLKREQ信號(hào))是必需的嗎注意 我說的是mini pcie, 單說pcie 是需要的。目前該接口的軟件協(xié)議部分還不清楚,所以對(duì)這幾個(gè)信號(hào)定義和作用不明白。請(qǐng)知道的大俠指點(diǎn),多謝

2017-11-29 11:50:51

FPGA(資源夠用)都可以以soft IP形式實(shí)現(xiàn)FPGA嗎?4.個(gè)人覺得使用Megwizard和Qsys中的IP就可以實(shí)現(xiàn)PCIE功能了,那么什么樣的設(shè)計(jì)還需要加專用的協(xié)議芯片呢?謝謝!

2015-07-27 11:05:46

RT-Thread概述RT-Thread的架構(gòu)

2021-03-29 06:29:54

STM32是什么?有哪幾種分類?STM32芯片的架構(gòu)是如何構(gòu)成的?

2021-10-29 07:53:20

目前我們已經(jīng)發(fā)布了NXP的QorIQLS架構(gòu)系列的幾款平臺(tái),包含LS1046A、LS1043A、LS1028A、LS1012A。這幾款平臺(tái)都原生支持網(wǎng)口、PCIE、SATA等高速接口協(xié)議,很多

2021-12-20 06:01:37

一、TCP/IP協(xié)議1、TCP/IP通信協(xié)議是目前最完整、最被廣泛支持的通信協(xié)議,它可以讓不同網(wǎng)絡(luò)架構(gòu)、不同操作系統(tǒng)的計(jì)算機(jī)之間通信,是Internet的標(biāo)準(zhǔn)通信協(xié)議TCP/IP 協(xié)議是 計(jì)算機(jī)

2021-08-05 07:51:57

USB協(xié)議起因簡介標(biāo)準(zhǔn)歷史USBUSB On-The-Go Supplement技術(shù)細(xì)節(jié)概述技術(shù)指標(biāo)機(jī)械和電氣標(biāo)準(zhǔn)編碼方式軟件架構(gòu)端點(diǎn)HCDUSB 封包格式設(shè)備分類USB接頭電源同類標(biāo)準(zhǔn)比較

2021-07-28 08:32:46

一、概述XSP06是一款符合USB Power Delivery標(biāo)準(zhǔn)的PD、QC、AFC協(xié)議的受電端(誘騙)協(xié)議芯片,支持從手機(jī)充電器/車充等電源上誘騙出需要的電壓給產(chǎn)品供電。支持固定電壓模式

2021-12-02 06:23:24

12.1概述_,12.1.1無線傳感器網(wǎng)絡(luò)中分簇設(shè)計(jì)的主要目的和挑戰(zhàn)12.2分簇算法分類12.2.1分簇參數(shù)12.2.2分類簇集協(xié)議12.3概率分簇方法12.3.1廣泛的概率分簇協(xié)議12.3.1.1低能

2012-08-17 09:52:38

、Artix-7 CPU,1.8GHz主頻。MYC-JX8MMA7核心板及開發(fā)板是基于ARM+FPGA處理架構(gòu),以ARM處理性能為主,F(xiàn)PGA作為輔助的系統(tǒng)。一、概述MYD-JX8MMA7 硬件平臺(tái)采用

2023-01-30 14:14:25

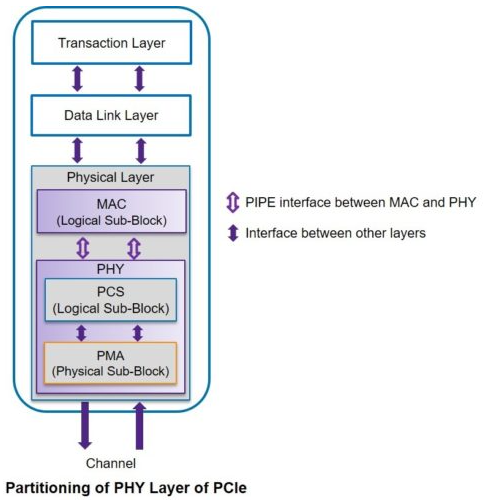

出TLP發(fā)給事務(wù)層;事務(wù)層解析TLP,取出有效負(fù)載數(shù)據(jù)。1.4 概述1.4.1 CXLCXL在PCIe 5.0的基礎(chǔ)上復(fù)用三種類型的協(xié)議,分別 CXL.io,CXL.cache,CXL.memory

2022-09-09 15:03:06

串行總線協(xié)議PCIe、ASI和sRIO之間有什么不同?

2021-05-25 07:05:09

SPI協(xié)議概述SPI協(xié)議舉例SPI協(xié)議心得

2021-03-04 06:24:57

和主機(jī)怎么交互起來都是一個(gè)問題。入門一看PCIE協(xié)議,會(huì)發(fā)現(xiàn)繁多也難懂——PCIE體系龐大足以讓天下無書,這夸張我已經(jīng)不知道從哪里聽來了。如果能夠一邊把PCIE通信交互轉(zhuǎn)起來,一邊理解去PCIE協(xié)議

2023-11-17 14:35:30

介紹參考時(shí)鐘需求。PCIe 參考時(shí)鐘 (RefClk) 規(guī)范可針對(duì) 3 種不同架構(gòu)定義,分別是:數(shù)據(jù)時(shí)鐘、獨(dú)立 RefClk 以及通用 RefClk。每個(gè)架構(gòu)都具有特定的濾波器函數(shù)。在接收器時(shí)鐘數(shù)據(jù)恢復(fù)

2018-09-17 16:12:25

第一章 單片機(jī)概述1.1 單片機(jī)概念1.2 單片機(jī)的特點(diǎn)1.3 單片機(jī)的發(fā)展1.4 單片機(jī)的分類1.5 單片機(jī)的應(yīng)用1.6 微機(jī)的基本結(jié)構(gòu)1.7 碼制與數(shù)制1.1 單片機(jī)概念1.2 單片機(jī)的特點(diǎn)

2022-01-19 06:41:49

; 通道數(shù):2基于pcie的串行協(xié)議交換

2010-11-08 23:25:23

基于kintex UltraScale XCKU060的雙路QSFP+光纖PCIe 卡一、板卡概述 本板卡系北京太速科技自主研發(fā),基于Xilinx UltraScale Kintex系列

2022-07-11 11:35:54

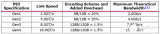

PCI Express? (PCIe?) 是一項(xiàng)業(yè)界領(lǐng)先的標(biāo)準(zhǔn)輸入/輸出 (I/O) 技術(shù),是服務(wù)器、個(gè)人電腦以及其它應(yīng)用中最常用的 I/O 接口之一。該標(biāo)準(zhǔn)多年來不斷發(fā)展,以適應(yīng)更高的數(shù)據(jù)速率

2022-11-22 08:04:25

PCI Express (PCIe)是嵌入式和其它系統(tǒng)類型的背板間通信的一個(gè)非常理想的協(xié)議。然而,在嵌入式環(huán)境中,背板連接器引腳通常很昂貴。因此,采用點(diǎn)對(duì)點(diǎn)連接的星型結(jié)構(gòu)的PCIe時(shí)鐘分配方案就變得

2019-09-26 07:56:41

PCI Express (PCIe)是嵌入式和其它系統(tǒng)類型的背板間通信的一個(gè)非常理想的協(xié)議。然而,在嵌入式環(huán)境中,背板連接器引腳通常很昂貴。因此,采用點(diǎn)對(duì)點(diǎn)連接的星型結(jié)構(gòu)的PCIe時(shí)鐘分配方案就變得

2019-08-30 06:54:47

嗨,我有一個(gè)ML605板和一塊使用RapidIO協(xié)議的DSP板。該板有兩個(gè)FMC連接器(HPC和LPC)和一個(gè)PCIe接口,我需要4個(gè)萬兆收發(fā)器(MGT),PCIe和FMC HPC都有8個(gè)(LPC

2019-08-29 10:33:02

域架構(gòu)中,ECU可根據(jù)功能不同分為不同的域。但區(qū)域架構(gòu)是一種按照ECU在汽車內(nèi)的實(shí)際位置分類的新方法,并利用中央網(wǎng)關(guān)來管理通信。這種物理接近性可減少ECU之間的布線,從而節(jié)省空間并降低汽車重量,同時(shí)

2022-11-07 07:38:40

`<h2>電感元件的分類概述</h2><div class="t_msgfont" id

2010-04-22 19:11:43

目錄0x01 藍(lán)牙概述0x02 藍(lán)牙技術(shù)分類Basic Rate(BR)/AMPLow Energy(LE)0x03 藍(lán)牙架構(gòu)0x04 藍(lán)牙協(xié)議應(yīng)用層(App Layer)L2CAP(Logical

2021-07-22 06:47:46

步進(jìn)電機(jī)詳解概述步進(jìn)電機(jī)的分類、結(jié)構(gòu)、原理單相步進(jìn)電機(jī)2相步進(jìn)電機(jī)概述根據(jù)電壓種類分類,可以分為AC和DC。根據(jù)旋轉(zhuǎn)速度以及電源頻錄之間的關(guān)系可以分為同步電機(jī)和異步電機(jī)。小型電機(jī)中步進(jìn)電機(jī)的位置如下

2021-07-08 06:46:29

傳輸速率是根據(jù)PCIE的協(xié)議制定的嗎?2.如果我設(shè)置的速率超過5.0Gbps可以嗎?是否會(huì)出現(xiàn)數(shù)據(jù)的傳輸錯(cuò)誤等現(xiàn)象?3.不太理解PCIE中關(guān)于x1和x2的含義,文檔說PCIE是one single interface link,那么對(duì)于單個(gè)端口而言,x2的含義僅僅是代表速率是x1速率的一倍嗎?

2018-06-19 04:36:26

本篇文章是基于STM32F767的學(xué)習(xí)總結(jié)文章目錄通訊方式分類典型通信方式概述串口通信IICSPI附錄參考鏈接通訊方式分類從物理結(jié)構(gòu)來看:通信方式分為并行通信與串行通信兩種方式,串行只用到一根線即可

2021-12-16 06:51:37

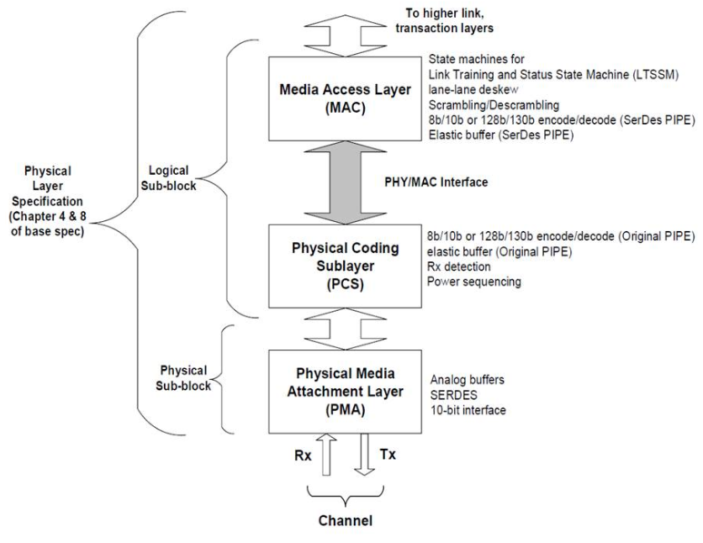

PCI Express是一種高性能互連協(xié)議,被廣泛應(yīng)用于網(wǎng)絡(luò)適配、圖形加速器、網(wǎng)絡(luò)存儲(chǔ)、大數(shù)據(jù)傳輸以及嵌入式系統(tǒng)等領(lǐng)域。文中介紹了PCIe的體系結(jié)構(gòu),以及利用Altera Cyclone IV GX

2019-05-21 09:12:26

在分析原有HMIPv6 網(wǎng)絡(luò)架構(gòu)的基礎(chǔ)上提出一種基于樹狀和分布式架構(gòu)相結(jié)合的網(wǎng)絡(luò)架構(gòu)。該架構(gòu)可解決在HMIPv6 中的MAP發(fā)現(xiàn)協(xié)議的不足,解決較高層次MAP 的瓶頸問題和提高原有網(wǎng)絡(luò)

2009-04-17 09:07:19 9

9 課程說明 . 1課程介紹. 1課程目標(biāo). 1相關(guān)資料. 1第一節(jié) 路由協(xié)議概述 11.1 概述. . 21.2 路由協(xié)議簡介 21.3 靜態(tài)路由 . . . 51.4 靜態(tài)路由的配置. . . . 51.5 利用靜

2009-06-24 17:40:12 10

10 學(xué)習(xí)完本課程,您應(yīng)該能夠了解:SoftX3000接口與協(xié)議的概念SoftX3000協(xié)議的分類SoftX3000各協(xié)議與信令的作用課程內(nèi)容第一節(jié) 接口與協(xié)議第二節(jié) SoftX3000信令

2009-07-31 10:25:43 20

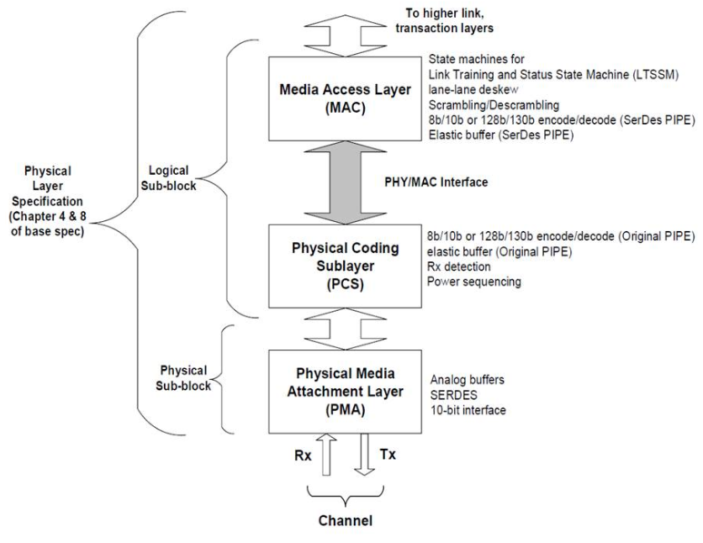

20 M31 PCIe 3.1 PHY IP M31 PCIe 3.1 PHY IP為高帶寬應(yīng)用提供高性能、多通道功能和低功耗架構(gòu)。PCIe 3.1 IP支持一系列完整的PCIe 3.1基本應(yīng)

2023-04-03 19:50:56

功能和低功耗架構(gòu)。PCIe 4.0 IP支持一系列完整的PCIe 4.0基本應(yīng)用程序,并符合PIPE 4.4.1規(guī)范。IP集成了高速混合信號(hào)電路,以支持16Gbp

2023-04-03 19:54:58

M31 PCIe 5.0 PHY IP,用于存儲(chǔ)和高帶寬連接 M31 PCIe 5.0 PHY IP為高帶寬應(yīng)用提供高性能、多通道功能和低功耗架構(gòu)。PCIe 5.0 IP支持一系列PCIe

2023-04-03 19:57:12

WCDMA網(wǎng)絡(luò)架構(gòu)及通訊協(xié)議

在前文中,我們?cè)岬経MTS架構(gòu):為盡量減少網(wǎng)路架構(gòu)變動(dòng),網(wǎng)路端被分為前端存取網(wǎng)路(Access Network)和后端核

2009-06-01 19:28:34 3153

3153 UMTS協(xié)議架構(gòu)

2009-09-18 15:14:08 929

929 UE側(cè)協(xié)議棧架構(gòu)

2009-09-18 15:25:10 1245

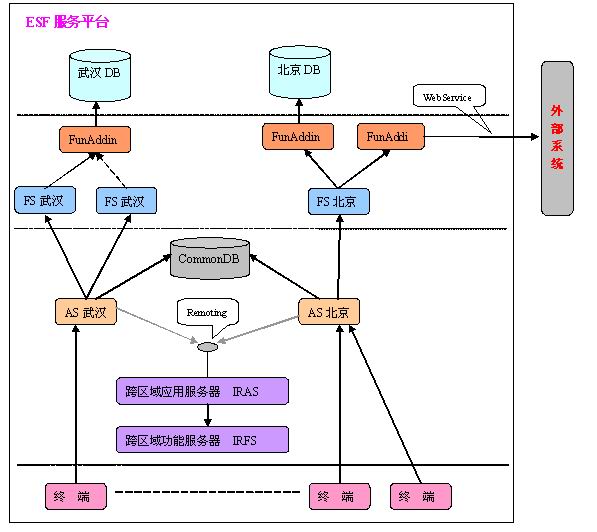

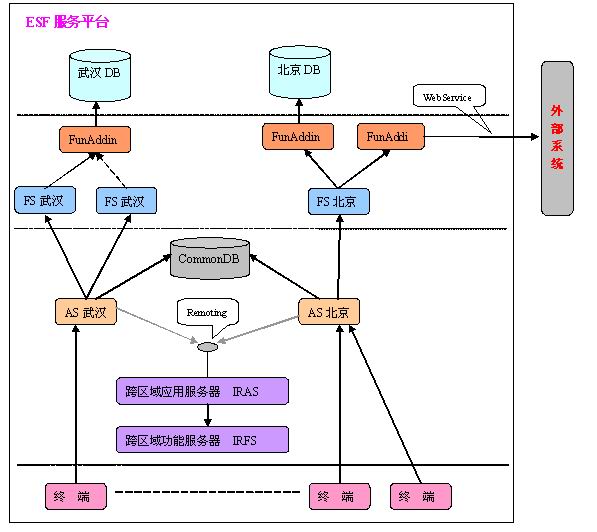

1245 基于C/S的4層架構(gòu)概述

ESFramework的4層結(jié)構(gòu)的4層分別是:客戶端(Client)、應(yīng)用服務(wù)器(AS)、功能服務(wù)器(FS)、數(shù)據(jù)庫服務(wù)器。它們之間的聯(lián)

2010-03-29 15:21:49 3676

3676

PericomSemiconductor推出五款PCIe與USB串行連接

新聞事件:

PericomSemiconductor推出五款據(jù)PCIe和USB通訊協(xié)議設(shè)計(jì)的新產(chǎn)品

&nb

2010-04-20 09:02:00 963

963 介紹關(guān)于路由協(xié)議的概念、原理,路由協(xié)議的分類和作用詳解。

2011-11-03 15:08:50 9473

9473 基于PCIe2_0協(xié)議的PCS層彈性緩沖器設(shè)計(jì)_武桂林

2017-01-07 20:49:27 5

5 PCI Express(PCIe)是一種高性能互連協(xié)議,可應(yīng)用于網(wǎng)絡(luò)適配、圖形加速、服務(wù)器、大數(shù)據(jù)傳輸、嵌入式系統(tǒng)等領(lǐng)域。PCIe協(xié)議在軟件層上可兼容于PCI和PCIX,但同時(shí)也有明顯的不同。在兩個(gè)

2017-10-13 10:41:03 24

24 流量分類是優(yōu)化網(wǎng)絡(luò)服務(wù)質(zhì)量的基礎(chǔ)與關(guān)鍵,機(jī)器學(xué)習(xí)算法利用數(shù)據(jù)流統(tǒng)計(jì)特征分類流量,對(duì)于識(shí)別加密私有協(xié)議流量具有重要意義.然而,特征偏置和類別不平衡是基于機(jī)器學(xué)習(xí)的流量分類研究所面臨的兩大挑戰(zhàn).特征偏置

2018-01-08 10:28:37 0

0 本文檔的主要內(nèi)容詳細(xì)介紹的是MCS-51指令系統(tǒng)的分類、格式及一般說明和尋址方式,分類指令資料概述。

2018-09-29 16:18:34 6

6 本文檔的主要內(nèi)容詳細(xì)介紹的是MODBUS協(xié)議的概述和使用指南資料免費(fèi)下載包括了:第一部分:Modbus 協(xié)議資料概述,第二部分:Modbus 協(xié)議在串行鏈路上的實(shí)現(xiàn)指南,第二部分:Modbus 協(xié)議在串行鏈路上的實(shí)現(xiàn)指南,第三部分:Modbus 協(xié)議在 TCP/IP 上 的實(shí)現(xiàn)指南。

2019-09-19 08:00:00 5

5 CANOpen系列教程07_CANOpen協(xié)議概述

2020-03-06 16:33:50 4769

4769 路由協(xié)議有自己的路由算法,能夠自動(dòng)適應(yīng)網(wǎng)絡(luò)拓?fù)涞淖兓m用于具有一定規(guī)模的網(wǎng)絡(luò)拓?fù)洹F?缺點(diǎn)是配置比較復(fù)雜,對(duì)系統(tǒng)的要求高于靜態(tài)路由,并占用一定的網(wǎng)絡(luò)資源。 對(duì)路由協(xié)議的分類可采用以下不同標(biāo)準(zhǔn)。

2020-03-04 16:30:46 13059

13059 在linux運(yùn)維(網(wǎng)絡(luò)安全運(yùn)維基礎(chǔ)入門)中,存儲(chǔ)提供了數(shù)據(jù)的基本保障,在整個(gè)架構(gòu)中是非常重要的環(huán)節(jié)。 學(xué)好存儲(chǔ)的前提是先認(rèn)識(shí)存儲(chǔ)和存儲(chǔ)架構(gòu)的分類。

2020-05-05 22:28:00 2075

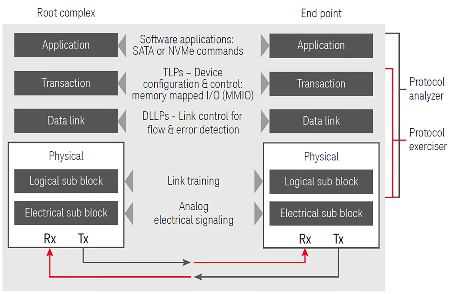

2075 分析革命性創(chuàng)新的領(lǐng)導(dǎo)者,SerialTek公司的PCIe Gen 4和Gen 5協(xié)議分析儀不僅顛覆了傳統(tǒng)的PCIe協(xié)議分析儀架構(gòu)設(shè)計(jì),大大提高了協(xié)議分析儀的性能以及用戶的測(cè)試效率,改變了用戶使用PCIe協(xié)議分析儀的習(xí)慣,同時(shí),它也提供了超高的靈活性和業(yè)內(nèi)最高的性價(jià)比,讓更多的公司買得起PCIe

2020-09-21 14:26:48 9855

9855 隨著PCIe Gen 4和Gen 5的項(xiàng)目開發(fā)越來越多,很多公司希望在PCIe鏈路層注入故障來模擬針對(duì)主板/背板一側(cè),或者外設(shè)一側(cè)(如插卡,NVMe SSD等)的各種異常,業(yè)內(nèi)主流的CPU廠商例如

2020-10-16 11:11:38 3938

3938 和PCIe,走過近30年時(shí)光。其中Host發(fā)現(xiàn)與查找設(shè)備的方式卻一脈沿襲,今天我們先來聊一聊PCIe設(shè)備在一個(gè)系統(tǒng)中是如何發(fā)現(xiàn)與訪問的。 首先我們來看一下在x86系統(tǒng)中,PCIe是什么樣的一個(gè)體系架構(gòu)

2021-01-12 16:50:16 4520

4520 導(dǎo)言:這篇為PCIe要提及的時(shí)鐘類型作個(gè)小鋪墊,可以大致作一個(gè)了解,想深入了解可以參考更加細(xì)致的文獻(xiàn)。 三種基本的I/O架構(gòu) 1? 通用時(shí)鐘(Common Clock) 2? 前向時(shí)鐘

2021-04-04 11:53:00 4693

4693

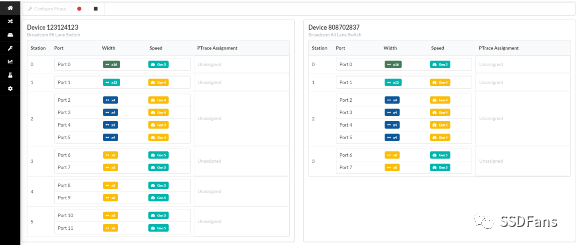

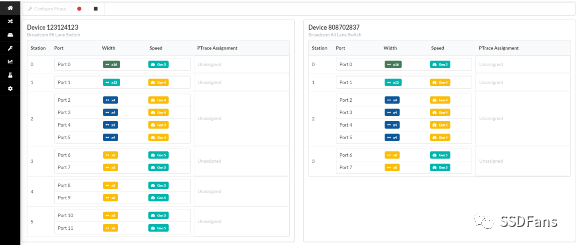

等各環(huán)節(jié)可能遇到的各種疑難問題,工程師只需要免費(fèi)下載SerialTek PCIe協(xié)議分析儀軟件BusXpert即可直接配置PCIe Gen 5 switch進(jìn)行抓包分析,可以分析upstream以及

2021-04-13 15:30:47 4797

4797

SerialTek是PCIe,NVMe和SAS/SATA協(xié)議測(cè)試解決方案的全球領(lǐng)先提供商,今天推出的PCIe測(cè)試和分析市場的最新技術(shù)和產(chǎn)品BusXpertiTAP,支持Broadcom的PCIe嵌入式分析儀技術(shù),這是Broadcom新的PEX89000 Gen5 PCIe交換芯片的一項(xiàng)突破性功能。

2021-04-13 15:34:21 5505

5505

/秒(PCIE5.0 X16),增長了480倍。 PCIe 5.0 第5代PCIe技術(shù) PCIe5.0速度是 PCIe 4.0 的兩倍,并具有向下兼容性。PCIe 5.0 協(xié)議分析儀能夠支持 32GT

2021-06-19 11:04:51 33055

33055 基于VIVADO的PCIE IP的使用 項(xiàng)目簡述 上一篇內(nèi)容我們已經(jīng)對(duì)PCIE協(xié)議進(jìn)行了粗略的講解。那么不明白具體的PCIE協(xié)議,我們就不能在FPGA中使用PCIE來進(jìn)行高速數(shù)據(jù)傳輸了嗎?答案是否

2021-08-09 16:22:10 10198

10198

1

PCIE基本概念1.1

PCIE拓?fù)?b class="flag-6" style="color: red">架構(gòu)圖1.2

PCIE Switch內(nèi)部結(jié)構(gòu)圖1.3

PCIE協(xié)議結(jié)構(gòu)圖2

PCIE枚舉原理2.1 Type0&Type1配置頭空間2.2 拓?fù)涫纠?/div>

2021-12-17 18:29:51 26

26 探究USB協(xié)議架構(gòu)及驅(qū)動(dòng)架構(gòu)

2022-01-25 16:35:27 1

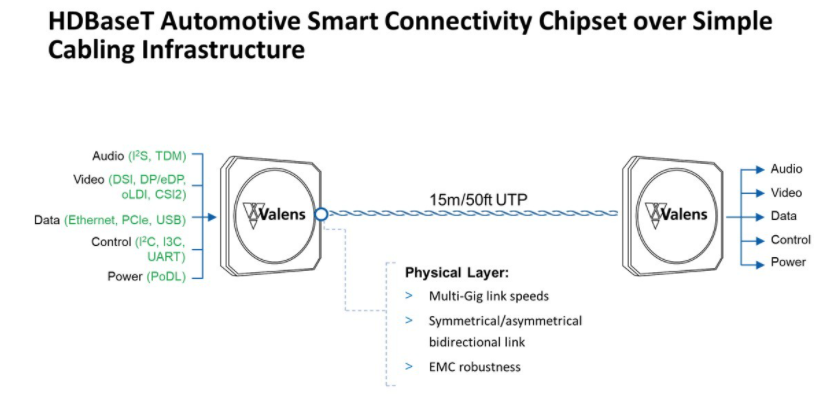

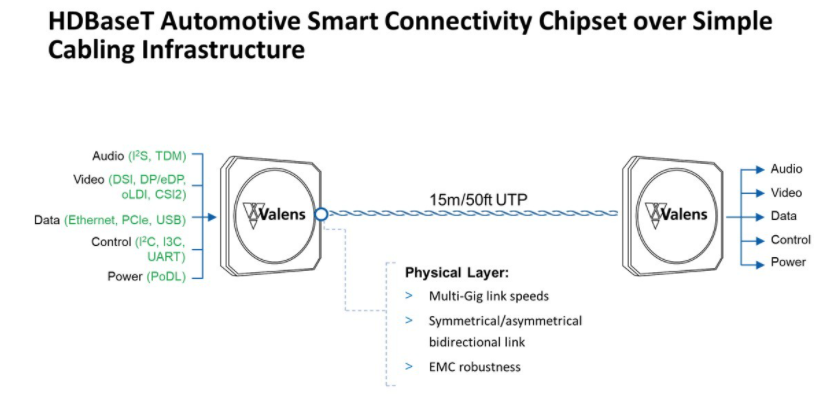

1 PCIe 虛擬化支持在多個(gè)設(shè)備之間共享資源,優(yōu)化汽車的網(wǎng)絡(luò)架構(gòu)并支持其他用例。通過擴(kuò)展 PCIe,HDBaseT Automotive 支持多個(gè)虛擬機(jī)和物理機(jī)之間的設(shè)備共享,同時(shí)提供故障轉(zhuǎn)移機(jī)制以提高可靠性。

2022-06-17 09:19:36 2426

2426

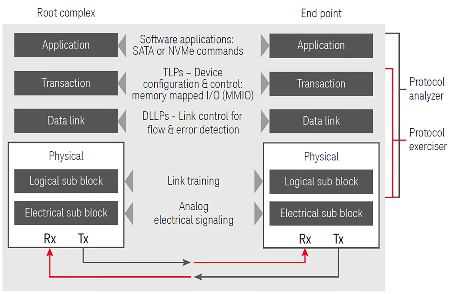

在滿足所有測(cè)試以建立穩(wěn)定的通信通道后,下一步是驗(yàn)證PCIe 總線上的應(yīng)用層(例如 NVMe)。對(duì)于 NVMe 協(xié)議測(cè)試,用戶將需要一個(gè)工具來觀察不同部分的交互方式。數(shù)據(jù)鏈路層、確認(rèn)、流控制、多個(gè)隊(duì)列和多個(gè)命令需要協(xié)調(diào)。在一次 NVMe 讀取中可能需要分析數(shù)千個(gè)數(shù)據(jù)包。一個(gè)好的工具將

2022-06-19 15:44:08 1883

1883

據(jù)悉,芯盛智能PCIe控制器名為“行者”,采用RISC-V六核架構(gòu)體系,前端具備PCIe4.0×4高速接口,后端采用8通道閃存接口,支持NVMe1.4傳輸協(xié)議,順序讀寫速度可達(dá)7000/6000MBps,4K隨機(jī)讀寫可達(dá)1000k/900kIOPS。

2022-08-04 09:21:54 1751

1751 CXL是基于PCIe 5.0實(shí)現(xiàn)的連接技術(shù),復(fù)用了很多PCIe協(xié)議的東西,這一點(diǎn)上與CCIX比較像,但又不完全一樣。說起CCIX和CXL,難免要相互對(duì)比。

2022-09-06 10:05:57 5256

5256 PCIE協(xié)議5.0完整版

2022-09-13 14:32:47 0

0 PCIE3.0協(xié)議分析儀U4301A,它是一塊采用了Agilent AXIe架構(gòu)的插卡,可以插在AXIe的機(jī)箱里,通過探頭來捕獲高速的PCIE 3.0信號(hào),并通過外部PC控制顯示協(xié)議分析的結(jié)果。

2022-10-12 17:33:56 1191

1191 佰維針對(duì)ARM架構(gòu)服務(wù)器的這一痛點(diǎn),提供創(chuàng)新性的PCIe BGA SSD+LPDDR4X存儲(chǔ)搭配方案,一舉解決了SOC平臺(tái)的存儲(chǔ)協(xié)議限制,賦予云手機(jī)更佳的性能體驗(yàn)。

2022-10-24 17:22:21 669

669 高級(jí)微控制器總線架構(gòu)(AMBA)是一種開放標(biāo)準(zhǔn)的片上互連方式。概述了如何連接和管理SoC中的不同組件或塊。它的應(yīng)用逐漸超出了微控制器的范疇,包括創(chuàng)建使用大量外設(shè)和控制器的多處理器設(shè)計(jì)。

2023-04-12 10:29:21 816

816 PCIe接口從2001年發(fā)展至今,在協(xié)議的完整性上已經(jīng)建立足夠高的"護(hù)城河",重新定義一個(gè)接口協(xié)議在性能上超越PCIe,短期內(nèi)一方面沒有企業(yè)會(huì)有這個(gè)動(dòng)力,另一方面技術(shù)的維度,也沒有可預(yù)期的雛形創(chuàng)新。

2023-04-13 11:10:00 2900

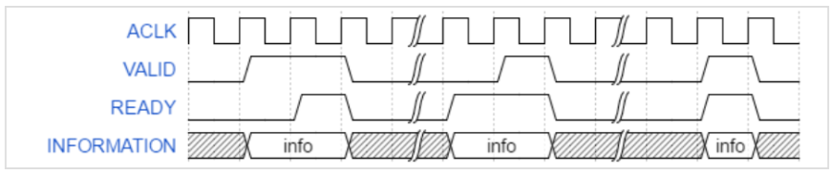

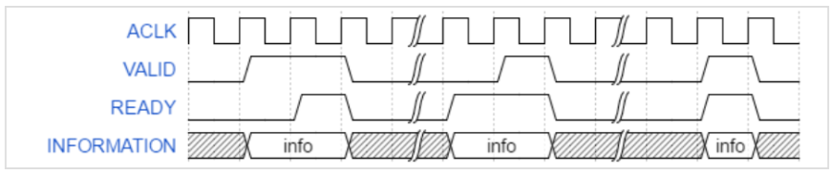

2900 之前文章為大家介紹了AXI的協(xié)議與架構(gòu),本篇我們接著往下講AXI的讀寫傳輸

內(nèi)容概括

2023-05-04 14:41:27 1423

1423

最近某開發(fā)嵌入式平臺(tái)的客戶到我們的協(xié)議測(cè)試Open Lab分析底層PCIe的問題。

2023-05-06 09:25:26 717

717

5月,芯盛智能發(fā)布基于RISC-V開源架構(gòu)主控芯片的高性能PCIe SSD——EP2000Pro、MP2000Pro及EP3000,全面兼容3D TLC和QLC顆粒,并與國內(nèi)主流CPU、OS、整機(jī)廠商適配兼容,以開源架構(gòu)助力自研存儲(chǔ)創(chuàng)新升級(jí),為用戶帶來安全高效的數(shù)據(jù)存儲(chǔ)體驗(yàn)。

2023-05-16 11:54:25 400

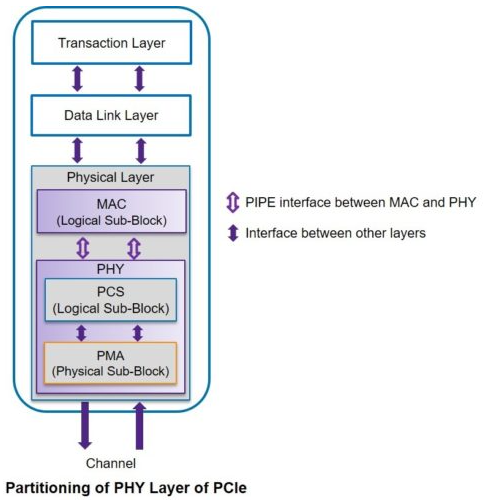

400 人工智能和機(jī)器學(xué)習(xí)正在迅速滲透到廣泛的設(shè)備中,推動(dòng)了SoC設(shè)計(jì)的重新架構(gòu),需要更多的內(nèi)存空間和更高的帶寬來傳輸和處理數(shù)據(jù)。這種變化需要更高速的接口和更寬的總線,為最新 PCIe 協(xié)議規(guī)范的增強(qiáng)以及升級(jí) PIPE(PCI Express 的 PHY 接口)規(guī)范作為首選 PHY 接口鋪平了道路。

2023-05-26 10:20:06 3839

3839

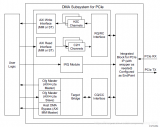

PCIe 是一種多層串行總線協(xié)議,可實(shí)現(xiàn)雙單工鏈路。由于其專用的點(diǎn)對(duì)點(diǎn)拓?fù)洌峁└咚贁?shù)據(jù)傳輸和低延遲。為了加快基于 PCIe 的子系統(tǒng)的驗(yàn)證和設(shè)備開發(fā)時(shí)間,英特爾定義了 PIPE(PCI

2023-05-26 11:43:19 2027

2027

Spec洋洋灑灑數(shù)千頁,也不會(huì)從頭到尾去通讀整個(gè)協(xié)議。對(duì)于cocotbext-pcie里面牽涉到的鏈路層的ACK/NAK,牽涉到的PCIe背景,聊做記錄。 ????本文僅結(jié)合PCIe Spce

2023-06-25 10:31:17 1458

1458

AMD FPGA自帶PCIE硬核,實(shí)現(xiàn)了PCIE協(xié)議,把串行數(shù)據(jù)轉(zhuǎn)換為并行的用戶數(shù)據(jù)

2023-07-14 15:53:40 878

878

碼的分類及其作用。 Modbus協(xié)議功能碼分類: Modbus協(xié)議定義了一系列的功能碼,每個(gè)功能碼都代表不同的請(qǐng)求類型和操作。根據(jù)Modbus規(guī)范,功能碼可以分為以下幾類: 讀功能碼(0x03和0x04): 功能碼0x03用于讀取包含連續(xù)多個(gè)寄存器(16位數(shù)據(jù)塊)的保持寄存器。 功能

2024-01-31 14:47:14 749

749 已全部加載完成

電子發(fā)燒友App

電子發(fā)燒友App

評(píng)論