本篇先總結一些APB總線的知識點。

1 學習資料

·由于師兄給的設計要求是AMBA2.0,所以參考了ARM官網關于AMBA2.0的技術手冊《AMBA? Specification (Res2.0)》,這本技術手冊英文比較好理解,篇幅也很短,可以直接看英文版,問題不大。

·在這本書中,介紹了AMBA基本信號、AHB總線、ASB總線、APB總線,由于寫的項目主要設計APB接口,所以在本文中主要介紹APB的部分。

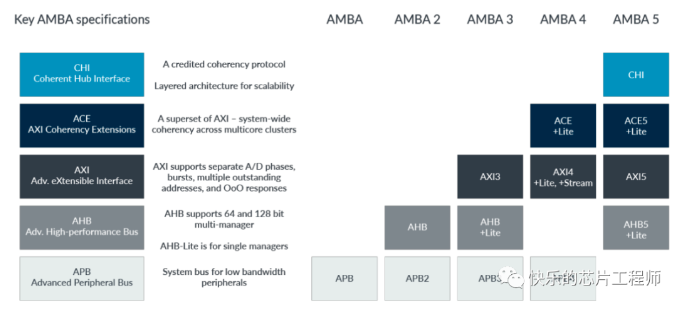

AMBA(Advanced Microcontroller Bus Architecture)高級處理器總線架構;

APB(Advanced Peripheral Bus)高級外圍總線;

2 AMBA APB的優點

先說用途和目的:APB可以實現與低功耗、低速設備進行數據傳輸。

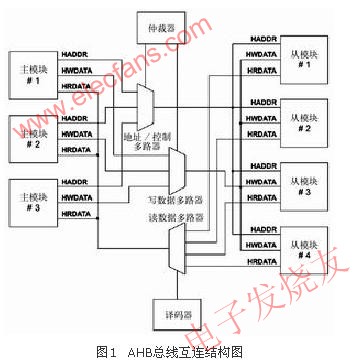

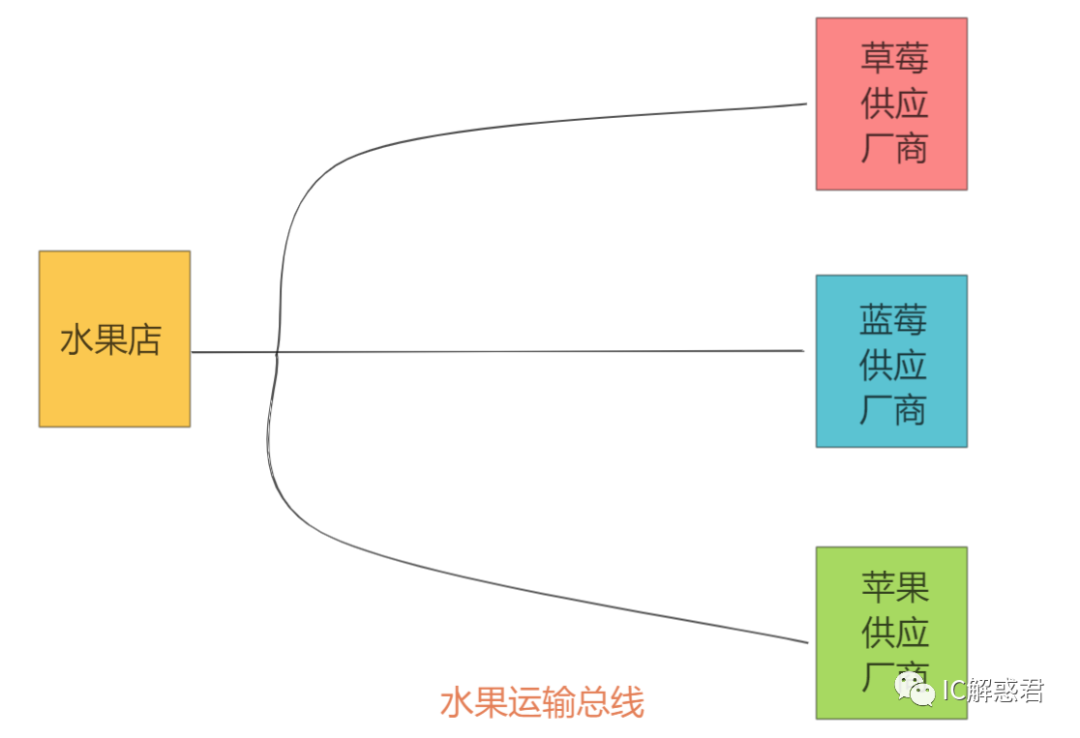

接下來介紹其特點:AMBA APB總線可以用在低帶寬和不需要高性能的外設上(即低速且低頻率的外設);可以將APB視作AHB的二級總線;

·低功耗(APB總線信號端口比較簡單,復雜度低,低頻工作環境等因素都可以降低功耗)

·低成本(用的廣泛,可以兼容很多IP,降低開發成本)

·低帶寬(信號的位寬有限,而且簡單的外設也不需要多位寬)

·無流水線結構(區別于AHB,但效率沒有AHB高)

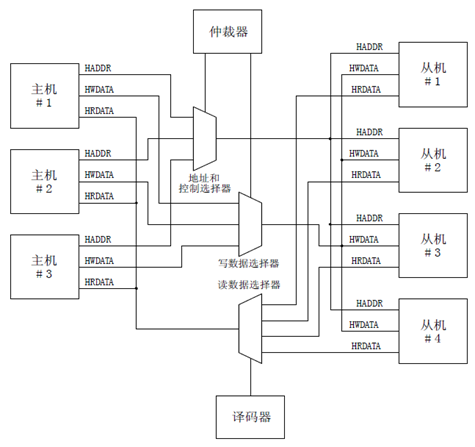

·APB總線中,唯一的master就是APB Bridge,其他設備都是slave。

3 典型的AMBA APB端口信號(APB Bridge、slave為例)

3.1 模塊端口示例(所有的AMBA APB信號使用P字母開始)

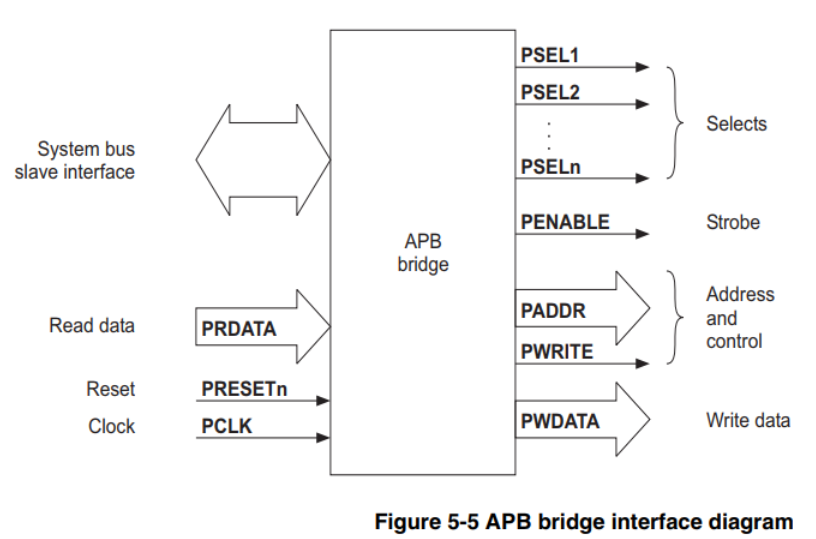

APB總線協議中唯一的master—APB Bridge模塊結構:

關于system bus slave interface信號的來源,其實是有一個AHB-APB模塊和APB進行連接通信;

實際的信號流:cortex M3核-》bus matrix -》 AHB-APB -》 APB bridge -》 APB slave(后續可能會提到,要看我能不能實現軟硬結合了~)

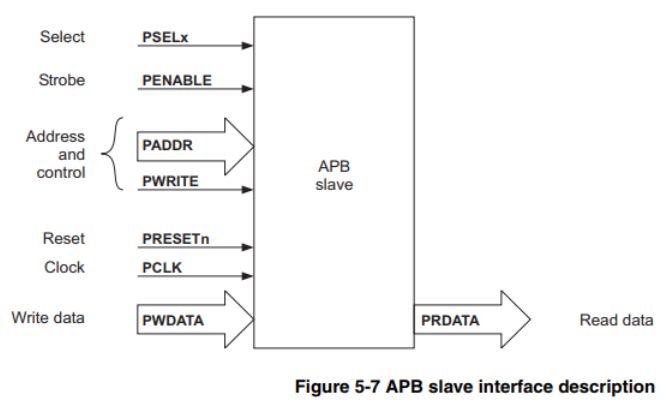

APB中slave模塊結構:

APB Bridge和slave的信號其實是可以進行互聯的,APB Bridge(master)將控制信號和數據傳輸給slave,slave將部分信號傳輸給APB Bridge(master),從而完成通信;

信號及其來源:

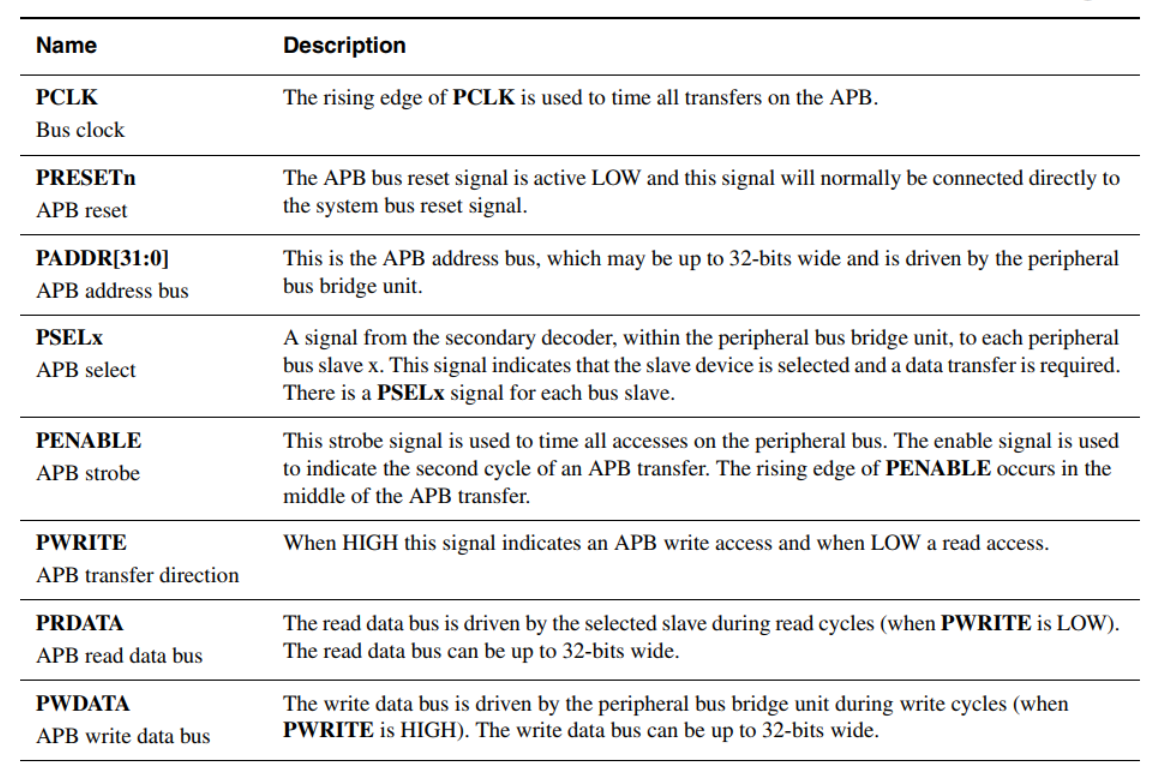

SignalSourceDescription

PCLK時鐘源系統時鐘,傳輸發生在上升沿

PRESETn復位源復位信號,低使能

PADDR[31:0]APB橋地址信號,最高可達32位

PSELxAPB橋由APB bridge產生的信號,針對每一個Peripheral Bus Slave片選信號,表示x從機是否被選中

PENABLEAPB橋使能信號,標記傳輸使能

PWRITEAPB橋讀/寫控制信號,高位寫,低為讀

PWDATAAPB橋寫數據

PREADY從機標記從機是否已將數據發送到總線,高為ready(給出的slave沒有,但是官方slave代碼會有的,常設定為assign PREADY = 1)

PRDATA從機讀數據

PSLVERR從機故障信號,為高時發生故障(給出的slave沒有,但是官方slave代碼會有的,常設定為assign PSLVERR = 0)

3.2 PCLK、PRESETn:首先來進行分析,一個APB總線信號肯定要有時鐘信號PCLK來管理數據傳輸,其次是異步復位信號PRESETn 信號,這兩個信號是基本所有模塊的基礎。

3.3 PADDR[31:0]:這里表示地址信號(地址與存儲的數據是一一對應的關系,要求是對齊的關系,這里沒有涉及),一般以16進制表示形式,也就是0xXXXX XXXX;

3.4 PSELx:在一個APB總線中,只有一個master(也就是APB橋),但是可以接很多slave。至于選擇哪個slave就需要PSELx信號進行選擇;

3.5 PENABLE:傳輸使能信號,表示當前傳輸是否有效;

3.6 PWRITE:讀寫信號,APB Bridge需要進行寫傳輸時,該信號拉高;APB Bridge需要進行讀傳輸時,該信號拉低。(這個信號是告訴slave的,表示master正在想干什么事情)

3.7 PRDATA:讀數據(slave傳輸給master)

3.8 PWDATA:寫數據(master傳輸給slave)

附上ARM官方文檔的APB信號端口,供大家欣賞:

4 APB狀態機

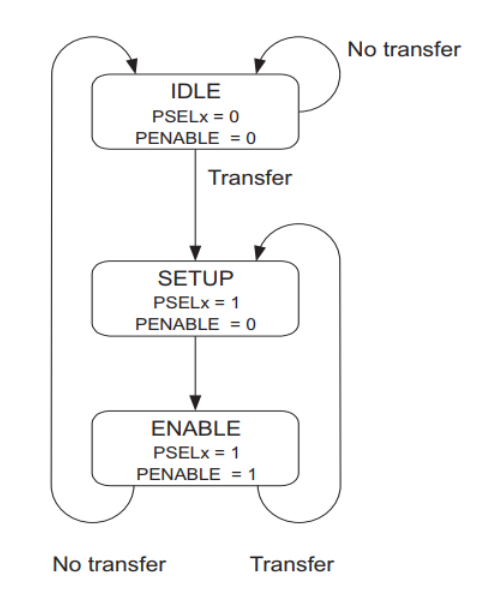

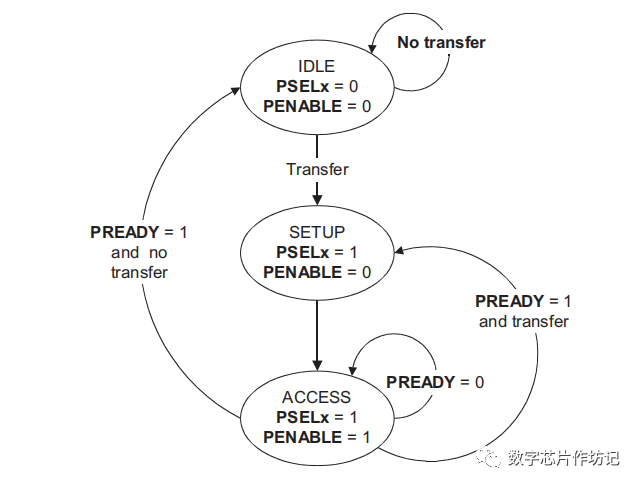

官方文檔的狀態機:

狀態功能

IDLE默認狀態(我的理解是一種待機狀態)

SETUP總線的傳輸狀態來到SETUP狀態,slave的PSELx被選中(拉為1),但只保持一個時鐘周期。之后就要在下一個時鐘上升沿時候,來到ENABLE狀態

ENABLE在ENABLE狀態,PENABLE被拉高。在SETUP和ENABLE狀態,地址、寫信號、選擇信號都要保持穩定。在ENABLE狀態也只持續一個時鐘周期,如果沒有后續傳輸,總線又將回到IDLE狀態。如果有后續傳輸,總線將回到SETUP狀態。

從狀態機來看,APB對每一筆數據的傳輸,都需要兩個周期(省略掉IDLE),因此APB數據不適合流水線架構的模塊設計中。

(注意:在ENABLE回到SETUP狀態時,對于地址信號、寫信號、選擇信號的要求并不高,可以出一點小錯誤,因為簡單外設接受數據的速度還可以,后期出一些小問題影響不大)

5 寫傳輸和讀傳輸時序邏輯

5.1 寫傳輸:

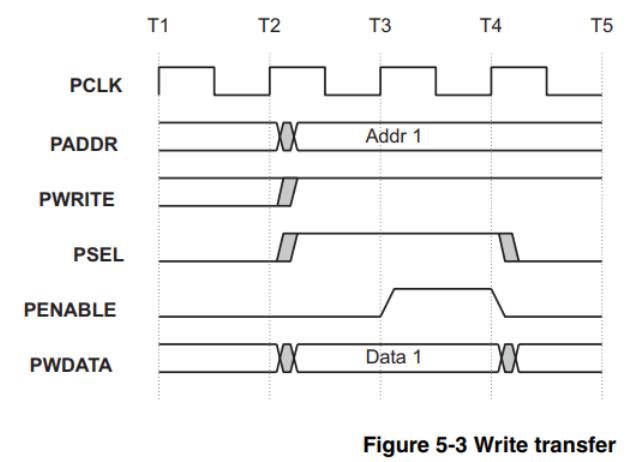

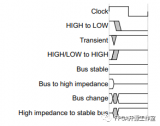

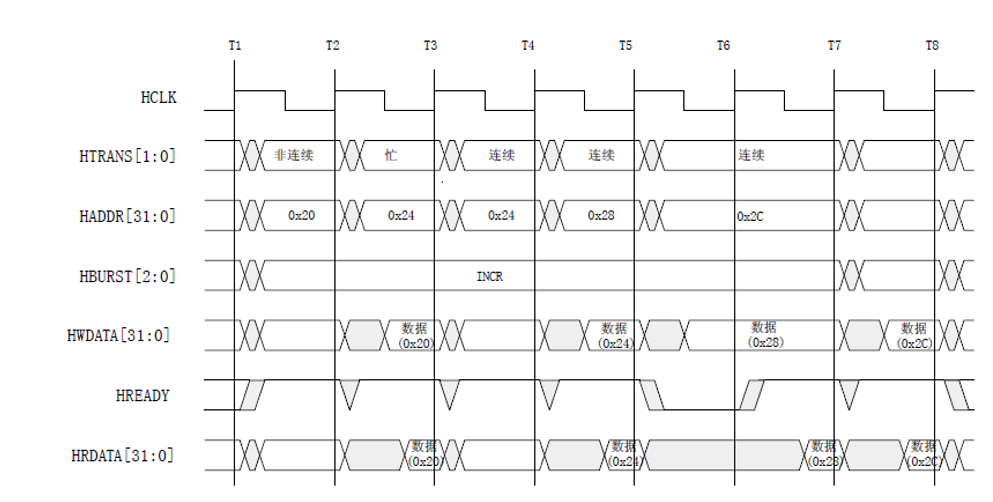

先放出寫傳輸時序圖:

分析(注意,我理解的這個時序圖是從master的角度進行分析的,要結合master和slave的共有信號去理解時序圖):

[T1,T2)對應IDLE狀態 (這里采用閉區間、開區間的表達方式,用作表示T1上升沿起作用,但T2上升沿還未起作用,下同);

[T2,T3) 對應SETUP狀態。此時,由于T2上升沿的有效,電路狀態開始發生改變,在這個時鐘周期內,PADDR、PWRITE(拉為1)、PSEL(選中哪個slave)、PWDATA等信息開始加載到數據線上,注意此時PENABLE還沒有起效果,只起到一種預加載的效果。

[T3,T4)對應ENABLE狀態。此時,由于T3上升沿有效,PENABLE開始有效,在這個時鐘周期內,上個狀態選中的slave開始接受PADDR、PWRITE、PSEL、PWDATA等信息。

[T4,T5)階段,由于T4時刻上升沿開始觸發,導致PENABLE和PSEL信號恢復默認值,等待下一次指令進行5.2 讀傳輸:

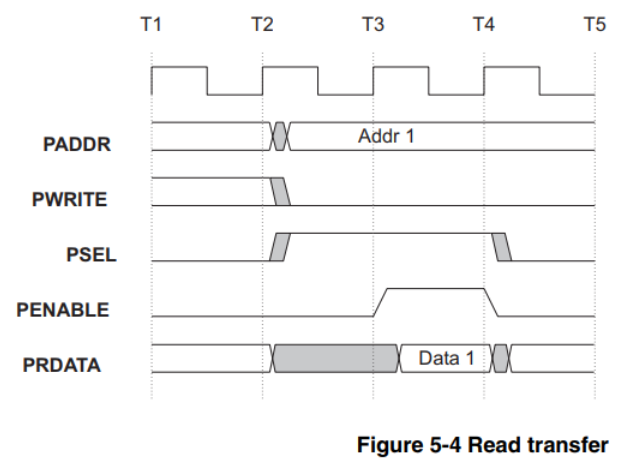

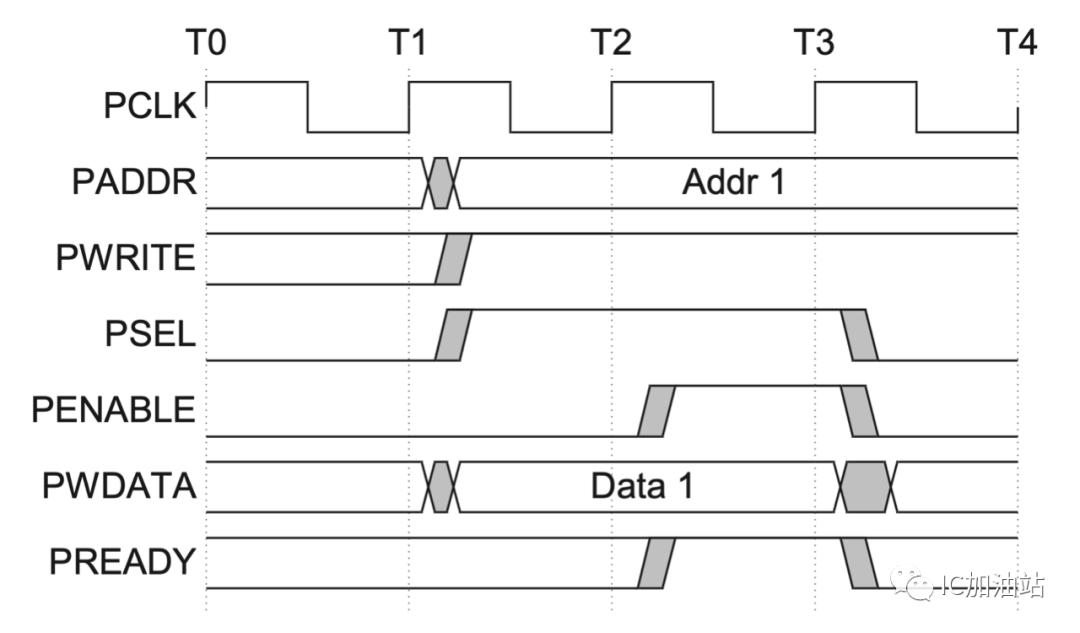

放出寫傳輸時序圖:

分析(注意,我理解的這個時序圖是也從master的角度進行分析的,要結合master和slave的共有信號去理解時序圖):

[T1,T2)對應IDLE狀態;[T2,T3) 對應SETUP狀態。此時,由于T2上升沿的有效,電路狀態開始發生改變,在這個時鐘周期內,PADDR、PWRITE(拉為0)、PSEL(選中哪個slave)等信息開始加載到數據線上,注意此時PENABLE還沒有起效果,只起到一種預加載的效果。(注意此時沒有PRDATA數據線上沒有有效信息)

[T3,T4)對應ENABLE狀態。此時,由于T3上升沿有效,PENABLE開始有效,在這個時鐘周期內,上個狀態選中的slave開始接受PADDR、PWRITE、PSEL等信息,并傳輸PRDATA信號給master。 4. [T4,T5)階段,由于T4時刻上升沿開始觸發,導致PENABLE和PSEL信號恢復默認值,等待下一次指令進行何種操作。

一些疑惑

·為什么讀操作在第一個時鐘周期里的PRDATA沒有有效數據?

在對比寫操作和讀操作的過程中,發現讀操作在SETUP時鐘周期里沒有有效數據,個人理解是因為低速外設準備數據的速度太慢了,如果在SETUP時鐘周期就要求有效數據,很有可能傳輸不了正確的數據,索性降低要求,讓其在ENABLE時鐘周期才有效。

而APB Bridge準備數據的速度很快,因此可以在SETUP狀態就可以準備好數據,方便在ENABLE狀態給外設數據。

(待續)

6 APB總線連接外設應用

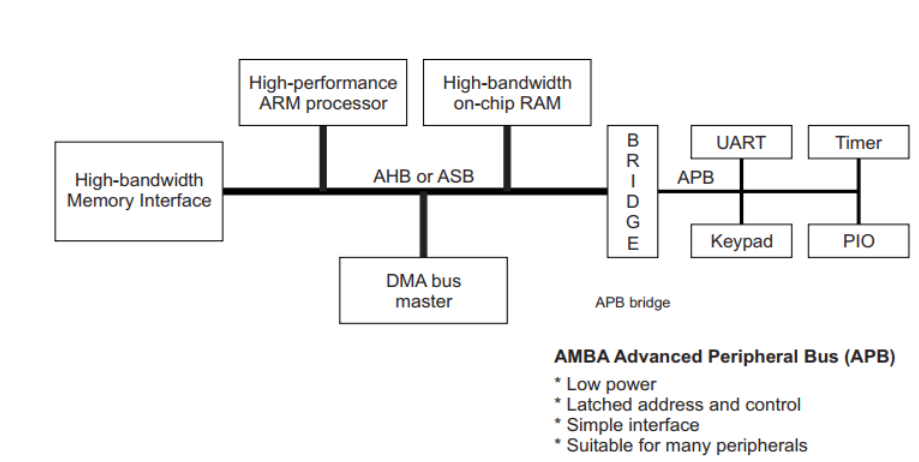

官方文檔給出的一些應用:

從這里可以看出對于AMBA APB總線來說,只有一個master(APB Bridge),同時可以掛載多個slave(比如uart,keypad,timer,PIO)。

審核編輯:黃飛

電子發燒友App

電子發燒友App

評論