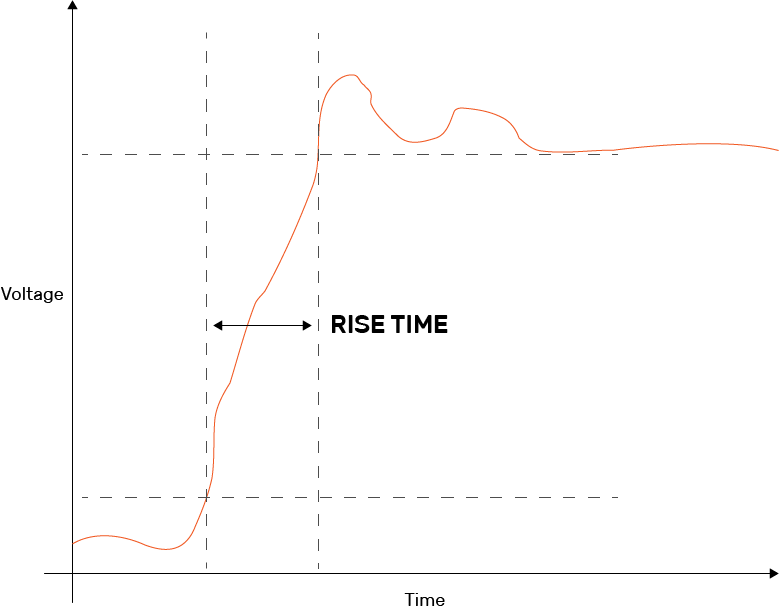

隨著高速信號的普及,迫切需要保證這些信號接口能夠維持正確時序和保真度的措施。上升時間一般在亞納秒級,傳輸延時在納秒級。系統對時序的要求越來越嚴格,如果不對信號通路進行認真分析,將無法獲得精確的時序。

引言

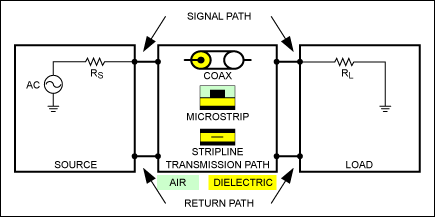

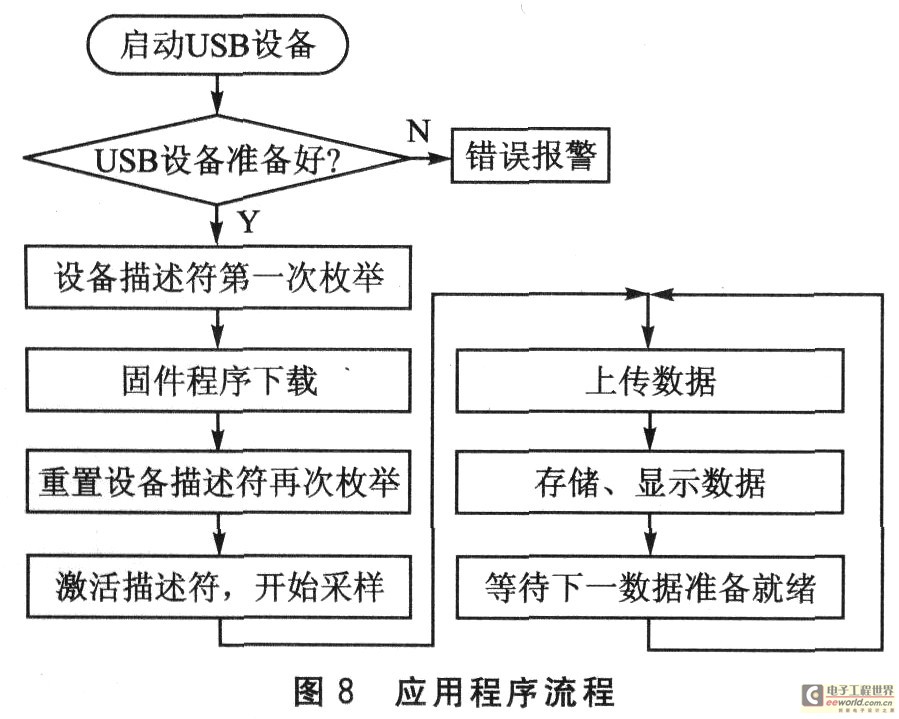

本文的目的并不是推導傳輸線方程,解釋為什么會出現以下的情況,我們的目的是說明在什么地方需要使用它以及如何使用。文章通過實際案例中的傳輸線理論,闡述可能出現的結果,并推薦了相應的解決方案來避免一些常見錯誤。典型的高速信號通路如圖1所示。高速信號通路中經常出現的問題有:

不希望的振蕩

波形振鈴

過沖和下沖

在波形上升沿和下降沿出現的邊沿效應

上面所有這些效應會引入大量的時序誤差,某些情況下還會產生直流誤差,從而劣化了信號通路。優化信號通路可避免這些誤差,在下面的案例研究中將進行演示。

圖1. 簡單的高速傳輸線

圖1所示的電路中,源和負載阻抗都是電阻。對于下面的案例研究,我們將保持其電阻性,以便簡化分析。傳輸線的特性阻抗一般定義為ZO。在理想情況下,RS?= ZO?= RL。對于這些相同的案例研究,我們使用50Ω的阻抗。分析中可以采用任意阻抗,結果類似。

基本傳輸線理論

傳輸線有兩種基本簡化電路。

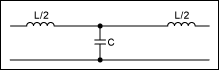

無損傳輸線

圖2所示為無損傳輸線。它之所以是無損的,是因為沒有產生損耗的阻性元件。

圖2. 無損傳輸線

采用四種阻抗定義無損和有損傳輸線。

L = 單位長度特征電感

C = 單位長度特征電容

R = 單位長度特征電阻

G = 單位長度特征電導

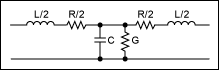

有損傳輸線

如果R << jωL,G << jωC,那么可以忽略R和G的有損項。這是對圖3的假設,由此,我們只需要參考圖2。

圖3. 有損傳輸線

兩個基本特征參數定義了圖2所示傳輸線。

特征阻抗(ZO),其中:

;注意:這是一個實數。

;注意:這是一個實數。

傳輸時間(τ),其中:

典型線路阻抗

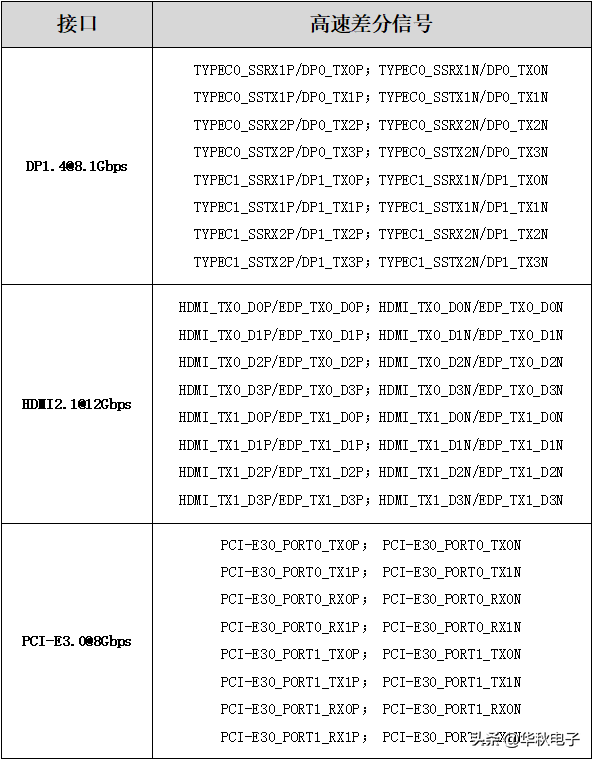

表1列出了一些常見導線的典型阻抗和傳輸延時。

表1. 線路阻抗的典型特征參數

?

| Type of Line | ZO?(Ω) | L (nH/in) | C (pF/in) | τ?(ns/ft) |

| Single wire,well above ground | 575 | 50.8 | 0.152 | 1.05 |

|

Micro-strip on FR4 board W = 1.5mm,T = 0.035mm,H = 0.794mm? W = 2.3mm,T = 0.035mm,H = 0.794mm? W = 0.7mm,T = 0.035mm,H = 0.794mm? |

50.71 36.09 76 |

7.17 4.71 10.45 |

2.79 4.05 1.81 |

1.65 1.65 1.65 |

| Twisted pair | 100 | 7.5 | 0.75 | 2.3 |

| Coaxial | 50 | 6.35 | 2.54 | 1.52 |

?

傳輸反射

現在,我們通過觀察三個基本阻抗來研究信號通路對信號保真度的影響。

RS?= 驅動源阻抗。它會隨著應用而變化。某些應用中,RS為50Ω,有的應用則是75Ω;如果由具有反饋通路的緩沖器直接驅動,它可能是數十歐姆甚至更低。當輸出來自CMOS緩沖器時,則可能是幾千歐姆。

ZO?= 信號通路或傳輸線的阻抗。該信號通路也會因為我們所選擇的單線、同軸電纜、微帶線或帶狀線的不同而變化。信號通路還具有另外一個更重要的參數,即,信號通過整個通路的時間(τ)。

RL?= 負載,這是我們定義的負載。在下面的案例中它為電阻,隨應用的不同而變化。

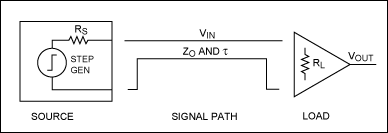

所有三個參數都會以不同的方式影響信號,利用圖4所示設置分析其影響。這一設置是所有案例研究中所采用的基本電路。

圖4. 測試原理圖

圖4中類似的設置會產生兩種反射。一是源反射系數(SRC),即RS和ZO的相互作用,二是負載反射系數(LRC),即ZO和RL的相互作用。所有這些反射系數都表示反射回來的電壓,其定義如下:

以及

案例研究

下面的四個案例研究以圖4中的設置為參考。唯一變化的參數是RS、ZO和RL。

案例1 (RS?= 0Ω,RL?= ∞,ZO?= 50Ω,τ?= 2.5ns)

規格與其最接近的實際案例是驅動ECL輸入的低阻緩沖器。

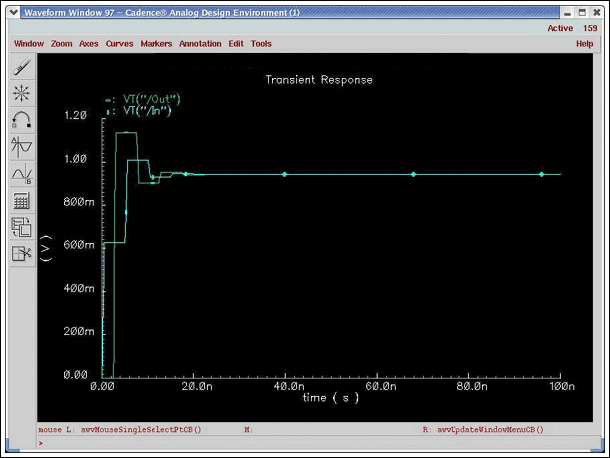

圖4中的發生器提供幅度為1V、上升時間(tr)為500ps的階躍脈沖。具有上述阻抗的VOUT仿真曲線如圖5所示。

圖5. RS?= 0Ω,RL?= ∞,ZO?= 50Ω,τ?= 2.5ns

這一設置的問題是在輸出節點VOUT出現了滿幅振蕩。這一案例有些不切實際,因為我們一般不會驅動零阻抗的傳輸線,也不會有無窮大的負載。然而,這達到了突出問題的目的,即,如果阻抗和所采用的負載接近時,將出現這一情況。

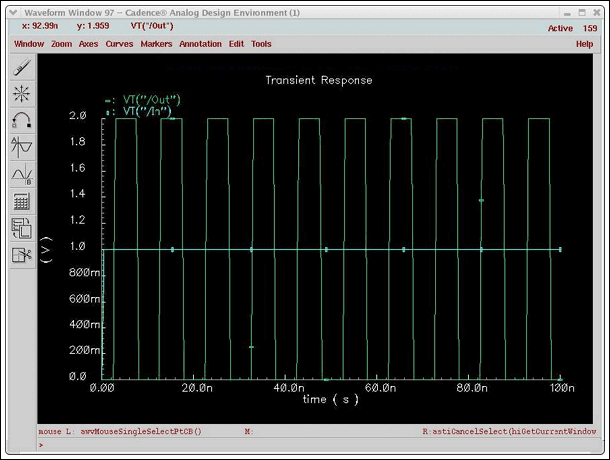

案例2 (RS?= 10Ω,RL?= 10kΩ,ZO?= 50Ω,τ?= 2.5ns)

案例2要更實際一些,它演示了使用低阻緩沖器,在這個例子中為10Ω,驅動帶有高阻抗負載的50Ω傳輸線。結果如圖6所示。在這一曲線中可以看到,在輸出節點VOUT觀察到了非常普遍的振鈴問題;振鈴最終衰減下去。

圖6. RS?= 10Ω,RL?= 10kΩ,ZO?= 50Ω,τ?= 2.5ns

案例3 (RS?= 30Ω,RL?= 500Ω,ZO?= 50Ω,τ?= 2.5ns)

案例3和部分典型設置非常相似。這里,輸入緩沖阻抗為30Ω,傳輸線是50Ω,負載為500Ω。測試設置和案例1、案例2的相同,但是振蕩或者振鈴大大降低了。我們在圖7曲線上所看到的是VOUT節點輸出波形的標準過沖和下沖。

圖7. RS?= 30Ω,RL?= 500Ω,ZO?= 50Ω,τ?= 2.5ns

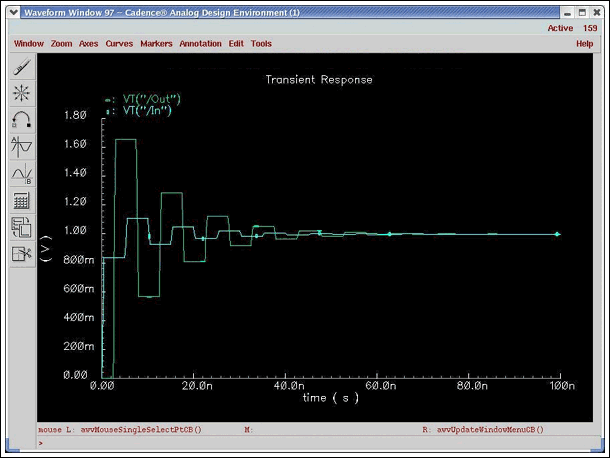

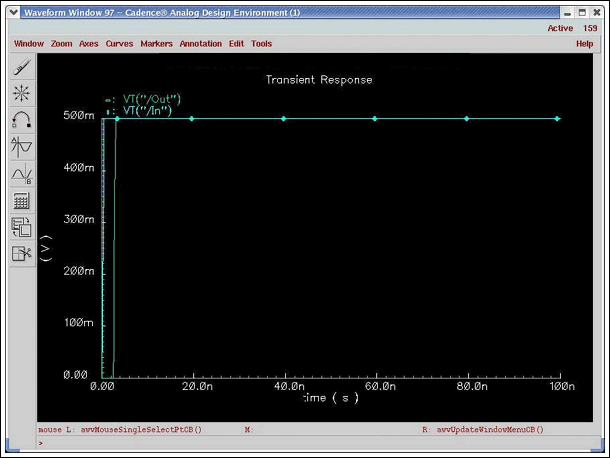

案例4 (RS?= 50Ω,RL?= 50Ω,ZO?= 50Ω,τ?= 2.5ns)

最后,案例4闡述了輸入和傳輸線理想匹配以及傳輸線和輸出相匹配的情況。圖8所示為我們希望在VOUT節點出現的波形,沒有振蕩、振鈴或過沖。

圖8. RS?= 50Ω,RL?= 50Ω,ZO?= 50Ω,τ?= 2.5ns

案例結果討論

這里所討論的四個案例代表了很多可能案例的集合,這些案例出現的問題和上面看到的相似。顯然,我們應該對源、傳輸線和負載進行匹配才能得到最佳結果。但是,實現匹配要比上面案例所建議的措施困難得多。需要仔細研究:

a.?

源

源需要有匹配阻抗以及較大的帶寬,但這并非總是可行。而且,有時源的邊沿可能已經有缺陷,例如,振鈴、過沖、下沖和下陷等,從而使匹配問題更加復雜。

?

b.?

傳輸線

傳輸線一般是印刷電路板(PCB)走線、較長的同軸電纜、簡單的導線或者雙絞線電纜等。這種通路的模型并不總是可以簡化為50Ω的阻抗。其阻抗分布可能非常復雜,走線本身的實際形狀使得阻抗分配更加復雜。

?

c.?

負載

負載并不總是簡單的阻性負載。還需考慮負載連接有其它復雜阻抗的問題。加入連接器也是負載變得更加復雜。

源、信號通路和負載之間沒有進行仔細的匹配會導致輸出產生振蕩、有害的振鈴效應等。圖5、圖6和圖7非常清楚地顯示了這些問題。

這四個案例還說明了我們能夠減小甚至消除振鈴問題的途徑。對于這些案例,提高低阻抗源的輸出阻抗就能夠有效地增大輸出阻抗,使其接近所需要的50Ω阻抗。對高阻抗負載進行匹配也能夠有效地得到50Ω阻抗。

需要注意的是脈沖邊沿振鈴和假象會改變波形,它對系統性能的影響很大。特別是這些假象出現在比較器輸入時,會導致錯誤的觸發。假象還會增大信號通路的延時。優化信號通路有助于減小這些有害的影響。

分析并驗證結果

反射圖

理論上,您可以畫出眾所周知的“反射”圖,驗證上面所有案例的結果。這是非常有用方式,能夠更好地理解這些信號是怎樣出現在輸出端的。雖然反射圖很有幫助,但是需要一定的時間,如果電路比較復雜,也很難使用。最簡單的方法是下面仿真一節所建議的SPICE仿真。使用SPICE仿真器之一對這四個案例進行仿真。

仿真

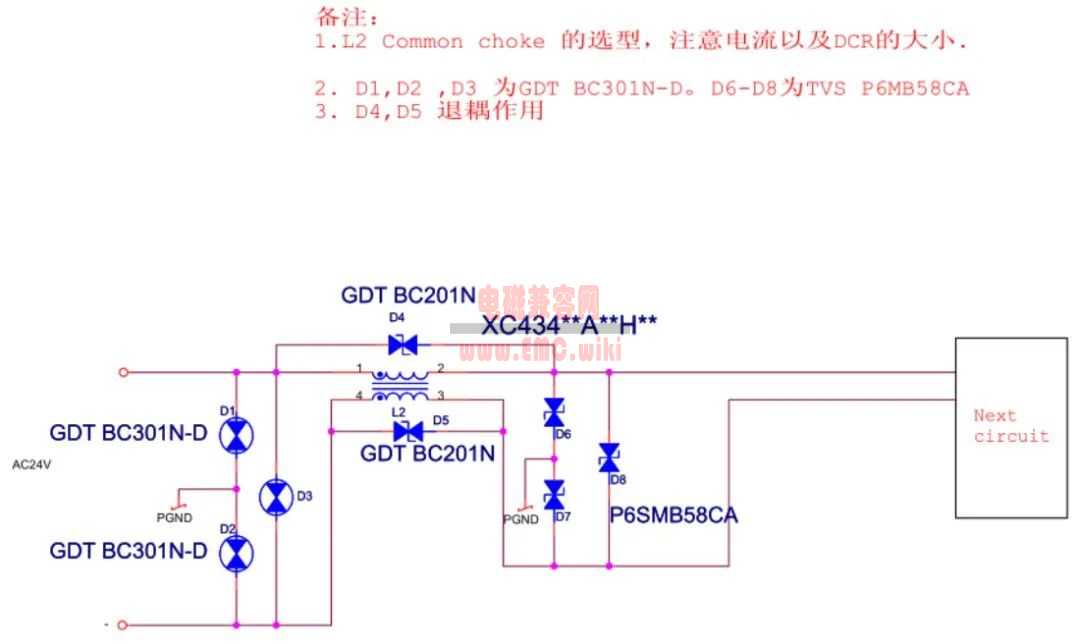

優化信號通路最快的方法是使用SPICE型仿真器。電路如圖4那樣簡單。記住以下幾點非常重要。

使用精確的源模型,如圖4所示。只有源的輸出部分需要建模。這一模型應表示出串聯電阻、串聯電感和并聯電容。

圖4中表示的傳輸線不論是PCB走線還是同軸電纜、雙絞線等,都需要建立準確的模型。

最后,對圖4中的負載也需要進行精確建模,以反映出電阻、電感和并聯電容。

對源、傳輸線和負載進行建模較好的工具是時域反射計(TDR)。使用TDR可以測量R、L和C等元件,從而建立更準確的模型。

總結

很容易看出,如果不能仔細地匹配整個信號通路上的源、傳輸線和負載,將會出現信號劣化。上面討論的四個案例對此進行了演示。如果達不到匹配,會有無法預見的誤差出現。使用SPICE仿真器及其簡化建模方法能夠很快地找到問題所在。利用這些信息,可以迅速設計并驗證解決方案。

隨著頻率的升高,需要投入大量的精力對整個信號通路進行建模和仿真。這樣可以保證最準確、可預測的結果。

審核編輯:黃飛

電子發燒友App

電子發燒友App

評論