一種嵌入式系統(tǒng)實現(xiàn)的JTAG調(diào)試器

JTAG 作為一個通用的標準器件功能測試接口, 具有靈活高效、易于實現(xiàn)等優(yōu)點, 是微控制器、微處理器、DSP、SoC 等器件的重要外部接口。它不但可以用來測試內(nèi)部功能模塊狀態(tài), 而且可以實現(xiàn)在線調(diào)試(ICE)功能。

??????

ARM系列處理器正是通過JTAG 接口使用內(nèi)部集成的ICE 功能, 并采用這種方式實現(xiàn)在線調(diào)試。此外CPLD、FPGA 等器件大多都可以使用JTAG 接口實現(xiàn)在線編程或下載。因此,JTAG 接口已經(jīng)成為復雜芯片系統(tǒng)的必備接口, 在芯片測試、調(diào)試及實現(xiàn)其他特殊功能方面發(fā)揮著重要作用。

基本原理

JTAG 標準即IEEE 1149.1 標準。聯(lián)合測試行動組JTAG(Joint Test Action Group ) 起草了邊界掃描測試BST(Boundary Scan Testing)規(guī)范, 該標準為數(shù)字集成電路規(guī)定了一個測試訪問口(TAP) 和邊界掃描結(jié)構(gòu),解決了由于數(shù)字電路高度集成化帶來的一些測試難題。它還提供了一種訪問和控制芯片內(nèi)部仿真(ICE) 模塊的方法, ICE 模塊一般包括內(nèi)部掃描和自測試的功能, 可以很好地支持集成電路的開發(fā)。

JTAG 標準工作原理

邊界掃描技術(shù)的基本思想是在靠近芯片的輸入輸出管腳增加一個移位寄存器單元。通過這些邊界掃描寄存器單元, 可以實現(xiàn)對芯片輸入輸出信號的觀察和控制。另外, 靠近芯片輸入輸出管腳的邊界掃描(移位) 寄存器單元可以相互連接起來, 在芯片的周圍形成一個邊界掃描鏈(Boundary- Scan Chain) 。一般的芯片都會提供幾條獨立的邊界掃描鏈, 用來實現(xiàn)完整的測試功能。

在JTAG標準中, 寄存器被分為兩大類: 數(shù)據(jù)寄存器(DR- Data Register)和指令寄存器(IR- Instruction Register),邊界掃描鏈寄存器即為一種很重要的數(shù)據(jù)寄存器, 邊界掃描鏈可用來觀察和控制芯片的輸入輸出。指令寄存器用來實現(xiàn)對數(shù)據(jù)寄存器的控制。TAP 是一個通用的端口, 通過TAP 可以訪問芯片提供的所有數(shù)據(jù)寄存器和指令寄存器, 對整個TAP的控制是通過TAP控制器完成的。TAP包括5個信號接口: (1)TCK(Test Clock), 為TAP操作提供了一個獨立的基本的時鐘信號。(2)TMS(Test-Mode Selector) , 用來控制TAP狀態(tài)機的轉(zhuǎn)換。(3)TDI(TestData Input), 是JTAG指令和數(shù)據(jù)的串行輸入端。在TCK的上升沿被采樣, 結(jié)果送到JTAG寄存器中。(4)TDO(Test Data Output), 是JTAG指令和數(shù)據(jù)的串行輸出端。在TCK的下降沿被輸出到TDO。(5)TRST, 是JTAG電路的復位輸入信號, 低電平有效。

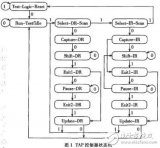

通過TAP控制器的狀態(tài)轉(zhuǎn)移即可實現(xiàn)對數(shù)據(jù)寄存器和指令寄存器的訪問, 從而實現(xiàn)對JTAG測試電路的控制。TAP控制器共有16 種狀態(tài), 如圖1 所示。通過測試模式選擇TMS 和時鐘TCK可控制狀態(tài)的轉(zhuǎn)移。

指令寄存器允許特定的指令被裝載到指令寄存器當中, 用來選擇需要執(zhí)行的測試, 或者選擇需要訪問的測試數(shù)據(jù)寄存器。每個支持JTAG調(diào)試的芯片必須包含一個指令寄存器。JTAG標準要求芯片支持的基本指令有:EXTEST、INTEST、SAMPLE/PRELOAD、BYPASS、HIGHZ等。

ARM7TDMI 調(diào)試原理

從功能上看, ARM7TDMI 處理器主要包括三大部分:

(1)ARM CPU Main Processor Logic , 包括了對調(diào)試的硬件支持; (2)嵌入式ICE- RT Logic , 包括了一組寄存器和比較器, 用來產(chǎn)生調(diào)試異常、設(shè)置斷點和觀察點; (3)TAP控制器, 它通過JTAG接口控制和操作掃描鏈。

ARM7TDMI 提供了4 條掃描鏈, 分別是掃描鏈0、1、2 和3。通過掃描鏈0可以訪問ARM7TDMI內(nèi)核的外圍電路,包括數(shù)據(jù)總線。該掃描鏈長度為113位, 具體包括數(shù)據(jù)總線的0 ̄31位、內(nèi)核控制信號、地址總線的0 ̄31 位、嵌入式ICE-RT的控制信號等。掃描鏈1是掃描鏈0的子集, 長度為33位, 具體包括數(shù)據(jù)總線的0 ̄31位和BREAKPT信號,掃描鏈1比掃描鏈0的長度短了很多,通過掃描鏈1可以更快地將指令或數(shù)據(jù)插入到ARM7TDMI的內(nèi)部。掃描鏈2長度為38位, 該掃描鏈專門用來訪問嵌入式ICE-RT內(nèi)部的寄存器, 通過訪問嵌入式ICERT的內(nèi)部寄存器, 可以讓ARM7TDMI進入調(diào)試狀態(tài)、設(shè)置斷點、設(shè)置觀察點。通過掃描鏈3, ARM7TDMI可以訪問外部的邊界掃描鏈, 該掃描鏈用得很少。

ARM7TDMI 的調(diào)試狀態(tài)和正常運行狀態(tài)是有區(qū)別的。在正常運行狀態(tài)下, ARM7TDMI由MCLK( MemoryClock)驅(qū)動, 正常運行。在調(diào)試狀態(tài)下, ARM7TDMI的正常運行被打斷, 并且和系統(tǒng)的其他部分隔離開來。可以通過掃描鏈插入特定的ARM/THUMB指令來讀寫ARM7TDMI的內(nèi)部寄存器和修改內(nèi)存的內(nèi)容。在完成需要的操作后,可以用RESTART JTAG 指令讓ARM7TDMI返回到正常運行狀態(tài),恢復原來的運行。

JTAG 調(diào)試器的嵌入式系統(tǒng)實現(xiàn)

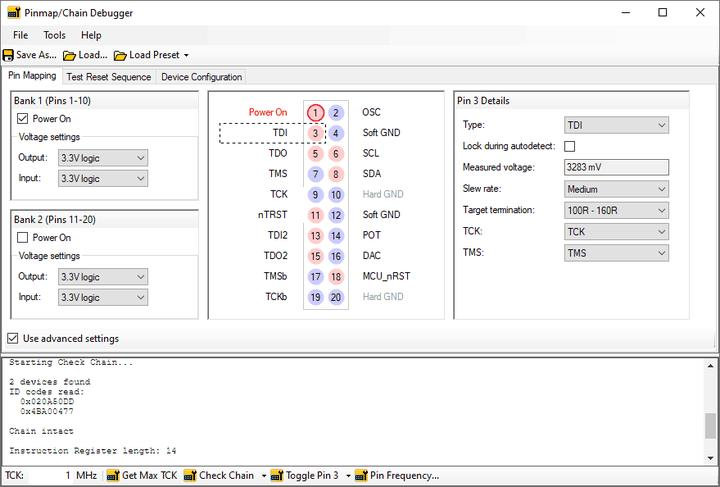

JTAG調(diào)試器硬件是以基于ARM7芯片的嵌入式系統(tǒng)實現(xiàn)的。該系統(tǒng)以帶以太網(wǎng)接口的ARM芯片S3C4510B為核心處理器, 以μClinux為嵌入式操作系統(tǒng)。JTAG調(diào)試器軟件主要包括兩部分: JTAG調(diào)試器與目標機的接口模塊和與調(diào)試主機的接口模塊。具體結(jié)構(gòu)框圖如圖2 所示。

嵌入式系統(tǒng)設(shè)計

設(shè)計并制作標準的S3C4510B應用系統(tǒng), 主要配置為2MBFLASH、16MBSDRAM、10/100Mbps 自適應以太網(wǎng)口、終端接口、并行I/O 接口等。利用S3C4510B 的通用I/O口中的P[4]、P[5]、P[6]、P[8]分別模擬JTAG標準中TAP的4個信號接口, 即TCK、TMS、TDI、TDO。

從軟件上看, 需要將μClinux 操作系統(tǒng)移植到設(shè)計制作的基于S3C4510B的JTAG調(diào)試器硬件平臺上, 以便開發(fā)基于網(wǎng)絡(luò)的調(diào)試器軟件。μCLinux是為沒有內(nèi)存管理單元(MMU)的處理器設(shè)計的一種嵌入式操作系統(tǒng),它繼承了桌面Linux的強大網(wǎng)絡(luò)功能,其內(nèi)核采用模塊化的組織結(jié)構(gòu),通過增減內(nèi)核模塊的方式來增減系統(tǒng)的功能。

通常, 在PC機上通過并口模擬JTAG時序,也可以按照標準仿真器設(shè)計JTAG調(diào)試器。與上述方案不同,本設(shè)計采用開放源代碼軟件設(shè)計JTAG調(diào)試器應用軟件,主要參考了Open- JTAG小組開發(fā)的通過PC機并口實現(xiàn)JTAG操作的軟件jtager - 1.0.0,將其中對PC 機并口的操作改為對S3C4510B口線的操作,通過設(shè)置S3C4510B的通用I/O口模式寄存器IOPMOD 的值可將P[4]、P[5]、P[6]設(shè)置為輸出模式,將P[8]設(shè)置為輸入模式,然后通過編程設(shè)置I/O口數(shù)據(jù)寄存器IOPDATA的值,控制P[4]、P[5]、P[6]、P[8]的狀態(tài)實現(xiàn)JTAG標準要求的時序。隨后,根據(jù)ARM7TDMI調(diào)試特性,修改操作代碼,增加通過網(wǎng)絡(luò)的遠程調(diào)試功能。

ARM7TDMI 的JTAG 指令實現(xiàn)

ARM7TDMI 的指令寄存器長度是4位, 通過TAP和JTAG接口, 可以把指令裝載到指令寄存器中。在CAPTURE-IR狀態(tài)下, 固定值B0001總是被裝載到指令寄存器中。在SHIFT- IR狀態(tài)下, 可以把ARM7TDMI支持的新指令從TDI串行輸入,同時固定值B0001會從TDO 串行輸出。通過輸出的這個固定值,可以判斷當前的操作是否正確。在UPDATE- IR狀態(tài)下, 新輸入的指令被裝載到指令寄存器中。在回到RUN- TEST/IDLE狀態(tài)后,新指令立即生效。

IDCODE和SCAN_N是ARM7TDMI調(diào)試中經(jīng)常用到的JTAG命令。IDCODE命令的二進制代碼是1110。IDCODE命令將Device Identification Code寄存器連接到TDI和TDO之間。Device Identification Code寄存器的長度是32 位,通過TAP可以讀到ARM7TDMI的ID。SCAN_N命令的二進制代碼是0010。ARM7TDMI提供了4 條掃描鏈,通過SCAN_N指令可以選擇需要訪問的掃描鏈。選擇掃描鏈的過程是:先把SCAN_N指令裝載到指令寄存器中,該指令會將長度為4位的掃描鏈選擇寄存器連接到TDI和TDO之間;通過TAP狀態(tài)的轉(zhuǎn)移便可使選擇的掃描鏈連接到TDI和TDO之間。

另外BYPASS、INTEST、RESTART等JTAG指令的實現(xiàn)方法與上面兩條指令的實現(xiàn)方法類似。

嵌入式ICE- RT 邏輯實現(xiàn)

嵌入式ICE- RT是ARM處理器內(nèi)部集成的在線仿真功能模塊,通過JTAG調(diào)試接口與外界交互,其中包含的常用寄存器如表1所示。

要訪問嵌入式ICE- RT內(nèi)部的寄存器,可通過掃描鏈2對Debug Control Register進行訪問。實現(xiàn)過程:通過TAP將SCAN_N指令寫入JTAG指令寄存器中,通過TDI將數(shù)值2寫到掃描鏈選擇寄存器中,即選擇了掃描鏈2,在通過掃描鏈2訪問任何嵌入式ICE- RT內(nèi)部寄存器之前,還需要用INTEST指令將當前通過SCAN_N指令選擇的掃描鏈置為內(nèi)部測試狀態(tài)。寫入INTEST指令的過程和寫入SCAN_N指令的過程類似。接下來就可以通過掃描鏈2訪問嵌入式ICE- RT內(nèi)部寄存器,實現(xiàn)對ARM7TDMI的基本調(diào)試功能。

ARM7TDMI 寄存器和內(nèi)存訪問的實現(xiàn)

邊界掃描鏈分布在ARM7TDMI的32位數(shù)據(jù)總線的周圍, ARM7TDMI每次取指令或者進行數(shù)據(jù)存儲時都要通過32位數(shù)據(jù)總線進行。這樣, 通過邊界掃描鏈1, 就可以插入新指令或者新數(shù)據(jù), 同時也可以捕獲出現(xiàn)在數(shù)據(jù)總線上的數(shù)據(jù)。通過這種方式, 可以檢查和修改ARM7TDMI的通用寄存器和系統(tǒng)內(nèi)存。

以讀取寄存器R0 的值為例, 介紹邊界掃描鏈1 的操作過程, 如圖3 所示。

讀取寄存器R0的值可以用指令STR R0, [R0] ( 機器碼為0xE5800000) 來實現(xiàn)。該指令可將寄存器R0 的值存儲到內(nèi)存單元R0中去。因為在ARM7TDMI處于調(diào)試狀態(tài)時, ARM7TDMI和外部是隔離開的, 所以該指令實際上不能訪問內(nèi)存單元, 也不會對內(nèi)存單元產(chǎn)生任何影響。使用指令STR R0, [R0]可使得寄存器R0的值出現(xiàn)在數(shù)據(jù)總線上, 這樣就可以通過掃描鏈1將其捕獲, 然后從TDO輸出。指令STR R0, [R0]的執(zhí)行需要兩個指令執(zhí)行周期。在第一個指令執(zhí)行周期, 執(zhí)行地址計算; 在第二個指令執(zhí)行周期, 將寄存器R0的值放到數(shù)據(jù)總線上去。對ARM寄存器寫操作及訪問內(nèi)存的方法與此類似,都是通過掃描鏈1, 只是所使用的指令不同而已。

網(wǎng)絡(luò)編程

通過網(wǎng)絡(luò)編程, 可以對目標系統(tǒng)實現(xiàn)遠程調(diào)試。圖4是PC與仿真器的網(wǎng)絡(luò)通信流程圖。網(wǎng)絡(luò)通信通過μClinux下的socket編程實現(xiàn), 首先PC(調(diào)試主機)通過網(wǎng)絡(luò)向仿真器發(fā)送命令, 仿真器通過統(tǒng)一的程序接口分析調(diào)試命令, 并將調(diào)試命令轉(zhuǎn)換成JTAG標準所要求的時序, 通過I/O口線發(fā)送到目標板; 然后目標板執(zhí)行命令,并將命令執(zhí)行后得到的調(diào)試信息返回給仿真器, 接著仿真器將調(diào)試信息通過網(wǎng)絡(luò)發(fā)送給PC, 這樣用戶在PC上便得到了調(diào)試信息。

JTAG調(diào)試器測試及部分執(zhí)行結(jié)果

本設(shè)計最終完成了一種在Linux終端下操作的JTAG調(diào)試器。調(diào)試器上電后便在μClinux 下自動運行調(diào)試器客戶端程序, 同時在PC的Cygwin環(huán)境下運行JTAG調(diào)試器服務器端程序jtager , 建立網(wǎng)絡(luò)連接。然后在Cygwin下鍵入用戶調(diào)試命令, 執(zhí)行下列操作: (1)寫目標板上的CPU狀態(tài); (2)讀寫編址在統(tǒng)一內(nèi)存空間的外部設(shè)備寄存器; (3)讀寫目標機上的RAM; (4)讀寫目標機上的固態(tài)存儲設(shè)備, 如Flash; (5)對嵌入式ICE- RT進行調(diào)試。

設(shè)計實現(xiàn)的調(diào)試器的用戶命令較多, 下面僅列出兩條典型命令I(lǐng)DCODE 和REG 執(zhí)行后的結(jié)果。

執(zhí)行IDCODE命令后, 讀出了一個基于S3C4510B的目標開發(fā)板內(nèi)的CPUID號, 從而得到Device ID="0x1F0F0F0F"。通過邏輯分析儀分析幾個JTAG接口信號的時序關(guān)系, 可以觀察到JTAG掃描連的訪問過程以及該過程中各種狀態(tài)的轉(zhuǎn)移, 結(jié)果與JTAG_調(diào)試原理吻合。

執(zhí)行RE命令后, 得到了寄存器R0~R15及CPSR內(nèi)容, 即讀出了目標開發(fā)板處理器S3C4510B在當前處理器模式下的所有寄存器值, 而且還可以通過其他命令對其進行修改。

此外, 通過掃描鏈2可以訪問嵌入式ICE- RT的17個寬度不同的內(nèi)部調(diào)試寄存器, 通過這些寄存器使目標ARM7TDMI分別進入調(diào)試狀態(tài)的3種方式, 即控制DBGRQ信號、斷點和觀察點, 實現(xiàn)在線調(diào)試功能。

本文實現(xiàn)的JTAG調(diào)試器具有基本的調(diào)試功能, 尚不具備完善的用戶操作界面, 特別是圖形操作界面, 另外網(wǎng)絡(luò)功能也需要進一步完善。但調(diào)試器的設(shè)計和實現(xiàn)方法對于設(shè)計類似調(diào)試器具有參考價值。為了提高JTAG調(diào)試器速率, 還可以采用CPLD或FPGA實現(xiàn)JTAG時序,通過存儲器形式與調(diào)試器CPU接口, 這將在提高速度的同時, 減輕調(diào)試器CPU的負擔。

電子發(fā)燒友App

電子發(fā)燒友App

評論