基于TMS320VC550的JPEG視頻壓縮系統的實現

1 引言

隨著網絡和多媒體技術的發展,視覺通信的重要性和需求急劇增加,如桌面視頻會議、移動終端、基于因特網的視頻通信等。這些視覺信息內涵豐富,但數據量大,必須壓縮數據。但采用多種方法壓縮圖像數據,其數據量仍然巨大,這就對計算機處理速度、傳輸介質、傳輸方法和存儲介質提出較高要求。因此,數據壓縮作為數據圖像處理的關鍵技術之一,對研究圖像壓縮編碼技術具有重要價值。

嵌入式微處理器中,DSP具有靈活、高速、便于嵌入式應用等優點,特別適合復雜算法處理的應用。數字視頻圖像壓縮系統利用DSP作為其嵌入式平臺,充分發揮其性能優勢,較好地提高編碼效率,滿足圖像實時處理需要。因此,這里介紹一種基于TMS320VC5509A型DSP的視頻壓縮系統。

2 靜止圖像的壓縮編碼標準JPEG

JPEG(Joint Photographic Experts Group)是由國際標準化組織(ISO)提出面向靜止圖像編碼的標準,其處理方法依次使用離散余弦變換、量化、Z行掃描、游程編碼和不變字長編碼。JPEG算法定義了以下4種運行模式:

(1)基于DCT順序型模式按照從左到右、從上到下的順序對圖像進行掃描和編碼,稱為基本系統。

(2)基于DCT遞增模式 按照從粗到細的順序對一幅圖像進行編碼,適用于傳輸時間長、用戶喜歡圖像從粗糙到清晰的場合。

(3)無失真編碼模式保證重建圖像與原始圖像完全相同。

(4)分層編碼 采用各種分辨率對圖像進行編碼。

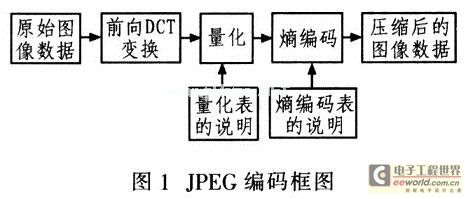

該系統采用基本系統模式。圖1是JPEG的編碼框圖。

3 硬件系統設計

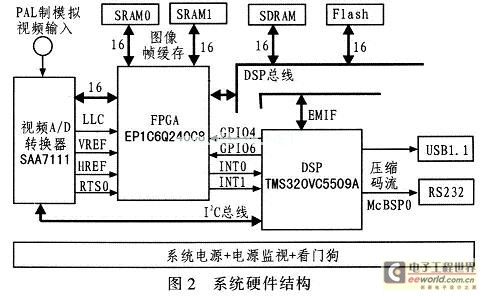

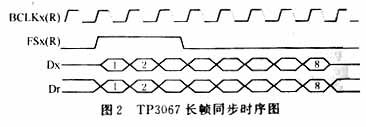

該視頻壓縮系統直接與PAL制攝像頭的輸出端相連,來采集、預處理和壓縮現場圖像,再以USB或RS232方式將處理后的圖像數據傳給上位機。圖2為視頻壓縮系統硬件結構圖。

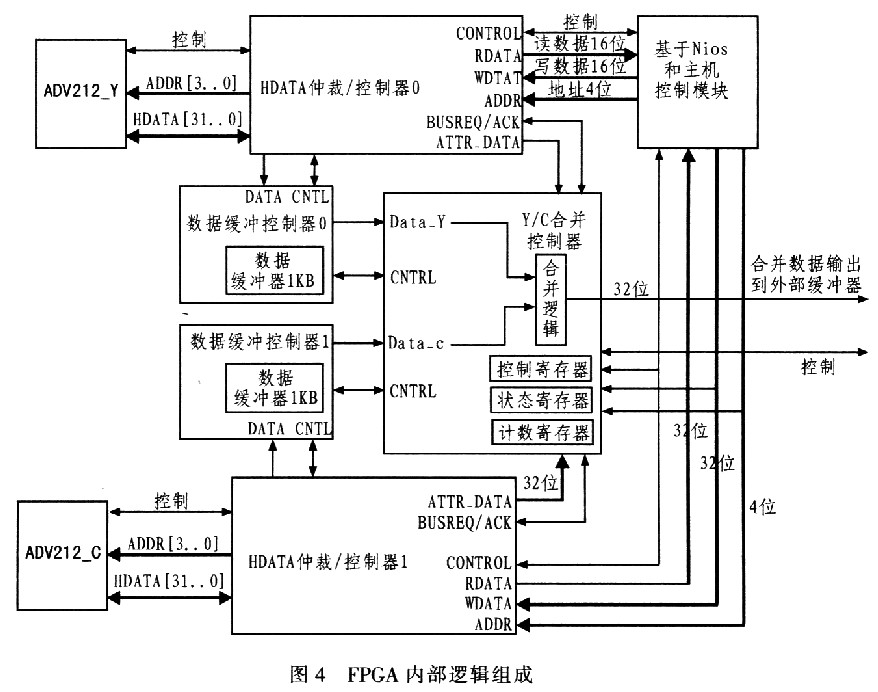

該系統硬件設計以TI公司的TMS320VC5509A型數字信號處理器為核心,包括視頻采集電路、FPGA預處理電路、存儲器擴展、系統電源和看門狗電路等。系統中TMS320VC5509A為中央處理器;SDRAM為DSP外擴數據存儲器;Flash為程序存儲器,用于系統上電自舉;模擬攝像頭與視頻 A/D轉換器負責視頻圖像采集;FPGA用于地址譯碼、隔行運算,控制兩片SRAM用于緩存視頻A/D轉換器轉換后的數字圖像。從系統設計成本考慮,這里選用Altera公司的可編程邏輯器件EPIC6Q240C8型FPGA。該器件是Cyclone系列器件中一款非BGA封裝的可用I/O引腳最多的 FPGA。

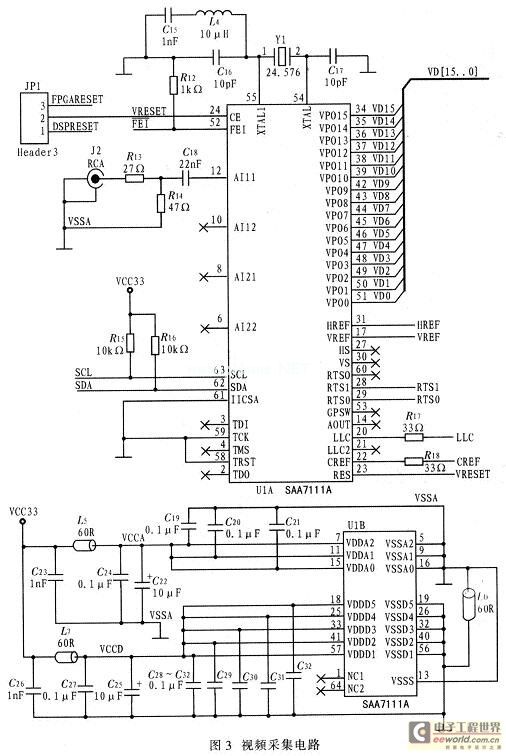

3.1 視頻采集電路

該系統選用的視頻解碼器為Philip公司的高性能視頻A/D轉換器SAA7111。該器件是一款廣泛應用于桌面視頻、多媒體、數字電視、圖像處理、視頻電話的高性能視頻輸入處理器件。該器件采用3.3 V的CMOS電路,高度集成模擬前端和數字視頻編碼器;包括2路模擬視頻處理通道,1個時鐘產生電路,1個自動箝位和自動增益控制電路,1個多制式數字解碼器,1個亮度/對比度/飽和度控制電路,以及色彩空間矩陣。SAA7111輸出為16位VPO總線,支持不同位寬的數據輸出格式。SAA7111支持的輸出格式包括:12位YUV411,16位YUV4:2:2,8位CCIR-656、16位565RGB以及24位的888RGB。圖3為視頻采集電路。

3.2 存儲器選型

選擇存儲器應從以下方面考慮:首先圖像壓縮算法中間數據量大,要求處理器的片上內存盡可能大,盡量避免對外部存儲器讀寫操作。VC5509A的片上存儲器包括32 Kx16位DARAM,96 Kx16位SARAM,共128 K位的存儲空間。其中DARAM為雙地址,在每個周期內可以對其進行兩次操作(2次讀,兩次寫,一次讀和一次寫),這樣大大增加片上存儲器的利用率;其次,VC5509A片上資源豐富,包括I2C總線(多主從接口),3個McBSPs(1個與多媒體卡/數字加密卡MMC/SD串行接口復用引腳)。利用 FC總線對SAA7111的片內控制寄存器進行讀寫操作,非常方便實時控制SAA711 1的工作狀態;利用McBSP配合DMA,軟件編程實現UART功能,無需專門的硬件UART,從而節省電路板空間:VC5509A采用144引腳 LQFP封裝,便于安裝、調試;VC5509A功耗小,工作在200 MHz主頻下,功耗僅100 mW,非常適合嵌入式應用。

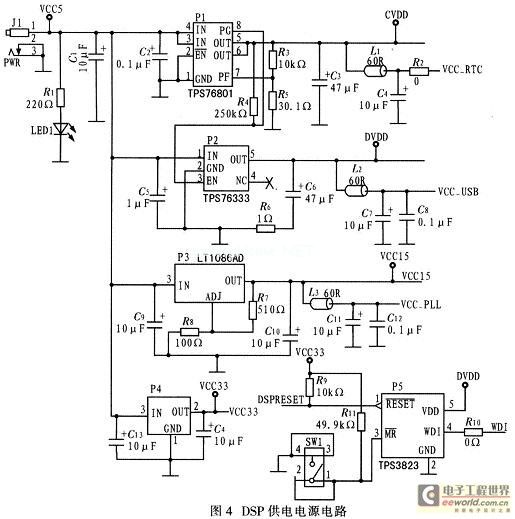

DSP基本系統由獨立的電源系統供電,而硬件平臺的其他器件共用另一套電源供電系統。為了降低系統功耗,DSP一般采用低電壓供電.并且采用I/O和 CPU內核分開供電方式。VC5509A不同的工作頻率要求不同的核電壓,200 MHz為1.6 V,144 MHz為1.35 V,108 MHz為1.2 V。DSP的I/O電壓為3.3 V。

DSP供電電源電路如圖4所示。選用TI公司的兩款LDO電源器件TPS76801和TPS75833分別為DSP提供內核電壓和I/O電壓。

TPS76801能給CPU內核提供最大1 A的電流,電壓在1.2~3 V范圍內可調。

調整TPS76801的輸入電阻值得到1.6 V,1.35 V,1.2 V的核電壓,DSP相應工作在200 MHz,144 MHz,108 MHz的頻率下。而TPS75833能提供最高3 A的I/O電流,對于低功耗的TMS320VC5509A,這已足夠保證其工作在最大負荷狀態。

4 系統軟件設計

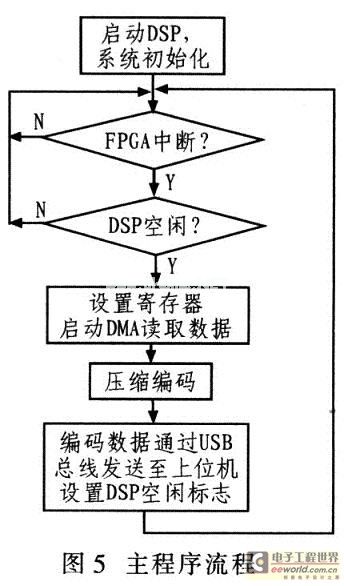

該系統軟件設計的主要功能是實時采樣現場的視頻信號,然后對網像數據編碼壓縮并通過USB總線或RS232串口將圖像數據傳送給主機。系統主程序流程如圖5所示,該系統軟件設計可分為系統初始化、圖像采集、壓縮編碼和數據傳輸4個主要模塊。

系統上電后,DSP首先初始化,初始化主要包括:通過I2C總線初始化SAA7111,設置其工作模式;空間分配,EMIF的配置以保證外部存儲器的正常訪問;配置USB模塊;設定DMA通道以及設定外部中斷。然后DSP等待FPGA的中斷。當DSP接收到FPGA的中斷后,DSP設定標志寄存器,啟動 DMA讀取數據,并進行編碼。當編碼結束后,DSP把數據交付USB模塊,通過USB總線傳送至上位機,同時DSP向FPGA發送空閑信號,通知FPGA 繼續發送下一幀。

5 JPEG優化

JPEG算法在DSP上實現需要解決編碼速度問題。片上內存資源的有限性使得大部分的程序代碼和數據不得不放在片外,大量的圖像數據在慢速的SDRAM存儲器中,對其訪問和算術運算是影響系統性能的關鍵因素之一。因此,應從內存分配和代碼優化兩個方面來優化程序,提高編碼效率。

5.1 數據內存優化

由于VC5509A的片上存儲器包括32 Kx16位DARAM,96 Kx16位SARAM,共128 K位的存儲空間。其中DARAM為雙訪問內存,即在一個周期內可完成兩次數據訪問,SARAM為單訪問內存,即在一個周期內只能完成一次數據訪問,片外內存為擴展的SDRAM,訪問其需要額外的等待時間,執行效率比較低。因此在算法設計中應合理安排內存分配,盡量將訪問頻繁的程序代碼和數據放在片內內存中,特別是DARAM中,可以提高編碼效率。

5.2 C代碼優化

在JPEG的編碼中,根據VC5509A結構特點及結合圖像數據量大的特點,提高編碼效率,考慮程序編寫和優化如下:

(1)利用編譯器優化,開啟編譯器的優化選項,包括基本優化、文件級優化和程序級優化。

(2)使用本征(intrinsics)函數,C55x提供了一種特殊函數一本征函數,可迅速優化C代碼。本征甬數前有個下劃線“一”,調用方法和普通函數相同。

(3)使用圖像庫,TI提供基于C55x的圖像庫IMGLIB,庫中都是圖像處理常用的函數,而且可以用C語言調用,匯編優化好,執行效率高,因此盡量用庫函數。在JPEG編碼中比較關鍵的是DCT變換可調用庫函數中的IMG_sw_fdct_8x8(short*fdct_data,short, *inter_buffer),該函數完成一次DCT變換需用1 078個時鐘周期。大大提高JPEG的編碼效率。

(4)高效使用MAC硬件,C55x有專門的硬件高效執行MAC運算。一個周期中可以執行一個單乘加或一個雙乘加(dual-MAC)運算。

(5)使用特殊數據類型(register類型、volatile類型、const類型),對于需要多次重復訪問的變量,如for循環中的變量值,一般可設置為register型變量。聲明變量為register型能提高效率,但必須小心使用。在某些編譯器中,優化器會自動分配一些變量為register 型。

(6)減少判斷循環,在使用判斷方式選取控制語句時應盡量減少判斷轉移。DSP多采用流水線結構。由于TMS320C55X采用7級流水線結構,頻繁的轉移指令使得流水線難以發揮作用。

另外。DSP的大多數指令為單周期指令,但轉移類指令卻通常要耗費較多的機器周期。因此,應盡可能減少程序中的轉移分支,以提高程序的效率。

6 實驗結果

6.1 壓縮效果實驗結果

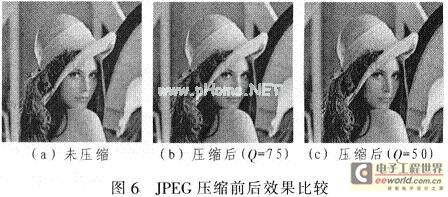

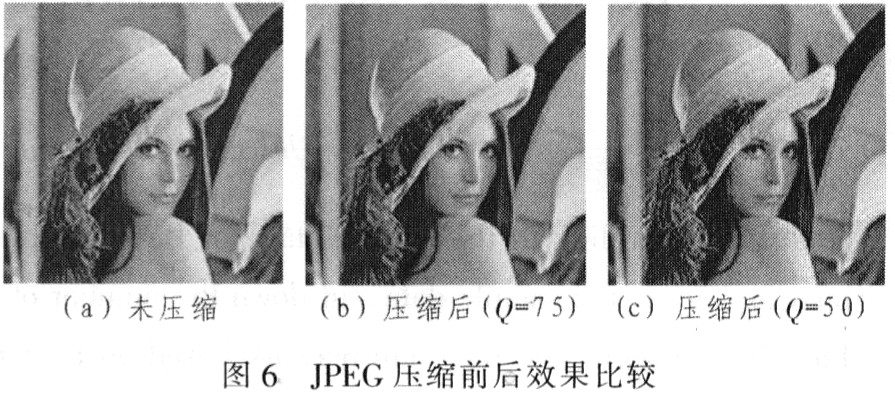

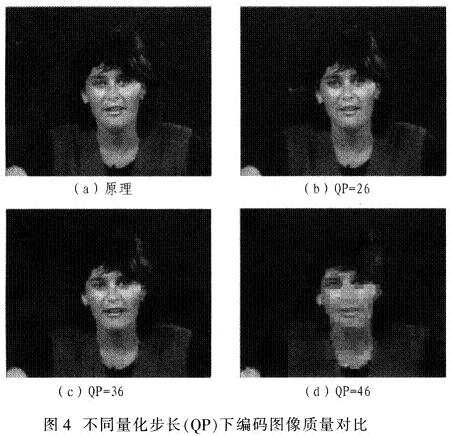

通過改變量化因子Q,改變圖像的壓縮比。壓縮比越大,壓縮過程中的視覺損失越大,壓縮后的圖片越不清晰。圖6為采用不同的量化因子Q的壓縮前后效果比較圖。其中,圖6a為未壓縮,大小57.4 KB的原始BMP圖像,圖6b為壓縮后大小為5.18 KB的圖像,圖6c為壓縮后大小5.18 KB的圖像。由圖知,壓縮后的圖像與原始圖像在視覺效果上相差不大。當Q=50時,壓縮后圖像所需存儲空間僅為原圖像的1/14。

6.2 壓縮耗時實驗結果

對于一個8x8數據塊,各步耗時如下:分塊:1.335μs;DCT變換:5. 39μs;量化:1.355μs;哈夫曼編碼:3.375μs。說明一個8x8數據塊總耗時為11.455μs,一幀720x576灰度圖像的壓縮總耗時為90x72x11.455=74 228.4μs,再加上其他輔助操作,實際耗時約75 ms。根據上述結果,在1 s內向上位機發送13幀720x576的灰度圖像,基本滿足系統要求。

7 結束語

介紹基于TMS320VC5509A DSP的JPEG視頻壓縮系統的設計和實現方案,該系統硬件設計采用DSP+FPGA的方案,充分發揮了各自優勢;而軟件設計針對C55x的結構進行程序結構和算法優化,經過驗證達到較好的實時效果。由于該系統體積小、功耗低,適用于一些野外圖像采集、遠程視頻監控等需要連續傳輸圖像的場合。

電子發燒友App

電子發燒友App

評論