根據FPGA的∑-Δ D/A轉換器的設計與實現策略

摘要:數模轉換器可以將一個二進制數字量轉換成與該數字量成正比的電壓值,可應用于可編程電壓源、波形發生器等。本文采用數字化技術,用FPGA實現了一個簡單的一階8位∑-Δ 型DAC,只占用幾個CLB。FPGA的速度和柔性的輸出結構非常適合該DAC的實現。引言

在各類電子系統中,數字電路所占比重越來越大。這主要是因為數字電路相對于 電路有一些突出的優點,例如:1 數字電路中的有源器件工作在飽和區 與截止區,工作狀態穩定;2 數字電路處理的是二值信號,易于存儲和再生;3 數字電路是由大量相同的基本單元,如門、觸發器等所組成,易于大規模集成,易于自動化設計工具的應用等。再加上數字計算機和數字信號處理技術的迅速發展,使得數字電路從集成規模、應用范圍及設計自動化程度等方面都大大超過了

1? 變∑-Δ換的原理

∑-Δ變換采用過取樣技術,將信號按時間分割,保持幅度恒定,具有高取樣率、噪聲整形和比特字長短的特點。變換可以在低取樣率、高分辨率的量化器或者高取樣率、低分辨率的量化器中進行,在數字音頻中很有用,如用于音頻信號數字化的∑-Δ

打個比方來說明如何用1比特替代16或更多比特:傳統的階梯變換器像16個電燈泡,連接到各自的開關上,每個都有不同的亮度,用各種組合方式可以得到216(即65536)種不同的亮度。然而,燈泡間的亮度差會引入誤差,某種組合也并不總是能夠產生所要求的亮度。1比特變換技術采用完全不同的方法,不用那么多燈泡和開關,只用一個燈泡和一個開關。房間亮度的變化可以通過簡單的改變開、關燈泡的次數來得到。如果燈泡開的次數增加,房間的亮度就會增加。

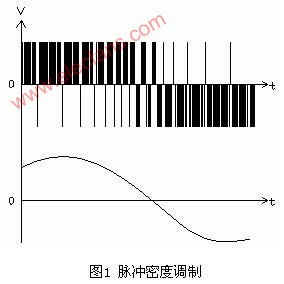

∑-Δ變換是將信號按時間分割,保持信號幅度恒定。它用高電平或低電平的脈沖表示信號,例如可以采用脈沖密度調制(PDM),如圖1所示恒定幅度的脈沖信號,不論電平高或低都能夠重建輸出信號波形。

?

?

2? ∑-Δ DAC的結構

傳統的應用電流模技術的DAC當位數達到10位以上時,要在某一溫度范圍保持精度非常困難。本文的∑-Δ DAC運用了數字技術,因此與電流模DAC相比,不受溫度變化的影響,且能在可編程邏輯器件如FPGA中實現。∑-Δ DAC實際上是高速1位DAC,應用數字反饋技術從輸入二進制數字量產生等幅的脈沖串,脈沖串的平均占空比與輸入二進制數字量成正比,脈沖串再通過一RC模擬低通濾波器就能重建模擬波形。∑-Δ DAC非常適合于低頻、高精度的應用,尤其在數字音頻領域應用廣泛。

作為例子,本文中所描述的∑-Δ DAC的二進制8位輸入數字量是無符號數,模擬輸出電壓值都是正值。輸入“00000000”產生輸出電壓0V,“11111111”產生輸出電壓的最大值Vmax,Vmax非常接近VCCO,其中VCCO是FPGA芯片I/O端口的供電電壓。??????????

????

????

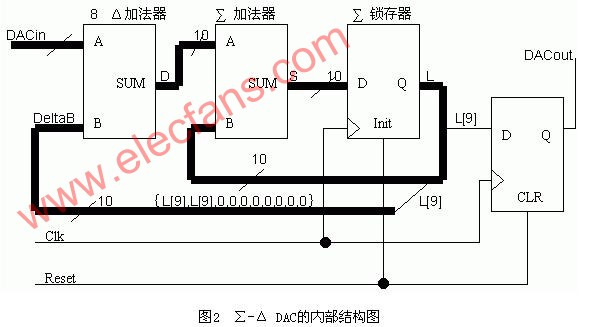

?????? 術語“∑-Δ”分別代表算術和與差,都可用二進制加法器來產生。雖然Δ加法器的輸入是無符號數,但Δ和∑兩加法器的輸出被看作有符號數。Δ加法器用來計算DAC輸入與當前DAC輸出之間的差值。由于DAC的輸出只有一位,非0即1,即全0或全1。如圖2 ∑-Δ DAC的結構圖所示,Δ加法器的另一個輸入值由∑鎖存器最高位L[9]的兩個拷貝后面跟8個0產生,這也彌補了DAC輸入值是無符號數的問題。∑加法器將它的上一次輸出(已經保存在∑鎖存器)與Δ加法器的當前輸出求和。

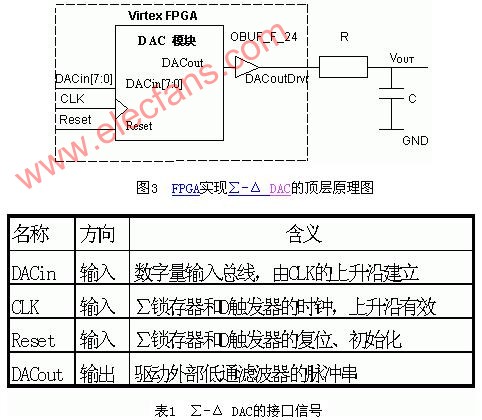

3?∑-Δ DAC的FPGA實現

如圖2所示,∑-Δ DAC的內部僅由2個10位的二進制加法器,1個10位的鎖存器和一個D觸發器組成,用FPGA實現時只需耗費極少的邏輯資源,即使用最小的FPGA也能實現,本文采用了Xilinx Virtex FPGA,圖3給出了FPGA實現的頂層原理圖。輸入信號有8位寬的二進制數字量DACin[7:0]、時鐘信號CLK和復位信號Reset;輸出信號為等幅脈沖串DACout,通過一個驅動緩沖器OBUF_F_24(是Xilinx FPGA特有的SelectI/O資源,OBUF表示輸出緩沖器,F表示它的轉換速率快,24表示它的驅動能力即輸出驅動電流是24MA,基于LVTTL I/O標準)驅動FPGA外部的模擬RC低通濾波器,該緩沖器的輸出端連接到FPGA的I/O端口,則它的驅動電壓即為FPGA的I/O端口的供電電壓VCCO。表1列出了∑-Δ DAC的接口信號。

圖3虛線框內的電路都在FPGA里面實現,其中的DAC模塊的原理圖見圖2,在本文中是用可以綜合的VerilogHDL語句來描述的。VerilogHDL描述的可綜合性是指其可被綜合工具所識別,將其寄存器傳輸級(RTL)描述綜合成門級網表,最終能通過FPGA的布局布線工具映射到FPGA當中成為能完成指定功能的硬件電路。VerilogHDL語言最初是面向建模和仿真的,只有10%可以被綜合稱為可綜合子集。對于不同的綜合工具,可綜合子集的內容并不相同。IEEE的一個工作組目前正在撰寫一個名為IEEE Std 1364.1RTL的綜合子集的規范,定義了一個最小的可綜合的Verilog語言要素的子集,以便得到各綜合工具提供商的支持。

圖3中緩沖器的輸出端DACoutDrvr連接到FPGA的輸出引腳上,驅動外部的

‘timescale 100 ps / 10 ps

//This is a Delta-Sigma Digital to Analog Converter

module dac(DACout, DACin, Clk, Reset);

output DACout; // This is the average output that feeds low pass filter

reg DACout;

input [7:0] DACin; // DAC input

input Clk;

input Reset;

reg [9:0] DeltaAdder; // Output of Delta adder

reg [9:0] SigmaAdder; // Output of Sigma adder

reg [9:0] SigmaLatch; // Latches output of Sigma adder

reg [9:0] DeltaB; // B input of Delta adder

always @(SigmaLatch) DeltaB = {SigmaLatch[9],SigmaLatch[9]} << (8);

always @(DACin or DeltaB) DeltaAdder = DACin + DeltaB;

always @(DeltaAdder or SigmaLatch) SigmaAdder = DeltaAdder + SigmaLatch;

always @(posedge Clk or posedge Reset)

begin

if(Reset)

begin

SigmaLatch <= #1 1’bl << (8);

DACout <= #1 1’b0;

end

else

begin

SigmaLatch <= #1 SigmaAdder;

DACout <= #1 SigmaLatch[9];

end

end

endmodule該程序經過Xilinx的FPGA集成開發工具ISE6.2編譯(含綜合過程)、仿真后,再選擇Virtex系列FPGA芯片進行配置。設置CLK=100MHz(最高可達219MHz)。

4 結論

∑-Δ DAC是高速FPGA芯片用于數字模擬混合信號系統設計的嘗試,可應用于可編程電壓源、波形發生器、聲音發生器、RGB顏色發生器和

電子發燒友App

電子發燒友App

評論