未來中國通信行業(yè)將會形成怎樣的格局與態(tài)勢?這不僅和4G有關(guān),與寬帶中國戰(zhàn)略有關(guān),與集約化網(wǎng)業(yè)分離以及三網(wǎng)融合有關(guān),更與十八屆三中全會相關(guān)的政策有關(guān)。

2014-03-10 09:19:34 2207

2207 在不溫不火的一年多推動發(fā)展后,iBeacon借助微信的搖一搖周邊終于在各大媒體火爆起來。作為iBeacon圈資深從業(yè)者,筆者對這一事件非常關(guān)注,和業(yè)內(nèi)同行和合作伙伴聊起,大家有的看好,有的觀望,一時間大家都在猜測最終iBeacon會形成怎樣的局面?

2015-03-24 10:05:22 1698

1698 物聯(lián)網(wǎng)產(chǎn)業(yè)日益壯大,2015年我國物聯(lián)網(wǎng)市場規(guī)模將突破7500億元,未來5年內(nèi),市場規(guī)模更是有望突破萬億元大關(guān)。那么,作為現(xiàn)在核心技術(shù)的物聯(lián)網(wǎng)主流連接方式藍牙、Wifi、ZigBee,會形成怎樣的競爭抑或合作格局呢?

2016-04-22 14:34:39 1737

1737 ,由于干擾源的不確定性,串擾噪聲一般會同時影響信號的邊沿和幅度。因此,對于串擾來說兩個方面的影響都應(yīng)該考慮。串擾形成的根源在于耦合。在多導體系統(tǒng)中,導體間通過電場和磁場發(fā)生耦合。這種耦合會把信號的一部分

2018-12-24 11:56:24

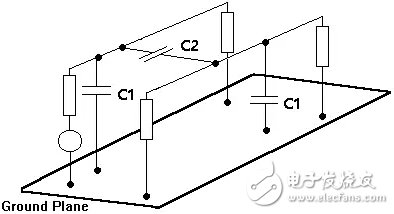

,由于干擾源的不確定性,串擾噪聲一般會同時影響信號的邊沿和幅度。因此,對于串擾來說兩個方面的影響都應(yīng)該考慮。串擾形成的根源在于耦合。在多導體系統(tǒng)中,導體間通過電場和磁場發(fā)生耦合。這種耦合會把信號的一部分能量傳遞到鄰近的導體上,從而形成噪聲。耦合的方式主要有兩種:1、容性耦合。2、感性耦合。

2019-05-31 06:03:14

繼上一篇“差模(常模)噪聲與共模噪聲”之后,本文將對“串擾”進行介紹。串擾串擾是由于線路之間的耦合引發(fā)的信號和噪聲等的傳播,也稱為“串音干擾”。特別是“串音”在模擬通訊時代是字如其意、一目了然的表達

2018-11-29 14:29:12

串擾的基本原理

2021-03-18 06:26:37

所謂串擾,是指有害信號從一個傳輸線耦合到毗鄰傳輸線的現(xiàn)象,噪聲源(攻擊信號)所在的信號網(wǎng)絡(luò)稱為動態(tài)線,***擾的信號網(wǎng)絡(luò)稱為靜態(tài)線。串擾產(chǎn)生的過程,從電路的角度分析,是由相鄰傳輸線之間的電場(容性)耦合和磁場(感性)耦合引起,需要注意的是串擾不僅僅存在于信號路徑,還與返回路徑密切相關(guān)。

2019-08-02 08:28:35

在選擇模數(shù)轉(zhuǎn)換器時,是否應(yīng)該考慮串擾問題?ADI高級系統(tǒng)應(yīng)用工程師Rob Reeder:“當然,這是必須考慮的”。串擾可能來自幾種途徑從印刷電路板(PCB)的一條信號鏈到另一條信號鏈,從IC中的一個

2019-02-28 13:32:18

怎樣學習51串口,掌握了一些基本知識,卻不知道從何下手,不知道怎樣一步一步的去學習它

2014-05-29 20:48:07

是ADI的SAR型 18位單通道全差分輸入的ADC。ADC的后端是MCU,MCU將數(shù)字信號處理之后再畫到顯示屏上顯示實時波形。

調(diào)試發(fā)現(xiàn)顯示的信號有串擾,表現(xiàn)為某一路信號懸空之后,相鄰的那一路信號

2023-12-18 08:27:39

是ADI的SAR型 18位單通道全差分輸入的ADC。ADC的后端是MCU,MCU將數(shù)字信號處理之后再畫到顯示屏上顯示實時波形。 調(diào)試發(fā)現(xiàn)顯示的信號有串擾,表現(xiàn)為某一路信號懸空之后,相鄰的那一路信號上

2018-09-06 14:32:00

限度的拉開,同時為了保證疊層厚度不變,就需要把信號和參考的地平面相應(yīng)的靠近。這個操作的好處是顯而易見,信號與信號之間的距離變遠的同時,信號與參考地平面的距離又變近了,串擾肯定就能夠改善了啊!下面是雷豹想到

2023-06-06 17:24:55

串擾是由于線路之間的耦合引發(fā)的信號和噪聲等的傳播,也稱為“串音干擾”。特別是“串音”在模擬通訊時代是字如其意、一目了然的表達。兩根線(也包括PCB的薄膜布線)獨立的情況下,相互間應(yīng)該不會有電氣信號

2019-08-08 06:21:47

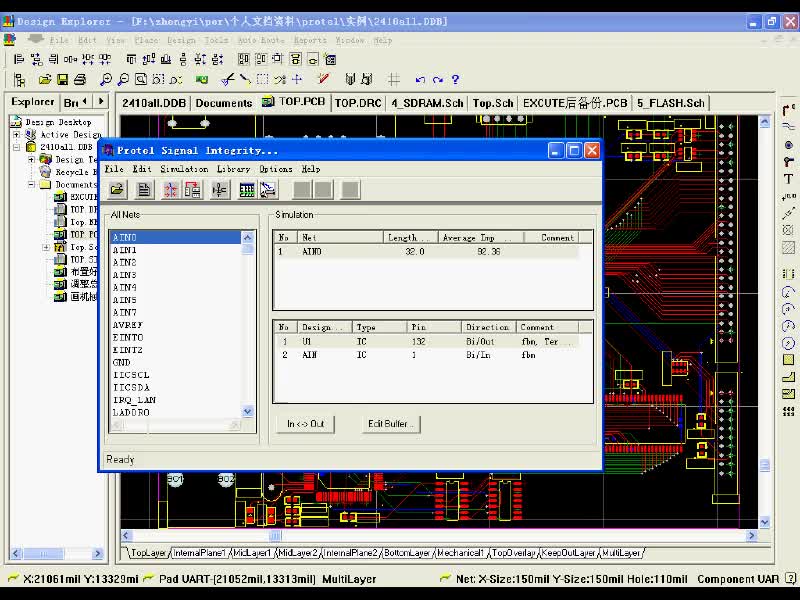

PCB板上的高速信號需要進行仿真串擾嗎?

2023-04-07 17:33:31

42.3 近端串擾與遠端串擾由靜態(tài)線耦合到動態(tài)線上的串擾分成兩部分,一部分往與信號方向相同,傳至接收端方向,我們把它叫做遠端串擾或者前向串擾。另一部分與信號方向相反,傳至發(fā)送端方向,我們把它叫做近端串

2014-10-21 09:53:31

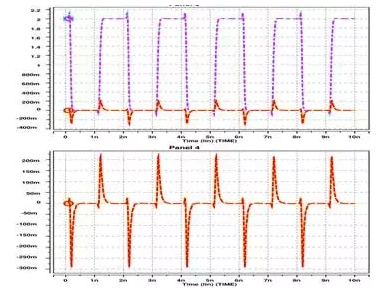

作者:一博科技SI工程師陳德恒3. 仿真實例在ADS軟件中構(gòu)建如下電路: 圖2圖2為微帶線的近端串擾仿真圖,經(jīng)過Allegro中的Transmission line Calculators軟件對其疊

2014-10-21 09:52:58

PCB設(shè)計中如何處理串擾問題 變化的信號(例如階躍信號)沿

2009-03-20 14:04:47

變化的信號(例如階躍信號)沿傳輸線由A到B傳播,傳輸線C-D上會產(chǎn)生耦合信號,變化的信號一旦結(jié)束也就是信號恢復到穩(wěn)定的直流電平時,耦合信號也就不存在了,因此串擾僅發(fā)生在信號跳變的過程當中,并且

2018-08-29 10:28:17

變化的信號(例如階躍信號)沿傳輸線由A到B傳播,傳輸線C-D上會產(chǎn)生耦合信號,變化的信號一旦結(jié)束也就是信號恢復到穩(wěn)定的直流電平時,耦合信號也就不存在了,因此串擾僅發(fā)生在信號跳變的過程當中,并且信號

2020-06-13 11:59:57

是怎么形成的。如下圖所示,當有信號傳輸?shù)淖呔€和相鄰走之間間距較近時,有信號傳輸?shù)淖呔€會在相鄰走線上引起噪聲,這種現(xiàn)象稱為串擾。串擾形成的根本原因在于相鄰走線之間存在耦合,如下圖所示:當信號在一走線上

2023-01-10 14:13:01

本文解釋了音頻串擾的產(chǎn)生原因,當兩個揚聲器相隔距離過近時,原本應(yīng)傳輸至一只耳朵的音頻信號會進入另一只耳朵。文中闡述了如何通過相位延遲實現(xiàn)3D音效,使聽者兩耳處產(chǎn)生與標準視聽條件相同的信號,并以MAX9775耳機放大器為例進行了說明。引言

2019-08-12 04:30:00

串擾串擾的途徑:容性耦合和感性耦合。串擾發(fā)生在兩種不同情況:互連性為均勻傳輸線(電路板上大多數(shù)線)非均勻線(接插件和封裝)近端遠端串擾各不同。返回路徑是均勻平面時是實現(xiàn)最低串擾的結(jié)構(gòu)。通常發(fā)生這種

2017-11-27 09:02:56

噪聲一般會同時影響信號的邊沿和幅度。因此,對于串擾來說兩個方面的影響都應(yīng)該考慮。串擾形成的根源在于耦合。在多導體系統(tǒng)中,導體間通過電場和磁場發(fā)生耦合。這種耦合會把信號的一部分能量傳遞到鄰近的導體上,從而形成噪聲。耦合的方式主要有兩種:1、容性耦合。2、感性耦合。

2019-04-18 09:30:40

為什么CC1101信道出現(xiàn)串擾現(xiàn)象?各位大神,我在使用CC1101的時候,遇到如下問題,我購買的是模塊,并非自己設(shè)計,所有參數(shù),使用smart rf生成,參數(shù)如下:base frequency

2016-03-11 10:01:10

多了,這樣我想有個問題就是,在正常采集時,這幾個通道間會不會有互相串擾的問題。謝謝。

另外我想知道互相串擾產(chǎn)生原因,如果能成放大器內(nèi)部解釋更好

2023-11-21 08:15:40

繼上一篇“差模(常模)噪聲與共模噪聲”之后,本文將對“串擾”進行介紹。串擾串擾是由于線路之間的耦合引發(fā)的信號和噪聲等的傳播,也稱為“串音干擾”。特別是“串音”在模擬通訊時代是字如其意、一目了然的表達

2019-03-21 06:20:15

串擾的概念是什么?到底什么是串擾?

2021-03-05 07:54:17

什么是串擾?互感和互容電感和電容矩陣串擾引起的噪聲

2021-02-05 07:18:27

航空通信系統(tǒng)變得日益復雜,我們通常需要在同一架飛機上安裝多條天線,這樣可能會在天線間造成串擾,或稱同址干擾,影響飛機運行。在本教程模型中,我們利用COMSOL Multiphysics 5.1 版本模擬了飛機機身上兩個完全相同的天線之間的干擾,其中一個負責發(fā)射,另一個負責接收,以此來分析串擾的影響。

2019-08-26 06:36:54

一、引言隨著電路設(shè)計高速高密的發(fā)展趨勢,QFN封裝已經(jīng)有0.5mm pitch甚至更小pitch的應(yīng)用。由小間距QFN封裝的器件引入的PCB走線扇出區(qū)域的串擾問題也隨著傳輸速率的升高而越來越突出

2019-07-30 08:03:48

我用AD9910做了塊板子,使用AD9910內(nèi)部的PLL,參考時鐘為10MHz,64倍頻,輸出80MHz,發(fā)現(xiàn)在70MHz和90MHz處有串擾信號,幅值與80MHz差65dB。懷疑是AD9910

2018-11-19 09:46:32

領(lǐng)域的工程師離不開它,近些年來,高速信號完整性領(lǐng)域也越來越多的工程師喜歡上了這款“不要不要”的軟件。鑒于國內(nèi)外的很多ADS的資料都是微波射頻領(lǐng)域的,接下來,我們會慢慢的分享一些ADS在信號完整性領(lǐng)域經(jīng)常使用的小功能和技巧。今天給大家介紹使用ADS進行串擾的仿真。

2019-06-28 08:09:46

串擾信號產(chǎn)生的機理是什么串擾的幾個重要特性分析線間距P與兩線平行長度L對串擾大小的影響如何將串擾控制在可以容忍的范圍

2021-04-27 06:07:54

一博科技自媒體高速先生原創(chuàng)文 | 黃剛讓你評估高速串行信號的串擾,你會說它們的串擾在-40db以下,沒什么影響。但是如果讓你評估像DDR這種并行信號的串擾,你說DQ0和DQ1的串擾-30db,DQ1

2019-09-05 11:01:14

面對串擾,包地是萬能的嗎?請看不一樣的解答

2016-12-30 16:29:07

在t=TD時刻,而且它的持續(xù)時間基本上就等于信號的上升時間或下降時間。 圖4信號上升沿產(chǎn)生的遠端/近端串擾信號示意圖干擾源傳輸線驅(qū)動信號從低到高的變化過程中,在鄰近傳輸線上產(chǎn)生的近端干擾與遠端干擾上面圖

2016-10-10 18:00:41

在設(shè)計fpga的pcb時可以減少串擾的方法有哪些呢?求大神指教

2023-04-11 17:27:02

問題:選擇模數(shù)轉(zhuǎn)換器時是否應(yīng)考慮串擾問題?答案:當然!串擾可能來自幾種途徑:從印刷電路板(PCB)的一條信號鏈到另一條信號鏈,從IC中的一個通道到另一個通道,或者是通過電源時產(chǎn)生。理解串擾的關(guān)鍵在于

2018-10-26 10:53:12

如果您給某個傳輸線的一端輸入信號,該信號的一部分會出現(xiàn)在相鄰傳輸線上,即使它們之間沒有任何連接。信號通過周邊電磁場相互耦合會產(chǎn)生噪聲,這就是串擾的來源,它將引起數(shù)字系統(tǒng)的誤碼。一旦這種噪聲在相鄰

2019-07-08 08:19:27

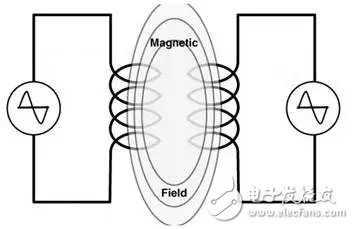

稱為遠端串擾(也稱前向串擾)。串擾主要源自兩相鄰導體之間所形成的互感Lm和互容Cm。 2.1感性耦合 在圖1中,先只考慮互感Lm引起的感性耦合。線路A到B上傳輸?shù)男盘柕拇艌鲈诰€路C到D上感應(yīng)出電壓

2018-09-11 15:07:52

靜態(tài)存儲器SRAM是一款不需要刷新電路即能保存它內(nèi)部存儲數(shù)據(jù)的存儲器。在SRAM 存儲陣列的設(shè)計中,經(jīng)常會出現(xiàn)串擾問題發(fā)生。那么要如何減小如何減小SRAM讀寫操作時的串擾,以及提高SRAM的可靠性呢

2020-05-20 15:24:34

解答: 一般acdc電源模塊輸入串聯(lián)供電時,都會存在串擾情況,特別是并聯(lián)多個電源時,一般采取的方法為輸入和輸出都增加濾波電路,可以在輸入端增加共模電感和X電容,輸出端做π型濾波。

2018-07-17 16:14:18

在嵌入式系統(tǒng)硬件設(shè)計中,串擾是硬件工程師必須面對的問題。特別是在高速數(shù)字電路中,由于信號沿時間短、布線密度大、信號完整性差,串擾的問題也就更為突出。設(shè)計者必須了解串擾產(chǎn)生的原理,并且在設(shè)計時應(yīng)用恰當?shù)姆椒ǎ?b class="flag-6" style="color: red">串擾產(chǎn)生的負面影響降到最小。

2019-11-05 08:07:57

存在串擾時的抖動和定時,你想知道的都在這

2021-05-07 06:56:55

一、引言隨著電路設(shè)計高速高密的發(fā)展趨勢,QFN封裝已經(jīng)有0.5mm pitch甚至更小pitch的應(yīng)用。由小間距QFN封裝的器件引入的PCB走線扇出區(qū)域的串擾問題也隨著傳輸速率的升高而越來越突出

2018-09-11 11:50:13

怎么實現(xiàn)基于AD8108的寬頻帶低串擾視頻切換矩陣的設(shè)計?

2021-06-08 06:18:11

隨著電路設(shè)計高速高密的發(fā)展趨勢,QFN封裝已經(jīng)有0.5mm pitch甚至更小pitch的應(yīng)用。由小間距QFN封裝的器件引入的PCB走線扇出區(qū)域的串擾問題也隨著傳輸速率的升高而越來越突出。對于

2021-03-01 11:45:56

`最近新買了一臺RIGOL的1000Z,在用CH1測試10M正弦波信號時,CH2的信號串擾好大(當時沒有給通道二信號,本應(yīng)是一條直線,可是有一個接近小正弦波的信號!!!!!!!!!!!!!下圖就是

2013-08-14 17:23:14

消除串擾的方法合理的PCB布局-將敏感的模擬部分與易產(chǎn)生干擾的數(shù)字部分盡量隔離,使易產(chǎn)生干擾的數(shù)字信號走線上盡量靠近交流地,使高頻信號獲得較好的回流路徑。盡量減小信號回路的面積,降低地線的阻抗,采用多點接地的方法。使用多層板將電源與地作為獨立的一層來處理。合理的走線拓樸結(jié)構(gòu)-盡量采用菊花輪式走線

2009-06-18 07:52:34

采用合適的線端負載,因為線端負載會影響串擾的大小和串擾隨時間的弱化程度。下面是一個測量實例,它揭示了走線末端與邏輯門電路輸出處的線端負載會怎樣衰減串擾并減弱形成串擾的成因。參考文獻:[1]. PCB datasheet http://www.dzsc.com/datasheet/PCB_1201640.html.:

2018-11-27 10:00:09

最近做了一塊板子,測試的時候發(fā)現(xiàn)臨近的3條線上的信號是一樣的,應(yīng)該是串擾問題,不知道哪位大神能不能給個解決方案!愿意幫忙的,可以回帖然后我把設(shè)計文件發(fā)給你,十分感謝!

2013-04-11 18:11:01

矢量網(wǎng)絡(luò)分析儀串擾如何測試,設(shè)備如何設(shè)置

2023-04-09 17:13:25

示波器通道間串擾的影響 目前幾乎所有通用品牌的主流示波器通道都不是隔離的,那么在進行多通道測試的時候,通道與通道之間會一定程度互相干擾,因此通道隔離度指標非常重要,隔離度越高的示波器測量就越精確

2020-03-23 18:53:35

雙絞線的性能在一直不斷的提高,但有一個參數(shù)一直伴隨著雙絞線,并且伴隨著雙絞線的發(fā)展,這個參數(shù)也越來越重要,它就是串擾 (Crosstalk)。串擾是影響數(shù)據(jù)傳輸最嚴重的因素之一。它是一個信號對另外一個

2018-01-19 11:15:04

在PCB電路設(shè)計中有很多知識技巧,之前我們講過高速PCB如何布局,以及電路板設(shè)計最常用的軟件等問題,本文我們講一下關(guān)于怎么解決PCB設(shè)計中消除串擾的問題,快跟隨小編一起趕緊學習下。 串擾是指在一根

2020-11-02 09:19:31

是SAR型 18位單通道全差分輸入的ADC。ADC的后端是MCU,MCU將數(shù)字信號處理之后再畫到顯示屏上顯示實時波形。 調(diào)試發(fā)現(xiàn)顯示的信號有串擾,表現(xiàn)為某一路信號懸空之后,相鄰的那一路信號上就會出現(xiàn)噪聲。將采樣的時間延長也無法消除串擾。想請教一下各路專家,造成串擾的原因和如何消除串擾,謝謝。

2019-05-14 14:17:00

高頻數(shù)字信號串擾的產(chǎn)生及變化趨勢串擾導致的影響是什么怎么解決高速高密度電路設(shè)計中的串擾問題?

2021-04-27 06:13:27

)。串擾主要源自兩相鄰導體之間所形成的互感Lm和互容Cm。 2.1感性耦合

2009-03-20 13:56:06

?????? 高速PCB設(shè)計的整個過程包括了電路設(shè)計、芯片選擇、原理圖設(shè)計、PCB布局布線等步驟,設(shè)計時需要在不同的步驟里發(fā)現(xiàn)串擾并采取辦法來抑制它,以達到減小干擾的目的。

?????? 串擾

2018-08-28 11:58:32

高速數(shù)字設(shè)計領(lǐng)域里,信號完整性已經(jīng)成了一個關(guān)鍵的問題,給設(shè)計工程師帶來越來越嚴峻的考驗。信號完整性問題主要為反射、串擾、延遲、振鈴和同步開關(guān)噪聲等。本文基于高速電路設(shè)計的信號完整性基本理論,通過近端

2010-05-13 09:10:07

在硬件系統(tǒng)設(shè)計中,通常我們關(guān)注的串擾主要發(fā)生在連接器、芯片封裝和間距比較近的平行走線之間。但在某些設(shè)計中,高速差分過孔之間也會產(chǎn)生較大的串擾,本文對高速差分過孔之間的產(chǎn)生串擾的情況提供了實例仿真分析

2018-09-04 14:48:28

方向的間距時,就要考慮高速信號差分過孔之間的串擾問題。順便提一下,高速PCB設(shè)計的時候應(yīng)該盡可能最小化過孔stub的長度,以減少對信號的影響。如下圖所1示,靠近Bottom層走線這樣Stub會比較短。或者

2020-08-04 10:16:49

串擾問題產(chǎn)生的機理是什么高速數(shù)字系統(tǒng)的串擾問題怎么解決?

2021-04-25 08:56:13

高速電路信號完整性分析與設(shè)計—串擾串擾是由電磁耦合引起的,布線距離過近,導致彼此的電磁場相互影響串擾只發(fā)生在電磁場變換的情況下(信號的上升沿與下降沿)[此貼子已經(jīng)被作者于2009-9-12 10:32:03編輯過]

2009-09-12 10:31:08

高速PCB設(shè)計中的信號完整性概念以及破壞信號完整性的原因高速電路設(shè)計中反射和串擾的形成原因

2021-04-27 06:57:21

pn結(jié)的形成/多晶硅中PN結(jié)是怎樣形成的?

PN結(jié)及其形成過程 在雜質(zhì)半導體中, 正負電荷數(shù)是相等的,它們的作用相互抵消

2010-02-26 11:40:45 5038

5038 在5G時代,AI將參與到傳統(tǒng)通信生態(tài)中,貫穿整個通信生態(tài)系統(tǒng)的業(yè)務(wù)和網(wǎng)絡(luò)領(lǐng)域,幫助提升信息效率和通信性能,從而扮演推進器的角色。

2020-04-17 11:16:45 257

257

電子發(fā)燒友App

電子發(fā)燒友App

評論