本文介紹了時鐘擴頻技術的原理、分類,結合它在攝像頭的具體應用案例,與傳統EMI抑制手段的實際效果進行對比,突顯時鐘擴頻技術在抑制時鐘EMI上的優勢。目前,時鐘擴展頻譜技術被廣泛使用在圖像采集、圖像

2018-05-18 02:13:00 2042

2042

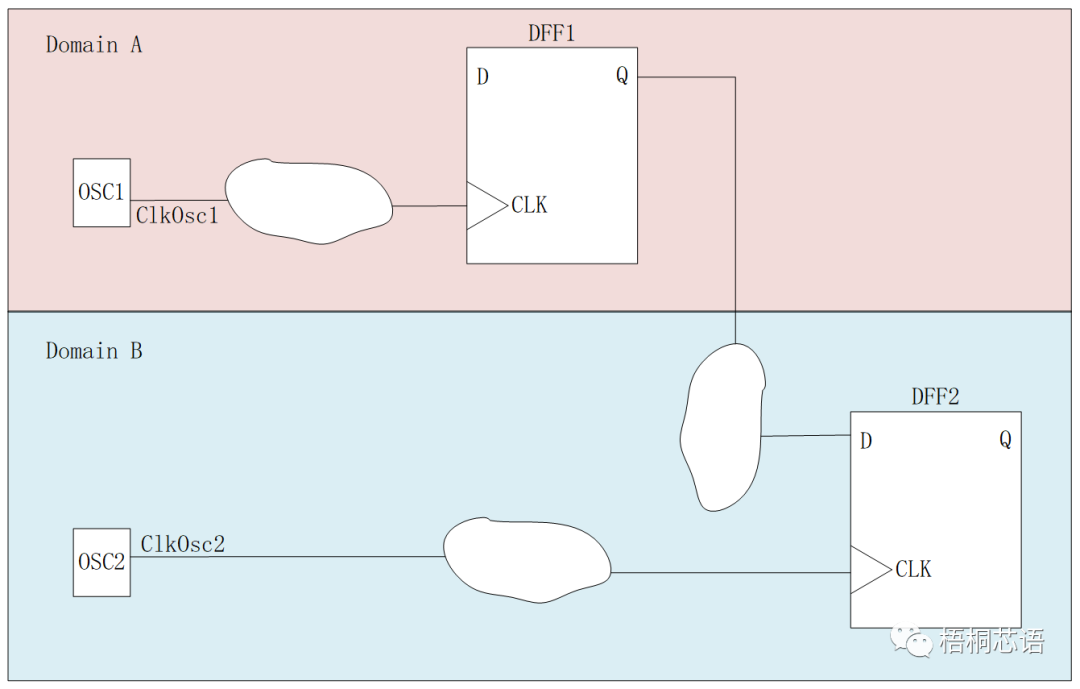

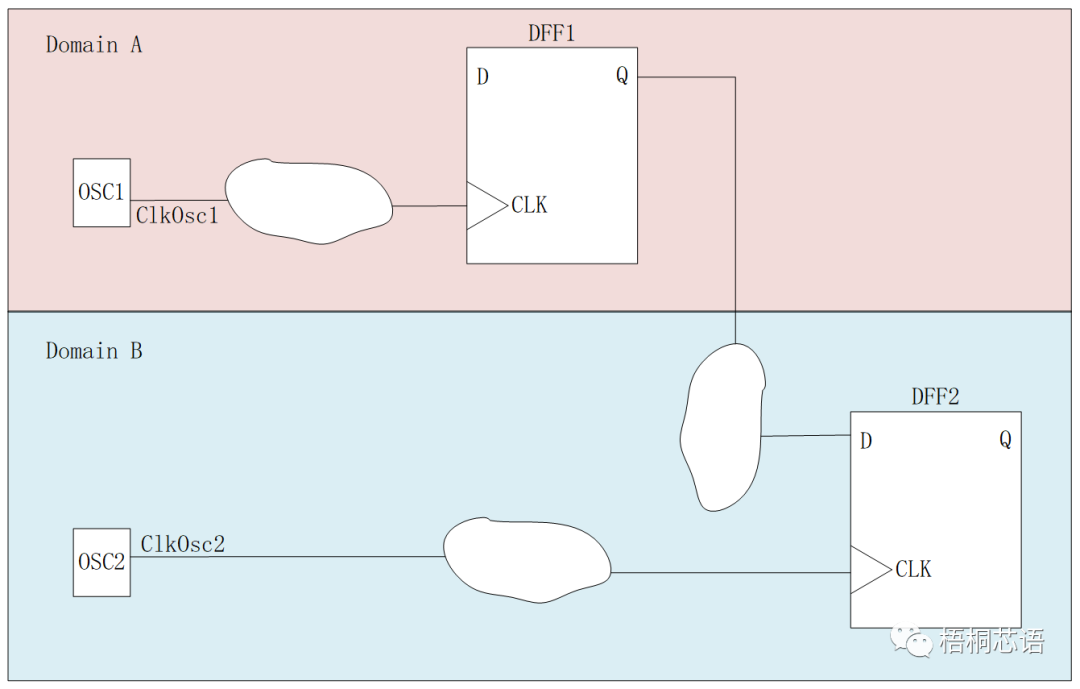

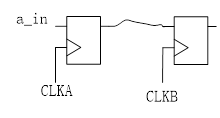

在多時鐘設計中可能需要進行時鐘的切換。由于時鐘之間可能存在相位、頻率等差異,直接切換時鐘可能導致產生glitch。

2020-09-24 11:20:38 5317

5317

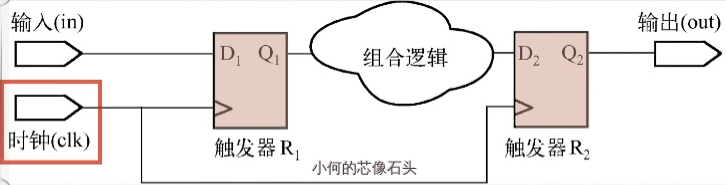

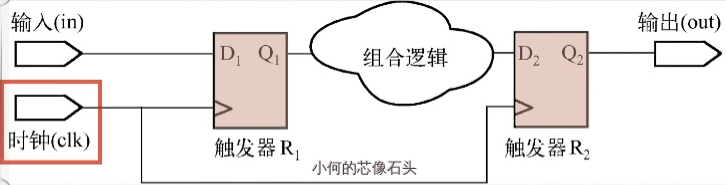

01、如何決定FPGA中需要什么樣的時鐘速率 設計中最快的時鐘將確定 FPGA 必須能處理的時鐘速率。最快時鐘速率由設計中兩個觸發器之間一個信號的傳輸時間 P 來決定,如果 P 大于時鐘周期

2020-11-23 13:08:24 3565

3565

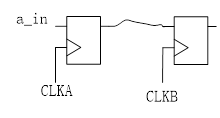

跨時鐘域路徑分析報告分析從一個時鐘域(源時鐘)跨越到另一個時鐘域(目標時鐘)的時序路徑。

2020-11-27 11:11:39 5449

5449

我在知乎看到了多bit信號跨時鐘的問題,于是整理了一下自己對于跨時鐘域信號的處理方法。

2022-10-09 10:44:57 4599

4599 今天我們將討論時鐘如何影響精密 ADC,涉及時鐘抖動、時鐘互調和時鐘的最佳 PCB 布局實踐。

2023-04-11 09:13:22 645

645 在一個復雜的SoC(System on Chip)系統中,不可能只有一個時鐘。我們一般認為,一個時鐘控制的所有寄存器集合處于該時鐘的時鐘域中。

2023-08-01 15:48:20 1052

1052

時鐘抖動技術適合于各種周期性的脈沖信號,典型的是電力電子設備中的PWM電壓和數字電路中的時鐘信號。

2023-09-11 10:55:34 503

503

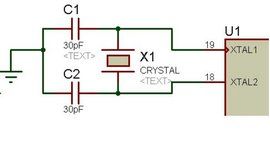

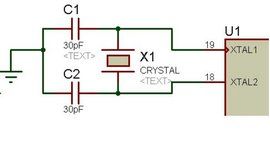

上篇文章我們講了時鐘信號的幾個重要參數,今天我們簡單講一下在設計中最常用到的幾種時鐘信號產生的方法,由于篇幅限制,我們不對具體的原理進行講述,有興趣的朋友可以在網上搜索相應的文章進行深入了解,另外

2019-06-05 04:20:28

PLL不僅被廣泛用在通信系統中產生方便調節的不同頻點的高頻率本振信號(LO),還被廣泛用在處理器、FPGA、通信器件中用于生成器件內部的高速時鐘。USB接口芯片的時鐘產生及內部PLLDDS生成任意頻率

2019-06-06 04:20:03

了這些寄生信號。整合 BB 濾波器可最大限度地消除這些寄生信號。本文將探討這些寄生信號是如何出現在調制器輸出端的。圖 1:OIP3 測量頻譜分析儀截圖在圖 1 所示的頻譜分析儀截圖中,有兩個 RF

2018-09-19 14:43:36

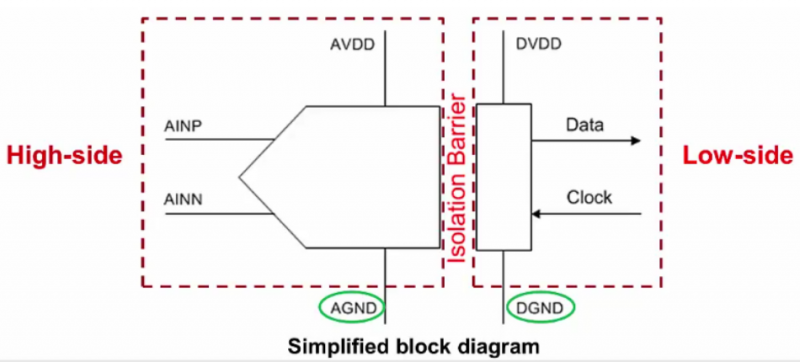

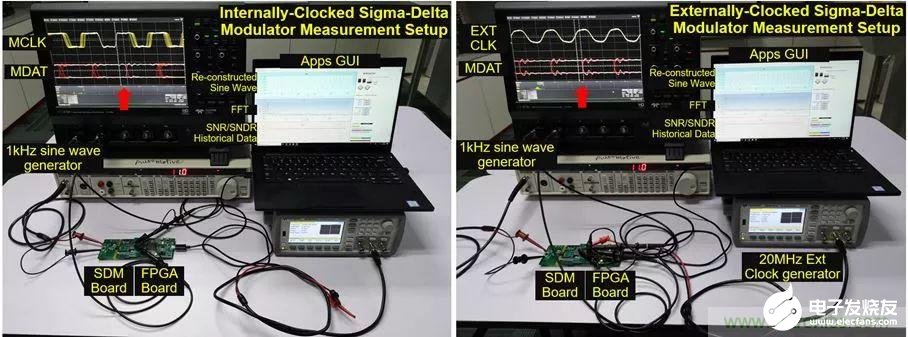

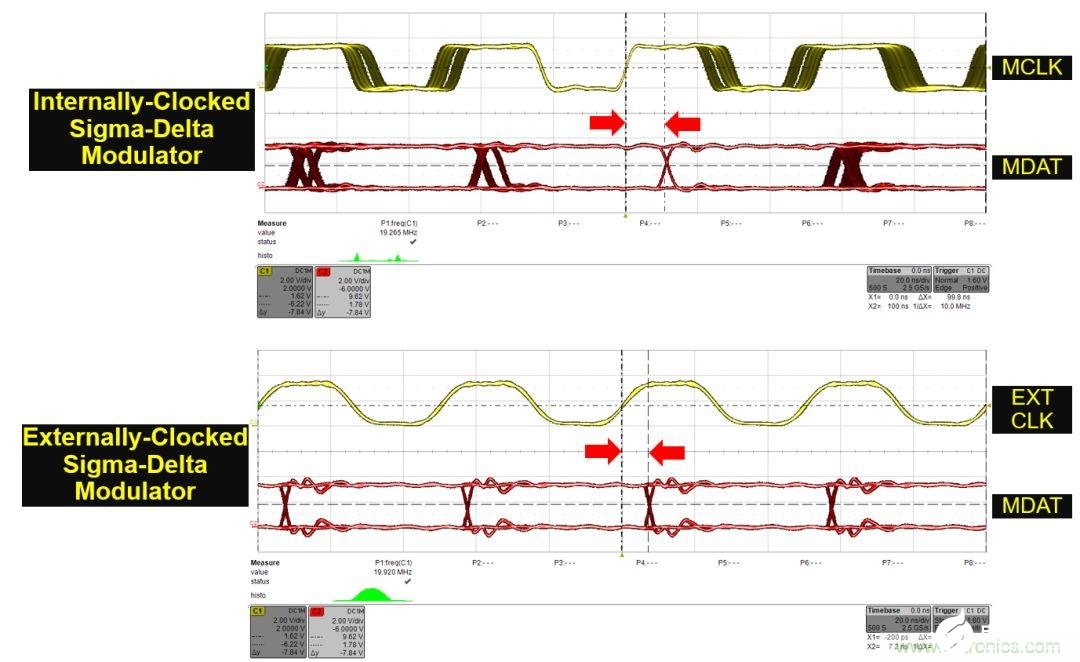

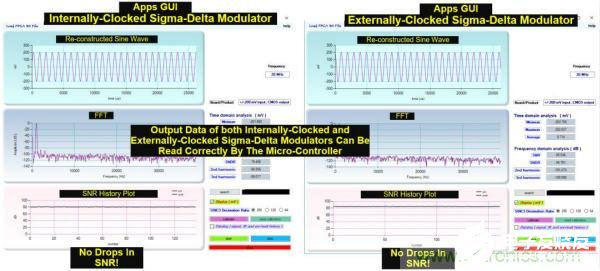

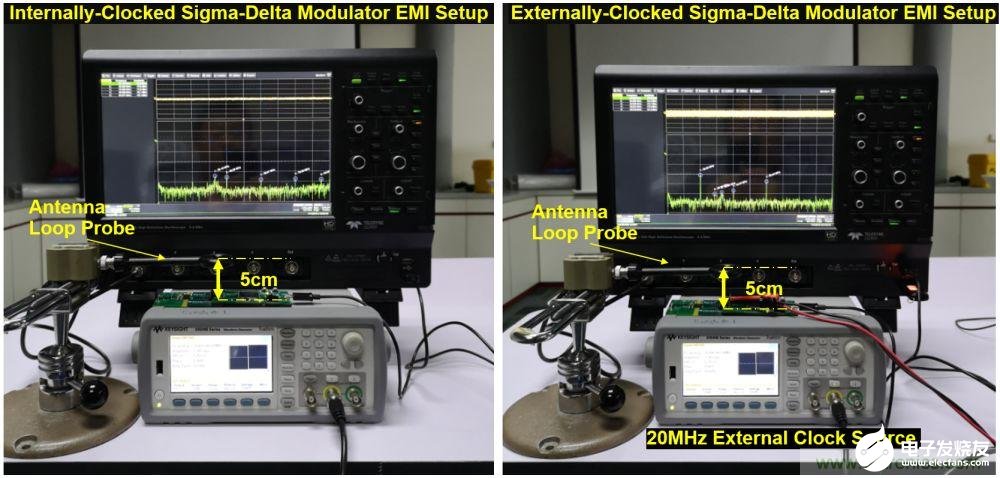

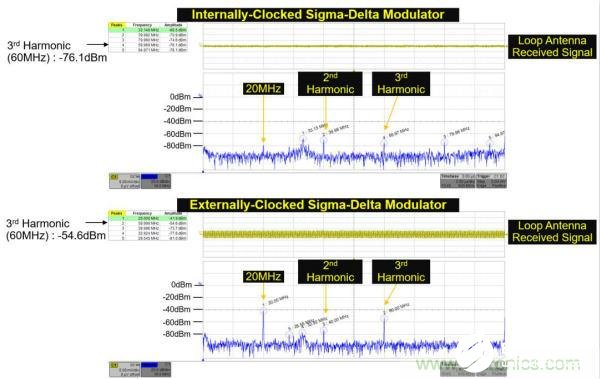

設置,用于測量兩類Σ-Δ調制器的時鐘信號的EMI從圖6中示波器捕獲的圖像可以清楚看出,外時鐘源產生的EMI要高得多,在時鐘信號頻率及其諧波處達到峰值。例如,對于60MHz的三次諧波,外時鐘源產生的EMI比內時鐘Σ-Δ調制器輸出時鐘信號的高20dB。

2020-10-21 16:12:12

速率時鐘或數據將被破壞。(使用瞬態脈沖頻率為100 kHz。)操作理論電路信息AD7400A隔離∑-Δ調制器將模擬輸入信號轉換為高速(10 MHz典型)的單位數據流;調制器的單位數據的時間平均值與輸入

2020-09-25 17:55:01

什么是時鐘脈沖?為什么CPU需要時鐘?CPU的時鐘信號是如何產生的?

2021-10-20 07:21:14

包括有源晶振、無源晶振、時鐘產生器等。MCG 模塊提供九種不同的工作模式,分別是:鎖頻環片內時鐘模式( FEI),鎖頻環片外時鐘模式(FEE),鎖頻環旁路片內時鐘模式(FBI),鎖頻環旁路片外時鐘模式

2015-02-10 15:39:48

MSP430 時鐘系統3個振蕩器 3個時鐘信號時鐘源1低頻時鐘源:外接32768Hz晶振工作在低頻模式ACLK輔助時鐘2 高頻時鐘源:外接8MHz晶振 MCLK主系統時鐘3 數字控制RC振蕩器 產生

2021-11-29 07:22:07

濾波電容,如VTT等。這不僅對穩定性有影響,對EMI也有很大的影響。 2 時鐘線的處理 2.1)建議先走時鐘線。 2.2)頻率大于等于66M的時鐘線,每條過孔數不要超過2個,平均不得超過1.5個

2018-09-11 16:05:40

用時鐘源來產生時鐘!在STM32中,有五個時鐘源,為HSI、HSE、LSI、LSE、PLL。①、HSI是高速內部時鐘,RC振蕩器,頻率為8MHz。②、HSE是高速外部時鐘,可接石英/陶瓷諧振器,或者

2021-08-19 06:49:53

(HSE,HSI,LSE,LSI)產生的過程比430簡單許多,430的幾個時鐘源(XT1CLK,XT2CLK,VLOCLK,REFOCLK,DCOCLK,DLOCLKDIV)在產生時還有一些基礎的配置。二、時鐘源產生模塊分析1、osc模塊這一部分是外接了一個振蕩器(可以是手表晶體振蕩器、標.

2022-02-15 06:17:26

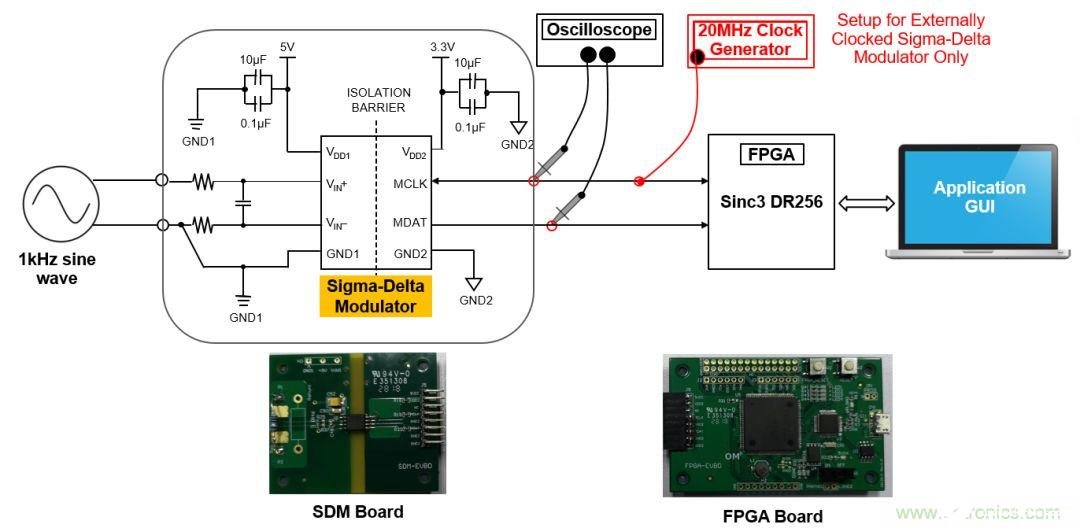

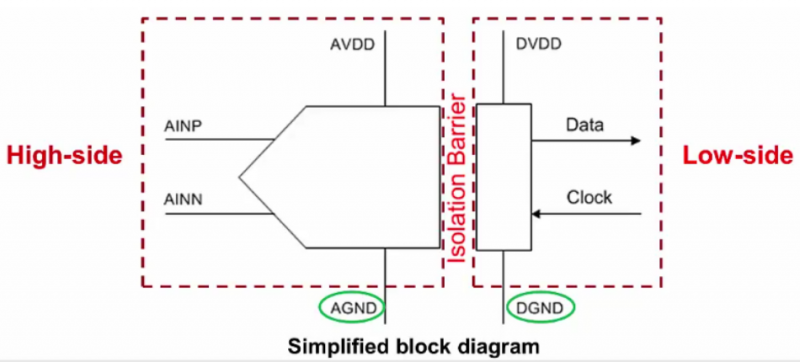

的基本分析開始,如圖1所示。 圖 1:Δ-Σ調制器內部框圖 調制器根據調制器時鐘運行,決定了輸入的采樣間隔。調制循環通過對輸入采樣和1位DAC之間的差分進行積分而開始。比較器根據積分器值確定下一個調制器

2019-08-12 04:45:06

因素,例如成本、功耗以及性能水平,但對大多數系統設計人員而言,一個重要目標是在成本控制范圍內提高效率。F從霍爾效應傳感器到分流電阻與隔離式Σ-Δ調制器耦合的分流電阻可提供最優質的電流反饋,其中的電流

2018-10-10 18:14:01

成本、功耗以及性能水平,但對大多數系統設計人員而言,一個重要目標是在成本控制范圍內提高效率。F從霍爾效應傳感器到分流電阻與隔離式Σ-Δ調制器耦合的分流電阻可提供最優質的電流反饋,其中的電流

2018-10-18 11:27:14

電阻 與隔離式Σ-Δ調制器耦合的分流電阻可提供最優質的電流反 饋,其中的電流電平足夠低。目前,系統設計人員明顯傾向于 從霍爾效應傳感器轉移到分流電阻,并且與隔離式放大器方案 相比,設計人員更傾向于采用隔離式

2018-10-18 10:49:28

如何設計一個程序,使它可以收到外界指令調整信號速率,產生信號速率可調的0,1信號?我的想法時先產生一個速率很高的時鐘,然后按不同抽樣率對它抽樣,但明顯這樣效率不夠高,請問大家有什么辦法呢

2014-11-06 21:43:10

擴頻時鐘調制器DS1081L資料下載內容主要介紹了:DS1081L引腳功能DS1081L功能和特性DS1081L應用范圍DS1081L內部方框圖DS1081L極限參數DS1081L典型應用電路

2021-04-02 07:34:06

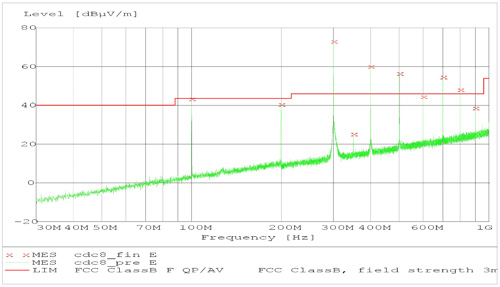

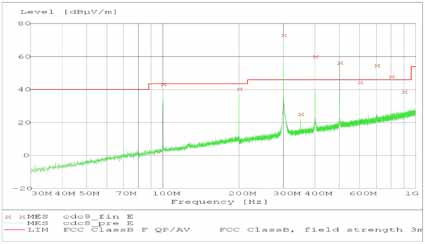

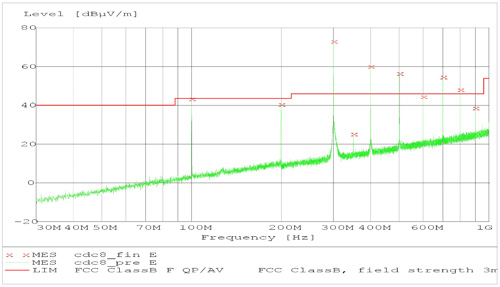

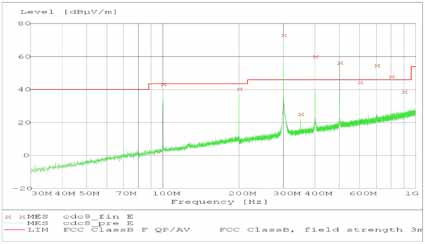

,EMI 可通過頻譜分析儀測量,如圖1 所示。圖中,綠色信號存在一些超出紅色 FCC 屏蔽的頻率分量(300MHz、400MHz 和 500MHz 等)。 控制時鐘引起 EMI 的一些方法都基于上述兩種

2018-09-19 14:42:35

MS2400是瑞盟科技推出的一款二階Σ-Δ調制器,集成片上數字隔離器,能將模擬輸入信號轉換為高速1位碼流。調制器對輸入信號連續采樣,無需外部采樣保持電路。模擬信號輸入滿量程為±320 mV,轉換后

2021-10-12 12:14:32

存在于信號之間的寄生電感/電容,或者通過電源或接地連接的無用耦合,從而產生 EMI;或者2)直接通過電子/磁輻射,即輻射性 EMI。由于兩個原因,時鐘信號常歸咎于 EMI。即使時鐘低頻率運行,較好的時鐘

2022-11-23 06:43:42

我做的一個基于DSP的系統中,DSP做主處理器,控制著整個系統,包括信號處理,整體調度等;選擇了一塊Xilinx的FPGA做FIFO UART和系統的邏輯控制和譯碼。DSP的時鐘輸入為15MHz

2023-06-19 06:43:17

你們好,

我們正在使用AD9779A進行設計,有如下疑問:

(1) 使用AD9779A的數據時鐘信號(DATACLK)作為FPGA內部PLL的參考時鐘,再用FPGA PLL產生的時鐘信號把數據

2023-12-20 07:12:27

我們一般使用FPGA都需要有外部時鐘信號輸入,在經過分頻倍頻等操作實現特定的功能,我想問問,能不能用FPGA自己產生時鐘信號,不需要外部輸入時鐘信號???求解答!

2019-05-24 04:05:29

時鐘產生和分發設計指南:在您設計時鐘電路時是否僅僅因為某些方法在過去一直沿用,所以就采用它呢?或者您曾經使用過某個器件僅僅是因為其他設計中使用了它?這種現象在如

2009-09-06 09:01:45 0

0 16MHZ至134MHZ擴展頻譜時鐘調制器DS1083L是擴展頻譜時鐘調制器IC可降低時間數字電子設備的EMI

2010-04-09 15:19:22 18

18

SPWM調制方法對比分析

摘要:對比分析了三種正弦波脈寬調制(SPWM)控制方法,指出各自的優缺點及應用,給出了一些數學

2009-07-06 13:33:51 12452

12452

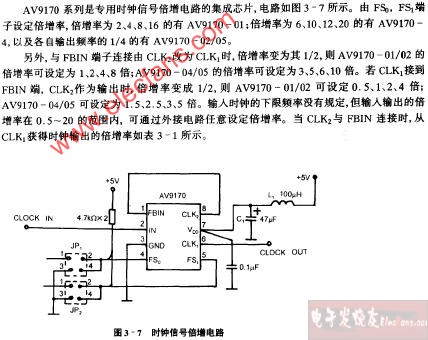

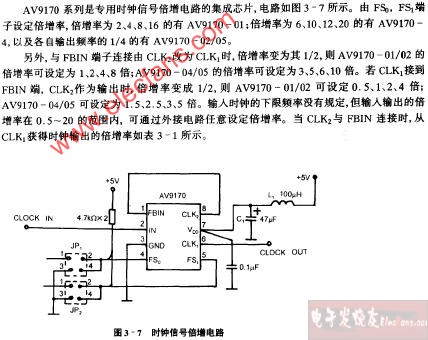

時鐘信號倍增電路圖

2009-07-14 17:18:36 741

741

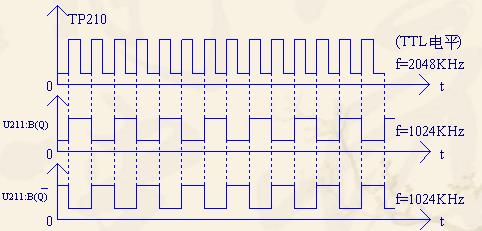

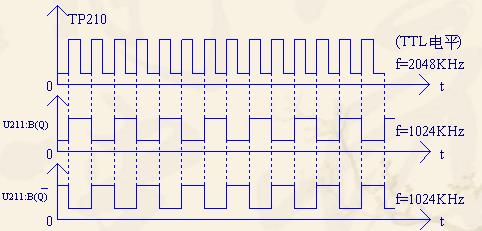

2048KHz(2M)時鐘信號產生電路

2009-10-11 10:20:02 2807

2807

控制板級時鐘分配期間出現的EMI

今天,我們來談談所有電子系統都存在的一種常見問題——電磁干擾也即 EMI,并側重討論時鐘的影響。

從廣義來講,EMI&n

2010-01-19 11:13:14 1958

1958

控制板級時鐘分配期間出現的 EMI

今天,我們來談談所有電子系統都存在的一種常見問題——電磁干擾也即 EMI,并側重討論時鐘的影響。

從廣義來講,EMI 是

2010-01-21 09:36:19 874

874

本文簡要介紹了SSC擴頻時鐘的基本概念以及如何使用力科示波器進行信號的擴頻時鐘的測試。

2011-05-17 11:23:34 4648

4648

所謂門控時鐘就是指連接到觸發器時鐘端的時鐘來自于組合邏輯;凡是組合邏輯在布局布線之后肯定會產生毛刺,而如果采用這種有毛刺的信號來作為時鐘使用的話將會出現功能上的錯

2011-09-07 16:11:32 34

34 基于片上偏差對芯片性能的影響,分析對比了時鐘樹設計與時鐘網格設計,重點分析了時鐘網格抗OCV影響的優點,并利用實際電路應用兩種方法分別進行設計對比,通過結果分析,驗證

2012-05-07 14:13:14 36

36 時鐘抖動時域分析(下):

2012-05-08 15:26:25 29

29 跨時鐘域信號的同步方法應根據源時鐘與目標時鐘的相位關系、該信號的時間寬度和多個跨時鐘域信號之間的時序關系來選擇。如果兩時鐘有確定的相位關系,可由目標時鐘直接采集跨

2012-05-09 15:21:18 63

63 ASM3P2182A是一個多才多藝的擴頻頻率調制器專門為范圍廣泛的輸入時鐘頻率從25兆赫到210兆赫。 ASM3P2182A可以產生EMI減少時鐘從OSC或生成一個系統時鐘。 ASM3P2182A

2017-04-06 10:24:19 7

7 的直列式電機相電流感應。調制器輸出采用曼徹斯特編碼,簡化了 MCU 和調制器之間的時鐘和數據信號路由。該調制器具有高 CMTI,有助于抑制逆變器開關噪聲瞬變在控制器側造成數據損壞。采用小尺寸調制器,實現了

2017-12-10 09:34:48 0

0 時鐘周期也稱為振蕩周期,定義為時鐘頻率的倒數。時鐘周期是計算機中最基本的、最小的時間單位。在一個時鐘周期內,CPU僅完成一個最基本的動作。時鐘周期是一個時間的量。時鐘周期表示了SDRAM所能運行的最高頻率。更小的時鐘周期就意味著更高的工作頻率。

2018-03-11 10:07:52 49788

49788 ,SSCG通過時鐘內部集成電路調制頻率的手段來達到抑制EMI峰值的目的。SSCG不僅調制時鐘源,其它的同步于時鐘源的數據、地址和控制信號,在時鐘展頻的同時也一并得以調制,整體的EMI峰值都會因此減小,所以說,時鐘展頻是系統級的解決方案。這是SSCG相比其它抑制EMI措施的最大優勢。

2018-08-22 14:45:27 8872

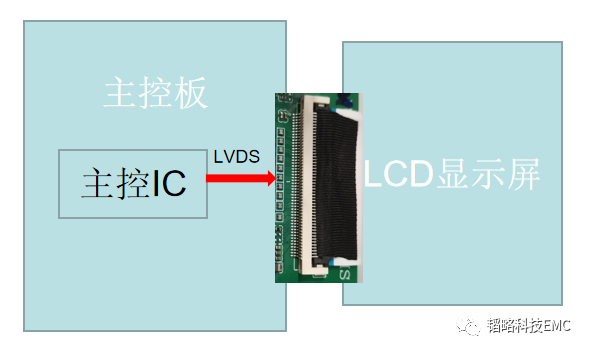

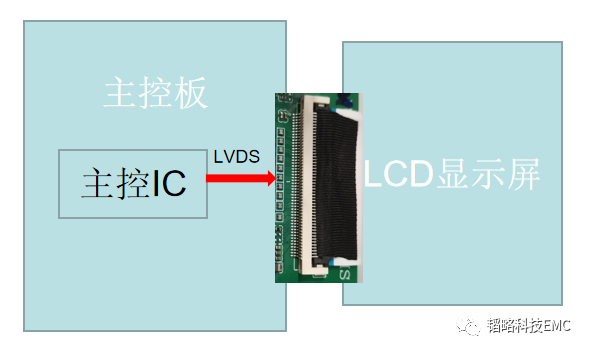

8872 對信號進行調制,將信號能量擴展到一個較寬的頻率范圍內,能有效的抑制系統的EMI問題。一、具體案列分析:客戶的樣機是工業類機器人,樣機中帶屏,屏的時鐘取自主芯片。如上圖,這是客戶沒有整改之前測試的實驗

2018-11-06 14:53:48 742

742 首先,我們看一下時鐘信號中最常見到的波形 - 矩形波(尤其是方波更常用)。在較低時鐘頻率的系統中我們看到的基本上都是以矩形波為主的時鐘信號,因為電路基本上都是靠時鐘的邊沿(上升沿或下降沿)進行

2018-12-06 11:53:10 59988

59988

想象一下,如果頻率較高的時鐘域A中的信號D1 要傳到頻率較低的時鐘域B,但是D1只有一個時鐘脈沖寬度(1T),clkb 就有幾率采不到D1了,如圖1。

2019-02-04 15:52:00 10841

10841

電子產品多功能化、高速化、小型化的發展,意味著對內部時鐘頻率的要求將越來越高。因為時鐘信號是周期信號,所以在頻域上的能量是集中在某個頻率上的,這也就造成了時鐘EMI測試超標的問題。

2019-02-02 16:25:00 5368

5368 隔離的Σ-Δ調制器長期以來被證明可以在嘈雜的工業電機應用環境中提供非常高的精度和強勁的電流和電壓感測能力。有兩類隔離型Σ-Δ調制器:一種是在IC內部產生時鐘信號;另一種是從外部時鐘源接收時鐘信號。

2019-07-27 09:22:29 750

750 跨時鐘域問題(CDC,Clock Domain Crossing )是多時鐘設計中的常見現象。在FPGA領域,互動的異步時鐘域的數量急劇增加。通常不止數百個,而是超過一千個時鐘域。

2019-08-19 14:52:58 2854

2854 隔離調制器是一種將模擬輸入信號轉換為由0和1組成的高速數字比特流,同時使用隔離層將輸入和輸出電路隔離開來的Δ-Σ調制器。該隔離層對電磁干擾有很強的抵抗力,電磁干擾通常稱為EMI。干擾由外部源產生且會對電路產生負面影響。

2019-09-14 10:02:00 1655

1655

SSDCI1108AF是減少電磁干擾(EMI)的時鐘發生器。利用內調制器對振蕩頻率進行周期性的微調,可以使不必要的電磁干擾(EMI)峰值衰減。SSDCI1108AF接收來自基本晶體或外部基準的輸入時鐘,并鎖定到該輸入時鐘,以傳遞1x調制時鐘輸出。

2020-04-17 08:00:00 10

10 。 不要隨意將內部信號作為時鐘,如門控時鐘和分頻時鐘,而要使用CLKDLL或者DCM產生的時鐘,或者可以通過建立時鐘使能或者DCM產生不同的時鐘信號。 FPGA盡量采取同步設計,也就是所有時鐘都是同一個源頭,如果使用兩個沒有相位關系的異步時鐘,必須

2020-12-11 10:26:44 1482

1482 電子產品多功能化、高速化、小型化的發展,意味著對內部時鐘頻率的要求將越來越高。因為時鐘信號是周期信號,所以在頻域上的能量是集中在某個頻率上的,這也就造成了時鐘EMI測試超標的問題。

2020-11-11 10:33:28 5091

5091 在本文中,將詳細研究這兩類隔離-調制器的輸出數據信號完整性。并通過簡單的電磁干擾(EMI)測試設置、對由這兩類-調制器的高頻時鐘信號產生的EMI進行比較。 對輸出數據信號完整性和時鐘信號電磁干擾

2020-11-18 14:59:50 996

996 超低抖動時鐘的產生與分配

2021-04-18 14:13:51 8

8 的錯誤操作而泄露文中對時鐘故障的產生原因進行了分析,并描述了幾種主要的毛刺注入機制,包括相同頻率時鐘切換、不同頻率時鐘切換以及模糊時鐘注入。最后介紹了3種時鐘毛刺注入攻擊的最新實際運用和未來的發展方向。

2021-04-26 14:20:04 9

9 時鐘芯片運行需要時鐘支持,如果沒有時鐘電路來產生時鐘驅動時鐘芯片,那時鐘芯片就不能執行程序。時鐘芯片可以看成是在時鐘驅動下的時序邏輯電路。

2021-05-18 09:29:14 12258

12258 PLL設計和時鐘頻率產生機理免費下載。

2021-06-07 14:36:43 22

22 stm32內部時鐘有哪些時鐘源 在STM32中,可以用內部時鐘,也可以用外部時鐘,在要求進度高的應用場合最好用外部晶體震蕩器,內部時鐘存在一定的精度誤差。 內部時鐘有2個時鐘源可以選分別是HSI

2021-07-22 10:38:57 15728

15728 門控時鐘的設計初衷是實現FPGA的低功耗設計,本文從什么是門控時鐘、門控時鐘實現低功耗的原理、推薦的FPGA門控時鐘實現這三個角度來分析門控時鐘。 一、什么是門控時鐘 門控時鐘技術(gating

2021-09-23 16:44:47 12193

12193

/4,1/8;(4)RTC時鐘單獨控制時鐘,時鐘頻率1KHz;(5)各外設時鐘可以單獨門控,滿足低功耗要求。1.2 時鐘設計要點 (1)DFT可控,隔離,可觀測。(2)上電工作外部參考...

2021-11-05 17:35:59 8

8 振蕩器 產生內部時鐘 SMCLK 子系統時鐘時鐘系統配置寄存器DCO控制寄存器 DCOCTL1、DCOx 頻率選擇 8種頻率2、MODx DAC調制器設定 微調DCO 的輸出頻率基本時鐘系統控制寄存器 BCSCTL1 BCSCTL2BCSCTL11、XT2OFF :XT2高速晶振開關

2021-11-19 21:06:06 18

18 信號-SOC-IN OSC-OUT懸空HSI:8MHz RC產生 做系統時鐘或2分頻后PLL輸入相對HSE優點為啟動時間短 置“1”,輸出時鐘釋放系統復位1 HSIAL[7:0]位...

2021-12-02 13:36:06 0

0 信號-SOC-IN OSC-OUT懸空HSI:8MHz RC產生 做系統時鐘或2分頻后PLL輸入相對HSE優點為啟動時間短 置“1”,輸出時鐘釋放系統復位1 HSIAL[7:0]位...

2021-12-22 18:59:46 0

0 如果用單獨的時鐘信號板,一般采用什么樣的接口,來保證時鐘信號的傳輸受到的影響小?

2022-09-16 08:58:49 1919

1919

本章的主要內容: 分析時鐘驅動器、時鐘信號的特殊布線 改進時鐘信號分配的特殊電路

2022-09-20 14:55:40 0

0 時鐘信號在很大程度上決定了整個設計的性能和可靠性,盡量避免使用FPGA內部邏輯產生的時鐘,因為它很容易導致功能或時序出現問題。內部邏輯(組合邏輯)產生的時鐘容易出現毛刺,影響設計的功能實現;組合邏輯固有的延時也容易導致時序問題。

2022-10-26 09:04:51 823

823 控制板級時鐘分配期間出現的 EMI

2022-11-07 08:07:32 0

0 時鐘使能電路是同步設計的基本電路,在很多設計中,雖然內部不同模塊的處理速度不同,但由于這些時鐘是同源的,可以將它們轉化為單一時鐘處理;在ASIC中可以通過STA約束讓分頻始終和源時鐘同相

2023-01-05 14:00:07 949

949 隔離放大器的輸入級由一個驅動輸入放大器-ΔΣ調制器的輸入放大器組成。輸入放大器的增益由內部精度電阻器進行固定和設置,ΔΣ調制器則使用內部參考電壓和時鐘發生器來將模擬輸入信號轉換為數字位流。

2023-02-10 15:12:49 749

749 RF DAC的無雜散動態范圍受到嚴重的數字do主開關的限制,這會干擾模擬輸出信號。介紹了一種擴頻時鐘發生器(SSCG)的設計、布局和仿真。SSCG調制用于切換DAC數字塊的時鐘頻率,以減少DAC

2023-02-14 16:43:56 0

0 時鐘電路是一種電路,它可以產生定期的時鐘信號,用于控制電子設備的運行。

它的特點是可以產生定期的時鐘信號,可以控制電子設備的運行,可以提高電子設備的精度和可靠性。時鐘電路的應用非常廣泛,它可

2023-02-20 18:16:38 5974

5974 系統時序設計中對時鐘信號的要求是非常嚴格的,因為我們所有的時序計算都是以恒定的時鐘信號為基準。但實際中時鐘信號往往不可能總是那么完美,會出現抖動(Jitter)和偏移(Skew)問題。

2023-04-04 09:20:56 1637

1637 理想值附近的一個范圍內,從而造成相鄰的時鐘邊沿存在偏差。在時序分析時,時鐘抖動是一個重要的因素。多種因素會導致時鐘抖動,包括PLL回路噪聲、電源紋波、熱噪聲以及信號之間的串擾等。

2023-06-09 09:40:50 1128

1128

即電路中的所有受時鐘控制的單元,全部由一個統一的全局時鐘控制

2023-06-27 09:54:21 377

377

跨時鐘域是如何產生的呢?現在的芯片(比如SOC,片上系統)集成度和復雜度越來越高,通常一顆芯片上會有許多不同的信號工作在不同的時鐘頻率下。

2023-06-27 11:39:41 902

902

時鐘電路用于產生穩定的時鐘信號,常見于數字系統、微處理器、微控制器、通信設備等。時鐘信號用于同步各個電子元件的操作和數據傳輸,確保系統的正常運行。

2023-08-03 14:46:04 1242

1242 單位寬(Single bit)信號即該信號的位寬為1,通常控制信號居多。對于此類信號,如需跨時鐘域可直接使用xpm_cdc_single,如下圖代碼所示。參數DEST_SYNC_FF決定了級聯觸發器

2023-08-16 09:53:23 462

462

如何抑制時鐘電路產生的電磁輻射? 在現代電子工業中,時鐘電路是不可或缺的,尤其是在數字電路中,時鐘電路起著控制數據流動的作用。然而,在時鐘電路運行時,它會產生電磁輻射,這會對周圍的設備和人體健康造成

2023-09-12 17:06:49 557

557 件、計算機、數字電路和通訊協議等設備的信號。它的主要作用是進行時序控制,使數據傳輸和處理的時序保持一致。時鐘信號一般由計時器產生,其具有一定的周期性、穩定性和精度。 時鐘信號的主要信號參數包括周期、頻率、精度和占空比等,

2023-09-15 16:28:12 1767

1767 芯片為什么需要時鐘信號? 在我們日常生活中,我們所使用的各種電子設備都需要一個時鐘信號來進行計時和同步,例如:手機、電腦、電視、汽車、機器人、智能家居等設備都需要時鐘信號。對于各種這些電子設備

2023-09-15 16:28:14 1370

1370 時鐘信號怎么產生的 時鐘信號是一種重要的信號,它在電子設備中廣泛應用。時鐘信號的產生與傳輸是現代電子設備中不可或缺的基礎技術之一。時鐘信號的精確性和準確性是現代電子設備能夠實現高速計算等復雜操作

2023-09-15 16:28:22 1496

1496 是數據信號(SDA)。SCL信號是在IIC通信中非常重要的一個信號,它確定了數據的傳輸速率以及同步時序。 IIC時鐘信號的產生需要硬件支持,一般通過外部晶振或者內部時鐘源產生。在IIC總線使用過程中,時鐘信號的頻率很重要,必須要與所有設備的時鐘頻率保持一致。一般來說,為了保證

2023-09-19 17:16:02 735

735 方法來使不同步的時鐘信號同步。下面我們就來詳細講解這些方法。 1. 時鐘緩沖器同步法 時鐘緩沖器同步法是指通過一個時鐘緩沖器來同步兩個不同步的時鐘信號。其原理是將一個時鐘信號通過一個緩沖器反轉,產生一個相反的信號,

2023-10-18 15:23:48 771

771 可以說是計算機運行的重要組成部分之一。 時鐘芯片的工作原理: 時鐘芯片是通過一系列簡單的電路來實現的,它內部包含一個晶體振蕩器,用來產生一個穩定的基準信號。這個基準信號通過分頻器分成不同頻率的信號輸出到不同的電

2023-10-25 15:02:33 2317

2317 什么器件可以產生時鐘信號?時鐘信號是用來做什么用的?時鐘信號起什么作用? 時鐘信號是一個精確的電信號,它可以通過電子器件來產生,并且具有一定的頻率和周期。時鐘信號在電子系統中具有非常重要的作用,因為

2023-10-25 15:07:45 637

637 如何用時鐘振蕩器產生穩定的100hz或1hz的時鐘信號? 時鐘信號是電子系統中至關重要的組成部分,用于同步各種信號和操作。它需要穩定、準確、可靠地工作,以確保系統性能。時鐘信號的產生可以通過許多

2023-10-25 15:07:55 959

959 什么是時鐘電路?什么是脈沖?時鐘電路是如何生成脈沖的? 時鐘電路是一種電路,它產生的周期性的信號被用作計算機系統的基準。時鐘電路產生的信號被稱為時鐘脈沖或時鐘信號。在計算機系統中,時鐘信號用于同步

2023-10-25 15:14:17 795

795 時鐘合成器和時鐘發生器是兩種用于產生時鐘信號的電子器件,它們在功能和應用上有一些區別。

2023-11-09 10:26:56 298

298 如何有效解決LVDS時鐘EMI問題

2023-11-23 09:04:46 485

485

對測試結果產生一定的影響。本文將詳細探討差分探頭對時鐘測試的影響。 首先,差分探頭的接觸電阻是一個重要的因素。接觸電阻會產生測量誤差,并且對于高頻時鐘信號來說影響更加顯著。由于差分探頭通常連接在被測電路的信號路

2024-01-08 15:36:28 178

178 什么是時鐘信號?數字電路的時鐘信號是怎么產生呢? 時鐘信號,也稱為時鐘脈沖,是用于同步數字電路中所有操作的基本信號。它提供了一個參考頻率,使得所有電路元件都能按照同樣的節奏進行工作。時鐘信號

2024-01-25 15:40:52 909

909 芯片為什么要時鐘信號 時鐘芯片的作用是什么? 時鐘信號在芯片中起著非常重要的作用。它是芯片的“心臟”,相當于人體的心臟,用于同步和控制芯片中的各個功能模塊之間的操作。時鐘信號可以提供一個穩定的時間

2024-01-29 18:11:31 626

626 SPICE是一種用于模擬和分析電子電路的計算機程序。在SPICE仿真中,產生時鐘信號是許多電路設計和模擬任務中的關鍵步驟。

2024-02-06 14:22:01 265

265

電子發燒友App

電子發燒友App

評論