0 引言

隨著信息化社會的發展,越來越多的電子產品經常在一起工作,它們之間的干擾也越來越嚴重,所以,電磁兼容(EMC)問題也就成為一個電子系統能否正常工作的關鍵。現在的電子產品一般都會有嚴格的EMC標準,而為了達到這些標準我們都會在系統設計中更多地考慮對于EMI的抑制或者減輕。但是對于系統而言最好能在單板設計的過程中就考慮這些問題,因為電路雖然工作在板級,但是可能對系統的其他部件輻射噪音、干擾,從而引起系統級的問題。而要在單板設計中就考慮EMC的問題,設計者就要從選擇器件、設計電路和做PCB Layer等方面著手。對于設計電路和做PCB Layer方面已經有許多的規則和一般經驗來考慮EMI的問題,例如增加走線之間的距離減少電容耦合的干擾;將電源和地平行布置來最大化PCB的電容;將敏感及高頻的走線盡量遠離高干擾的電源走線;加寬電源和地的走線來減少電源線和地線之間的阻抗等。

本文主要從元器件的選擇,尤其是普通的電子元器件方面來考慮對于EMI的抑制。對于單板電路設計而言,我們不可能將EMC放在首要位置來考慮,但是在不影響電路功能的前提下,對于一些普通電子元器件的優化選擇,尤其是電阻、電容和電感的優化選擇,會對EMC的提高起到到事半功倍的作用。每種電子元器件都有自己的特性,所以元器件的選擇在電路設計中就顯得尤為重要,以下主要從電阻、電容、電感以及集成電路四方面的選擇來考慮對于EMI的抑制。

1 電阻的選擇

在單板電路設計中,電阻是最普通也是最常用的元器件。但電阻的種類十分繁多,各個類型都有自己的優缺點和合適的使用場合,因此在合適的電路中選擇適合的電阻顯得尤為重要,有以下一些一般指導可供參考:

從封裝形式上來看,表面貼裝的電阻比插裝的電阻的寄生效應更低,所以首要選擇表面貼裝的電阻。

從有鉛封裝和無鉛封裝上看,無鉛封裝的器件肯定優選。有鉛封裝的元器件存在著寄生效應,尤其在高頻范圍內,鉛構成了一個低值電感,大概1nH/mm lead。在終端也可以產生一個小的電容效應,在4pf左右,因此應盡可能地減少鉛的長度。無鉛的元器件相較而言有更小的寄生效應,大約為1nH/mm lead電感效應和0.3pf左右的終端電容。

對于有鉛封裝的電阻而言也有選擇順序,由高到低的選擇次序為:碳膜電阻、金屬氧化膜電阻、線繞電阻。金屬氧化膜電阻在低頻(MHz以下)有顯性的寄生影響,所以它一般適合用在大功率密度和高精度的電路中,這就是我們在精密電阻中往往選擇金屬氧化膜電阻的原因。線繞電阻有很高的敏感度,所以應當避免在頻率敏感的電路中應用,線繞電阻最好在大功率處理電路中使用。

在不同的應用電路中,電阻放置的位置也尤為重要。在放大電路設計中,電阻的選擇極為重要。在高頻范圍內,由于在電阻上的感應影響,阻抗會增大,所以增益調整的電阻應盡可能地放置在靠近放大電路的地方,來降低電路板的感應系數;在上拉、下拉電阻的電路中,晶體管和IC電路的快速通斷會引起開關噪音。為了降低這種影響,所有的偏置電阻都應當盡可能地放在靠近有源器件的地方;在穩壓及相關電路中,直流偏置電阻都應當盡可能地放在靠近有源器件的地方來降低去耦影響;其次在我們常用的RC濾波網絡中,必須考慮電阻的感應影響,因為線繞電阻的寄生感應極容易引起本地振蕩。

2 電容的選擇

電容是解決許多EMC問題的重要器件,但是電容有不同的類型和行為反應,所以電容的選擇并不是一件容易的事情。這里我們就最普通的電容的類型、特性和用法等來闡述電容的選擇。

鋁電解電容通常是在兩個電解質中間纏上螺旋狀的金屬箔構成,每單位體積可以達到很高的電容值,但是也增加了內部的感應系數;鉭電容由帶直接焊盤和腳位連接的塊電解質構成,它有比電解電容小的感應系數;陶瓷電容由多層的金屬和陶瓷介質組成,在低于1MHz的頻率范圍內有顯性的寄生效應。不同類型的電容有著不同的介質,而不同的介質對不同的頻率有不同的響應,所以說電容的選擇和使用的頻率范圍有著密切的關系。鋁和鉭電解電容在低頻結尾處有優勢,主要在蓄能和低頻電路中使用;在中頻范圍內(kHz~MHz)陶瓷電容有優勢,主要用作去耦和高頻濾波;低漂移的陶瓷電容和云母電容主要用在超高頻或者微波電路中。

不管什么類型的電容,我們一般都用作兩個方面,旁路和去耦。所以我們也可以根據應用場合將電容分為旁路電容和去耦電容兩大類。對于同一個電路來說,旁路(bypass)電容是把輸入信號中的高頻噪聲作為濾除對象,把前級攜帶的高頻雜波濾除,旁路電容的主要作用是對于交流旁路,濾掉從敏感區域進入的干擾。旁路電容主要擔當高頻的旁路器件,來減少在電源部分的瞬態電流的要求。通常,鋁和鉭電容是旁路電容的最佳選擇,它們的取值取決于PCB上瞬態電流的需要,通常取值在10~470UF。而去耦(decoupling)電容也稱退耦電容,是把輸出信號的干擾作為濾除對象。去耦電容的作用是局部穩定有源器件的直流電源,減少通過板子傳播的開關噪音,將這些噪音去耦到地。

我們經常可以看到,在電源和地之間連接著去耦電容,它有三個方面的作用:一是作為本集成電路的蓄能電容;二是濾除該器件產生的高頻噪聲,切斷其通過供電回路進行傳播的通路;三是防止電源攜帶的噪聲對電路構成干擾。

影響去耦電容效率的因素是電容的介質材料,生產去耦電容常用兩種材料,一種是鋇鈦氧體(Z5U),另一種是鍶鈦氧體(NPO),Z5U有更大的介電常數,它的諧振頻率從1MHz到20MHz,NPO的介電常數比較小,有較高的諧振頻率(超過10MHz),所以Z5U更適合在低頻電路中做去耦電容,而NPO更適合在高頻電路中(超過50MHz)。

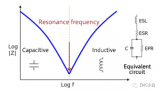

就理想狀態而言,旁路電容和去耦電容應當在電源入口的地方盡量靠近放在一起,來濾掉高頻噪聲,去耦電容的取值大約是旁路電容的1/100到1/1000,去耦電容應當盡可能靠近IC器件,因為導線電阻會降低去耦電容的作用。陶瓷電容常常被用來起去耦作用,其取值取決于最快信號的上升/下降沿的時間。舉例來說,對于33MHz的時鐘頻率,使用4.7nF到100nf的去耦電容,對于100MHz的時鐘頻率,使用10nF。另一方面,電容的等效串聯電阻對信號有衰減作用,會影響電容的去耦作用,特別是工作頻率接近于電容的諧振頻率時。為了最佳的EMC性能,電容最好有很小的等效串聯電阻,所以最好選用等效串聯電阻小于1 Ω的電容。

電容在電路中的加入常常是為了提高抗EMI,但在不考慮電容的諧振頻率的情況下,濾波的性能并不是很好。理想電容的阻抗是隨著頻率的升高降低,而實際電容的阻抗不是這樣的,在頻率較低的時候,呈現電容特性,即阻抗隨頻率的增加而降低,在某一點發生諧振,在這點電容的阻抗等于等效串聯電阻ESR。在諧振點以上,由于ESR的作用,電容阻抗隨著頻率的升高而增加,這是電容呈現電感的阻抗特性。在諧振點以上,由于電容的阻抗增加,因此對高頻噪聲的旁路作用減弱,甚至消失。

我們在使用過程中往往并聯使用去耦電容,這種做法可以減少更大頻寬的由電源引起的開關噪聲。在抑制由有源器件開關時產生的射頻電流方面,多個并行去耦電容可以提高6dB的作用。多個去耦電容不只是提供一個更大頻寬的分配,它們還可以提供更大的引線寬度來降低導線電感,更大的提升去耦作用。兩個并行電容的取值應當不同,相差兩個數量級左右,比如說0.1UF和0.01UF的兩個并行去耦電容,來獲得更好的去耦效應。還要注意在數字電路的去耦中,低的ESR比諧振頻率更重要,因為低的ESR提供一個到地的小電阻,可以提供充足的去耦作用,即使在超過諧振頻率時,電容等效于電感的時候。

3 電感的選擇

電感是電場和磁場的連接器件,因為可以和磁場相互影響固有的本性,所以電感比其他元器件更敏感。和電容一樣,當我們恰當的應用電感時,它可以解決許多EMC的問題。

從封裝方面來看,電感相比電容或者電阻的好處是它沒有寄生感應,所以插裝電感和貼裝電感幾乎沒有什么不同。

電感有兩種中心材料:鐵或鐵氧體。鐵中心材料電感一般用于低頻應用中(幾十kHz),而鐵氧體中心材料電感一般用于高頻(MHz)。因此,鐵氧體中心材料電感更適合用在EMC應用中。由于鐵氧體在衰減較高頻的同時讓較低頻幾乎無阻礙地通過,故在EMI控制中得到了廣泛的應用。用于EMI吸收的磁環/磁珠可制成各種的形狀,廣泛應用于各種場合。如在PCB板上,可加在DC/DC模塊、數據線、電源線等處。它吸收所在線路上的高頻干擾信號,卻不會在系統中產生新的零極點,不會破壞系統的穩定性。它與電源濾波器配合使用,可很好地補充濾波器高頻端性能的不足,改善系統中濾波特性。

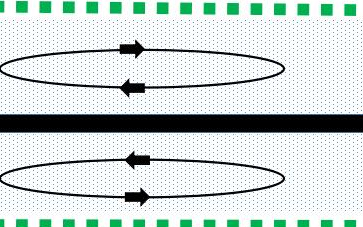

有兩種電感經常用在EMC的應用中,一個是ferrite beads(鐵氧體磁珠),ferrite clamps(鐵氧體磁芯)。鐵氧體磁珠是一個簡單的旋轉電感,有一個引線通過鐵氧體材料組成。在高頻方面提供10dB的衰減,在直流方面的衰減很小。鐵氧體磁芯和鐵氧體磁珠相似,在頻率超過MHz的區域提供10 dB到20dB的衰減,無論是在共模或差模模式下。電感經常用在LC濾波或交流濾波中。

4 集成電路的選擇

現代的數字集成電路大多是基于CMOS技術制造的。CMOS器件的靜態功耗比較低,但是快速開關CMOS器件需要從電源處有更多的瞬態功率分配。一個高速CMOS器件對電源的動態要求可能會超過一個類似的Bipolar(TTL)器件。因此在這些器件旁邊需要使用去耦電容來減少對電源的瞬態需要。

對于組合邏輯電路,時鐘抖動、電力線諧波可能會在使用不同種類的邏輯器件時產生,例如CMOS和TTL,這主要是因為它們有不同的開關門限。為了避免這種問題,最好使用同類邏輯器件。現在多數設計者選擇CMOS器件時因為它們有一個很高的干擾極限。由于使用CMOS技術制造,CMOS邏輯器件是和微控制器接口的首選邏輯器件。很重要的一點是使用CMOS器件時,輸入腳位在不使用的時候應當接地或者接到電源,因為在MCU電路中,噪音干擾也會使這些沒有使用的輸入端口變得無規律的變化,有可能使MCU執行不該執行的代碼。

現在集成電路的封裝五花八門,但是總體而言,集成電路的引線越短,EMI的問題就越少。所以表面貼裝的集成電路是EMC設計的最佳選擇,因為它有低的寄生效應和回路面積。更進一步地提高PCB上直接使用芯片綁定的方法。

IC管腳的排列方法也會影響EMC的效能。將IC的電源供給線放在IC封裝的中央,可以獲得從芯片核到封裝管腳最短的引線長度,也就具有更低的引線感應系數,接近的VCC和IGND管腳可以使去耦電容更容易布局和作用更明顯。

在單板電路設計中或整個系統中,時鐘電路是影響EMC效能的主要因素之一。許多從IC而來的干擾都和時鐘頻率或者它的諧振分量有關。這就需要更好的電路設計和PCB Layout技術應用在系統時鐘設計中來減小這些干擾。良好的接地,充足的去耦電容和旁路電容都可以減小這些輻射。在CLOCK的分配上使用高阻抗的緩沖也可以減小從時鐘信號而來的反射和噪音干擾。

5 結束語

總之,電子元器件的選擇是一個很復雜的問題,對于電路的設計者而言,不光是要考慮元器件的性能,元器件的質量等級、EMC都已經成為設計之初設計者必須考慮的問題。本文主要介紹了在單板設計中通過選用合適的普通電子元器件來減少或抑制EMI的影響。對于設計者而言簡單元器件如電阻、電容、電感的選擇是可以控制件,在電路中選擇合適的器件會對我們整個系統的EMC問題打下良好的基礎。

電子發燒友App

電子發燒友App

評論