最近在做一個(gè)項(xiàng)目時(shí),我不得不對(duì)幾組電子電線進(jìn)行重新布線,讓它們遠(yuǎn)離越野車的發(fā)電機(jī),因?yàn)殡娙蓠詈袭a(chǎn)生的噪聲可從發(fā)電機(jī)進(jìn)入電線。這個(gè)項(xiàng)目讓我想起了在通過電線、帶狀線纜或板對(duì)板連接器路由相互之間相鄰信號(hào)時(shí)所遇到的類似情況。

2015-04-03 11:06:48 5011

5011

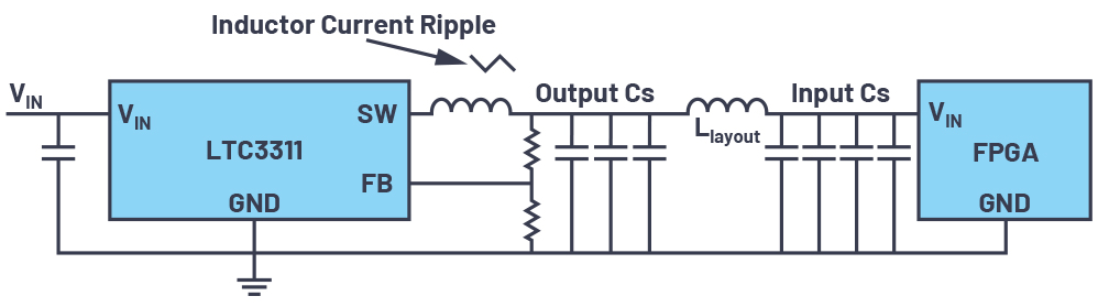

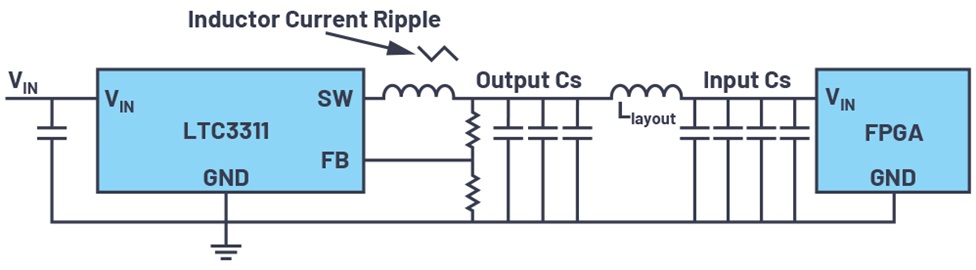

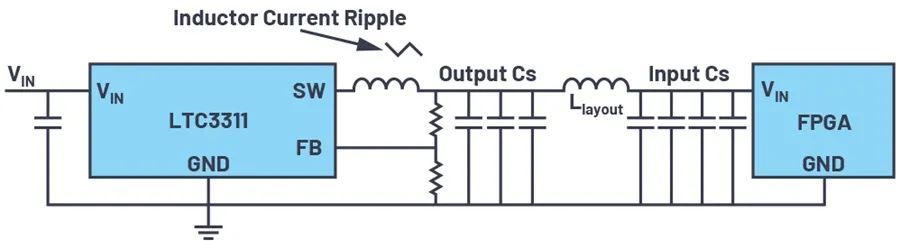

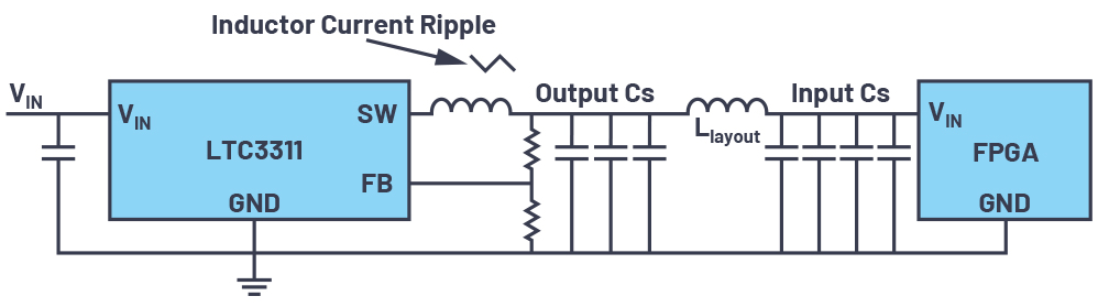

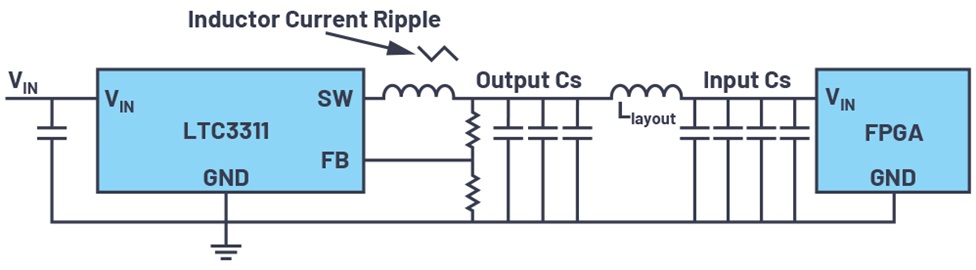

電源輸出電容一般是100 nF至100 μF的陶瓷電容,它們耗費(fèi)資金,占用空間,而且,在遇到交付瓶頸的時(shí)候還會(huì)難以獲得。所以,如何最大限度減小輸出電容的數(shù)量和尺寸,這個(gè)問題反復(fù)被提及。

2022-03-18 11:14:52 2472

2472

STPOWER MDmesh K6 新系列超級(jí)結(jié)晶體管改進(jìn)多個(gè)關(guān)鍵參數(shù),最大限度減少系統(tǒng)功率損耗,特別適合基于反激式拓?fù)涞恼彰鲬?yīng)用。

2021-10-26 11:53:38 823

823

模式2所產(chǎn)生的噪聲電壓Vn。R為電阻,C為電容,M為互感,Vs為噪聲源電壓,Is為噪聲源電流。在這里請(qǐng)記住,平行的布線間會(huì)發(fā)生串擾。順便提一下,如果布線是正交結(jié)構(gòu),則雜散電容和互感都會(huì)顯著減少。關(guān)鍵

2018-11-29 14:29:12

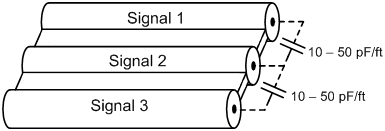

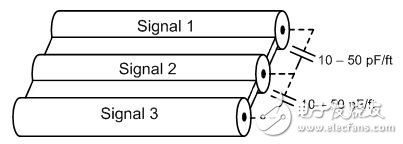

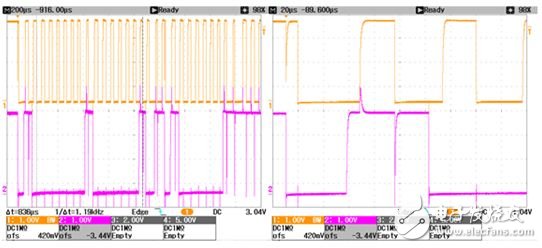

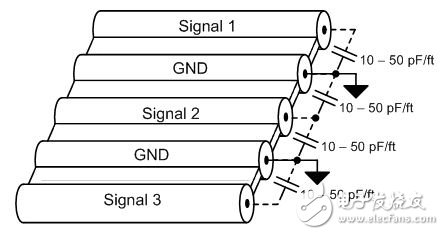

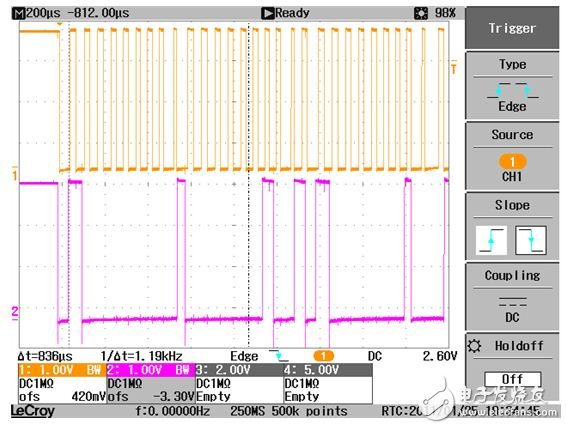

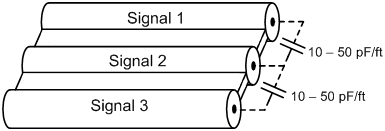

之間產(chǎn)生 10 至 50 pF/ft 的電容,如下圖 1 所示。圖1. 帶狀線纜中相鄰電線間的電容由于信號(hào)會(huì)相互干擾,兩條信號(hào)線之間的電容會(huì)引起信號(hào)延遲、噪聲耦合或瞬態(tài)電壓。圖 2 是電纜電容在通用雙線

2018-09-19 10:55:31

解決方案,以最大限度地減少電源驅(qū)動(dòng)設(shè)備的功耗、電壓尖峰和過熱。產(chǎn)品營(yíng)銷和應(yīng)用經(jīng)理Allen Chen表示:“我們依賴這些價(jià)值不菲的小裝置中的電池可靠性,并盡可能長(zhǎng)時(shí)間保持充電。您絕對(duì)不想讓無(wú)人機(jī)在湖上

2019-08-09 04:45:04

請(qǐng)問如何最大限度的減小在汽車環(huán)境中的EMI?

2021-04-13 06:57:09

雙ISP camera 芯片Android的應(yīng)用軟件一般情況下會(huì)用到其中的一種或者幾種硬件,功耗主要來源于硬件,通過以下幾種方式說明如何最大限度的降低應(yīng)用軟件的功耗。應(yīng)用軟件與可穿戴設(shè)備,例如智能

2018-09-19 18:11:19

隨著現(xiàn)代微控制器和SoC變得越來越復(fù)雜,設(shè)計(jì)者面臨著最大化能源效率,同時(shí)實(shí)現(xiàn)更高水平的集成。最大限度地提高能量在低功耗SoC市場(chǎng)中,多個(gè)功率域的使用被廣泛采用。在

同時(shí),為了解決更高級(jí)別的集成,許多

2023-08-02 06:34:14

DN249-LTC1628-SYNC最大限度地減少多輸出,大電流電源中的輸入電容

2019-06-17 08:42:47

PCB設(shè)計(jì)中如何處理串擾問題 變化的信號(hào)(例如階躍信號(hào))沿

2009-03-20 14:04:47

變化的信號(hào)(例如階躍信號(hào))沿傳輸線由A到B傳播,傳輸線C-D上會(huì)產(chǎn)生耦合信號(hào),變化的信號(hào)一旦結(jié)束也就是信號(hào)恢復(fù)到穩(wěn)定的直流電平時(shí),耦合信號(hào)也就不存在了,因此串擾僅發(fā)生在信號(hào)跳變的過程當(dāng)中,并且

2018-08-29 10:28:17

變化的信號(hào)(例如階躍信號(hào))沿傳輸線由A到B傳播,傳輸線C-D上會(huì)產(chǎn)生耦合信號(hào),變化的信號(hào)一旦結(jié)束也就是信號(hào)恢復(fù)到穩(wěn)定的直流電平時(shí),耦合信號(hào)也就不存在了,因此串擾僅發(fā)生在信號(hào)跳變的過程當(dāng)中,并且信號(hào)

2020-06-13 11:59:57

?對(duì)串擾有一個(gè)量化的概念將會(huì)讓我們的設(shè)計(jì)更加有把握。1.3W規(guī)則在PCB設(shè)計(jì)中為了減少線間串擾,應(yīng)保證線間距足夠大,當(dāng)線中心間距不少于3倍線寬時(shí),則可保持大部分電場(chǎng)不互相干擾,這就是3W規(guī)則。如(圖1

2014-10-21 09:53:31

6mil,線間距為12mil,滿足3W原則。圖7為當(dāng)RT=0.3ns 各個(gè)電路的串擾圖形。攻擊線1V的驅(qū)動(dòng)信號(hào),受害線中微帶線最大近端串擾為11mv,微帶線最大遠(yuǎn)端串擾為12mv,帶狀線最大近端串擾為

2014-10-21 09:52:58

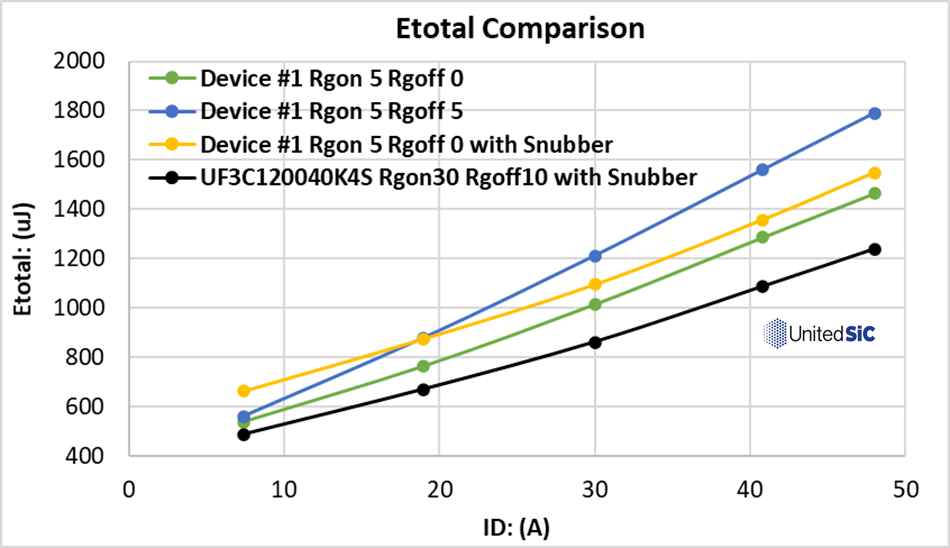

。將功率 MOSFET 并聯(lián)時(shí),設(shè)計(jì)人員必須更密切地注意如何最大限度降低這些影響,因?yàn)槠骷g的電流分配不均會(huì)影響性能。例如,在開關(guān)瞬變過程中,在并聯(lián)中增加一個(gè)器件會(huì)使 di/dt 倍增,從而可能導(dǎo)致

2022-03-24 18:03:24

模式2所產(chǎn)生的噪聲電壓Vn。R為電阻,C為電容,M為互感,Vs為噪聲源電壓,Is為噪聲源電流。在這里請(qǐng)記住,平行的布線間會(huì)發(fā)生串擾。順便提一下,如果布線是正交結(jié)構(gòu),則雜散電容和互感都會(huì)顯著減少。關(guān)鍵

2019-03-21 06:20:15

串擾的概念是什么?到底什么是串擾?

2021-03-05 07:54:17

什么是串擾?互感和互容電感和電容矩陣串擾引起的噪聲

2021-02-05 07:18:27

DN186- 優(yōu)化的DC / DC轉(zhuǎn)換器環(huán)路補(bǔ)償最大限度地減少了大輸出電容器的數(shù)量

2019-08-06 07:09:13

使用DMM和交換機(jī)系統(tǒng)時(shí)最大限度地縮短總體測(cè)試時(shí)間的技術(shù)

2019-08-15 14:35:47

相互作用時(shí)就會(huì)產(chǎn)生。在數(shù)字電路系統(tǒng)中,串擾現(xiàn)象相當(dāng)普遍,串擾可以發(fā)生在芯片內(nèi)核、芯片的封裝、PCB板上、接插件上、以及連接線纜上,只要有臨近的銅互連鏈路,就存在信號(hào)間的電磁場(chǎng)相互作用,從而產(chǎn)生串擾現(xiàn)象

2016-10-10 18:00:41

DN247- 雙相高效移動(dòng)CPU電源,可最大限度地減小尺寸和熱應(yīng)力

2019-07-29 11:00:26

描述 此項(xiàng) 25W 的設(shè)計(jì)在反激式拓?fù)渲惺褂?UCC28740 來最大限度降低空載待機(jī)功耗,并使用 UCC24636同步整流控制器來最大限度減少功率 MOSFET 體二極管傳導(dǎo)時(shí)間。此設(shè)計(jì)還使用來

2022-09-23 06:11:58

在數(shù)字無(wú)線通信產(chǎn)品測(cè)試中最大限度地降低電源瞬態(tài)電壓......

2019-08-19 07:42:24

在設(shè)計(jì)fpga的pcb時(shí)可以減少串擾的方法有哪些呢?求大神指教

2023-04-11 17:27:02

的電容,如下圖 1 所示。圖 1. 帶狀線纜中相鄰電線間的電容由于信號(hào)會(huì)相互干擾,兩條信號(hào)線之間的電容會(huì)引起信號(hào)延遲、噪聲耦合或瞬態(tài)電壓。圖 2 是電纜電容在通用雙線開漏通信總線中引起大量瞬態(tài)電壓的實(shí)例

2022-11-23 07:51:41

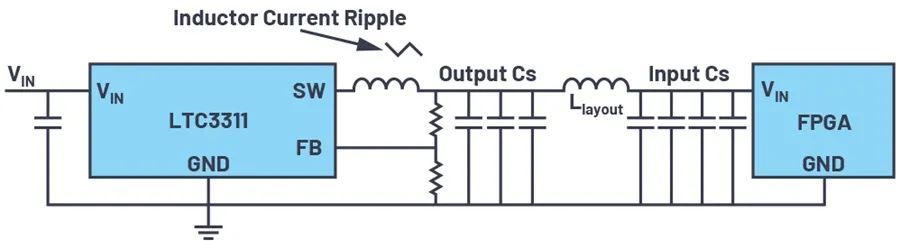

電源輸出電容一般是100 nF至100 μF的陶瓷電容,它們耗費(fèi)資金,占用空間,而且,在遇到交付瓶頸的時(shí)候還會(huì)難以獲得。所以,如何最大限度減小輸出電容的數(shù)量和尺寸,這個(gè)問題反復(fù)被提及。輸出電容造成

2022-06-14 10:19:20

電源輸出電容一般是100 nF至100 μF的陶瓷電容,它們耗費(fèi)資金,占用空間,而且,在遇到交付瓶頸的時(shí)候還會(huì)難以獲得。所以,如何最大限度減小輸出電容的數(shù)量和尺寸,這個(gè)問題反復(fù)被提及。 輸出電容造成

2022-03-21 14:42:45

在測(cè)量電源噪聲中我們會(huì)面臨各種挑戰(zhàn),包括RF干擾和信噪比(SNR),接下來我們來看如何在測(cè)量中實(shí)現(xiàn)高帶寬,同時(shí)最大限度地減少DUT上的電流負(fù)載?鑒于DUT是電源軌,我們不希望從它汲取太多電流。但是

2021-12-30 06:19:45

大家好, 昨天我剛剛得到了stm8s-discovery board。我不知道如何最大限度地利用它。因?yàn)槲也恢烙糜趕tm的編譯器來構(gòu)建代碼和關(guān)于STM的其他信息,直到今天我對(duì)AVR很熟悉請(qǐng)不要

2019-01-25 12:03:32

最大限度提高Σ-Δ ADC驅(qū)動(dòng)器的性能

2021-01-06 07:05:10

如何最大限度的去實(shí)現(xiàn)LTE潛力?

2021-05-25 06:12:07

如何在密集PCB布局中,最大限度降低多個(gè)isoPower器件的輻射?請(qǐng)參考以下幾個(gè)要點(diǎn):*最大程度降低每個(gè)通道的電源要求*在多個(gè)PCB層上構(gòu)建拼接*采用盡可能多的PCB層切實(shí)可行*在各參考層間使用最薄的電介質(zhì)*在相鄰域之間進(jìn)行連接*確保內(nèi)部和外部爬電距離仍然符合要求*電纜連接上提供過濾

2018-10-11 10:40:15

1394物理層所具備的優(yōu)勢(shì)是什么?如何采用1394技術(shù)最大限度地優(yōu)化安全攝像頭網(wǎng)絡(luò)?

2021-05-25 06:25:20

在嵌入式系統(tǒng)硬件設(shè)計(jì)中,串擾是硬件工程師必須面對(duì)的問題。特別是在高速數(shù)字電路中,由于信號(hào)沿時(shí)間短、布線密度大、信號(hào)完整性差,串擾的問題也就更為突出。設(shè)計(jì)者必須了解串擾產(chǎn)生的原理,并且在設(shè)計(jì)時(shí)應(yīng)用恰當(dāng)?shù)?b class="flag-6" style="color: red">方法,使串擾產(chǎn)生的負(fù)面影響降到最小。

2019-11-05 08:07:57

布局電源板以最大限度地降低EMI:第3部分

2019-08-16 06:13:31

布局電源板以最大限度地降低EMI:第1部分

2019-09-05 15:36:07

布局電源板以最大限度地降低EMI:第2部分

2019-09-06 08:49:33

許多高速數(shù)據(jù)采集應(yīng)用,如激光雷達(dá)或光纖測(cè)試等,都需要從嘈雜的環(huán)境中采集小的重復(fù)信號(hào),因此對(duì)于數(shù)據(jù)采集系統(tǒng)的設(shè)計(jì)來說,最大的挑戰(zhàn)就是如何最大限度地減少噪聲的影響。利用信號(hào)平均技術(shù),可以讓您的測(cè)量

2019-07-03 07:01:20

消除串擾的方法合理的PCB布局-將敏感的模擬部分與易產(chǎn)生干擾的數(shù)字部分盡量隔離,使易產(chǎn)生干擾的數(shù)字信號(hào)走線上盡量靠近交流地,使高頻信號(hào)獲得較好的回流路徑。盡量減小信號(hào)回路的面積,降低地線的阻抗,采用多點(diǎn)接地的方法。使用多層板將電源與地作為獨(dú)立的一層來處理。合理的走線拓樸結(jié)構(gòu)-盡量采用菊花輪式走線

2009-06-18 07:52:34

在我的應(yīng)用程序中,HSPDM 觸發(fā) EVADC 同時(shí)對(duì)兩個(gè)通道進(jìn)行采樣。

我應(yīng)該如何配置 EVADC 以最大限度地減少采樣抖動(dòng)并最大限度地提高采樣率?

在用戶手冊(cè)中,它提到 SSE=0,USC=0

2024-01-18 07:59:23

外部之間的干擾,不得不說,串擾讓線纜結(jié)構(gòu)越來越復(fù)雜。在工程施工中,如何提高串擾呢?首先,在原材料上把好關(guān)。要對(duì)購(gòu)買的整箱雙絞線進(jìn)行驗(yàn)貨,只有通過驗(yàn)貨測(cè)試,我們才能避免購(gòu)買不合格的線纜或假線。而在驗(yàn)貨環(huán)節(jié)

2018-01-19 11:15:04

,發(fā)送時(shí)間11ms左右,發(fā)現(xiàn)LDO的輸出總是有5ms 0.3V壓降,看手冊(cè),TPS2830可以提供150mA的電流。請(qǐng)問有什么辦法可以最大限度的消除這個(gè)壓降嗎?謝謝!

2019-07-31 10:28:47

DN468- 通過精心的IF信號(hào)鏈設(shè)計(jì)最大限度地提高16位,105Msps ADC的性能

2019-09-04 14:09:04

DN371- 高效率2相升壓轉(zhuǎn)換器可最大限度地降低輸入和輸出電流紋波

2019-08-15 07:27:09

可能出現(xiàn)在電路板、連接器、芯片封裝以及線纜上。本文將剖析在高速PCB板設(shè)計(jì)中信號(hào)串擾的產(chǎn)生原因,以及抑制和改善的方法。?

?????? 串擾的產(chǎn)生

?????? 串擾是指信號(hào)在傳輸通道

2018-08-28 11:58:32

數(shù)值比較接近。從圖4中的仿真結(jié)果我們可以得出在上述實(shí)例中差分過孔間的串擾起主要作用。差分過孔間串擾的優(yōu)化了解了此類問題產(chǎn)生串擾的根源,優(yōu)化差分過孔之間串擾的方法就比較明確了。增加差分過孔之間的間距

2020-08-04 10:16:49

最大限度地減少組件的

2009-04-25 11:00:05 702

702

最大限度地減少組件的

2009-05-05 11:13:30 483

483

最大限度地減少組件的

2009-05-07 09:13:49 612

612

筆記本最大限度延長(zhǎng)電池的使用壽命

本文將討論如何有效地使用電池,以及最大限度地延長(zhǎng)電池的使用壽命。本文將只討論最新的XTRA這幾個(gè)使用了鋰電池的系列,對(duì)于較

2010-04-19 09:20:34 851

851 機(jī)器監(jiān)測(cè):通過性能測(cè)量,最大限度提高生產(chǎn)質(zhì)量。

2016-03-21 16:34:53 0

0 Plunify?基于機(jī)器學(xué)習(xí)技術(shù)的現(xiàn)場(chǎng)可編程門陣列(FPGA)時(shí)序收斂和性能優(yōu)化軟件供應(yīng)商,今天推出了Kabuto?,可最大限度地減少和消除性能錯(cuò)誤。

2018-07-04 12:24:00 2657

2657 如果你是一名負(fù)責(zé)搭建嵌入式系統(tǒng)(或軟件、設(shè)備、網(wǎng)絡(luò)等)的工程師或開發(fā)者,那么你排在最高優(yōu)先級(jí)之一的事情是(或應(yīng)該是)鑒別并最大限度的減少潛在的數(shù)據(jù)安全漏洞。要想有效的實(shí)現(xiàn)這個(gè)目標(biāo),你需要了解系統(tǒng)是如何被黑客入侵的,最終要理解如何“像黑客一樣思考”。

2018-07-13 14:54:00 878

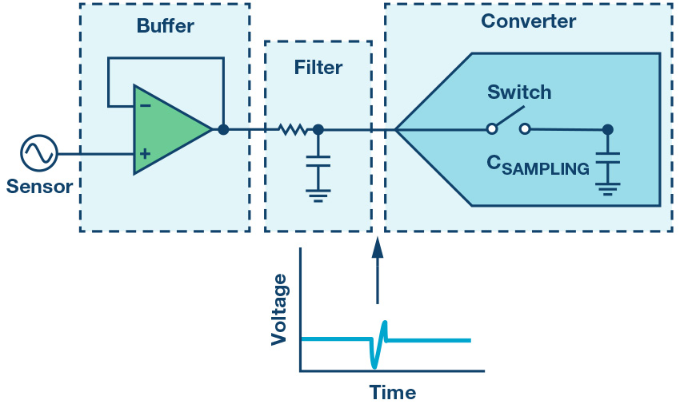

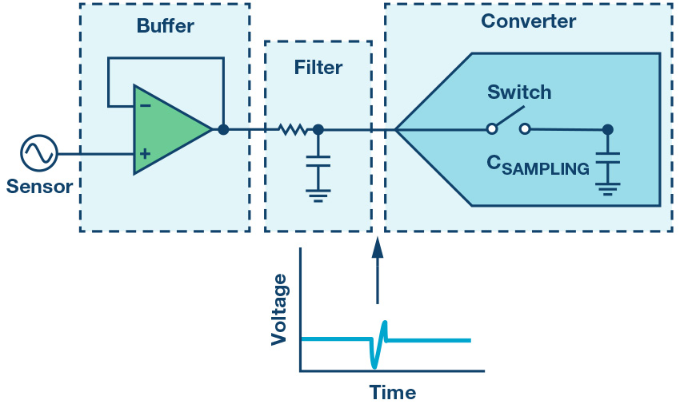

878 放大器級(jí)的設(shè)計(jì)由兩個(gè)彼此相關(guān)的不同級(jí)組成,因此問題變得難以在數(shù)學(xué)上建模,特別是因?yàn)橛蟹蔷€性因素與這兩級(jí)相關(guān)。第一步是選擇用來緩沖傳感器輸出并驅(qū)動(dòng)ADC輸入的放大器。第二步是設(shè)計(jì)一個(gè)低通濾波器以降低輸入帶寬,從而最大限度地減少帶外噪聲。

2019-07-29 11:29:37 1497

1497

在新冠肺炎疫情防控期間,要最大限度阻止病毒傳播,關(guān)鍵是減少人與人之間的接觸。旨在解決“最后一公里”配送問題的各大電商平臺(tái)和無(wú)人配送公司紛紛加入戰(zhàn)“疫”,無(wú)人配送車、無(wú)人機(jī)、配送機(jī)器人輪番上陣,在疫情

2020-03-13 08:53:07 3224

3224 對(duì)于高層建筑物來說,在消防設(shè)計(jì)中充分考慮建筑物的火災(zāi)事故隱患,最大限度的減少火災(zāi)事故造成的人員傷亡和財(cái)產(chǎn)損失,是一項(xiàng)及其重要的任務(wù)。高層建筑物一旦發(fā)證火災(zāi)事故,對(duì)人員生命威脅最大的是大量的有毒有害

2020-11-09 15:03:24 415

415 理想二極管橋控制器最大限度地減少整流器發(fā)熱量和電壓損失

2021-03-19 09:54:08 3

3 最大限度地減小汽車 DDR 電源中的待機(jī)電流

2021-03-20 17:22:52 1

1 LTC3555 - 開關(guān)模式 USB 電源管理器和三路降壓型穩(wěn)壓器,可實(shí)現(xiàn)更快速的充電并最大限度地減少熱量

2021-03-20 20:02:20 1

1 LTC3567 - 集成 1A 降壓-升壓型穩(wěn)壓器和 I2C 接口的開關(guān)模式USB 電源管理器最大限度延長(zhǎng)電池工作時(shí)間并減少熱量

2021-03-20 23:11:14 6

6 LTC3556 - 具開關(guān)模式 USB 電源管理器、一個(gè)降壓-升壓型穩(wěn)壓器和兩個(gè)降壓型穩(wěn)壓器的 PMIC 最大限度延長(zhǎng)電池工作時(shí)間和減少熱量

2021-03-21 08:17:26 9

9 DN468-精心設(shè)計(jì)IF信號(hào)鏈,最大限度提高16位、105Msps ADC的性能

2021-04-14 09:56:02 6

6 DN186優(yōu)化的DC/DC變換器環(huán)路補(bǔ)償最大限度地減少了大輸出電容器的數(shù)量

2021-04-30 09:20:03 3

3 蓄能電池管理系統(tǒng)中最大限度提高電池監(jiān)測(cè)精度和數(shù)據(jù)完整性

2021-05-18 11:08:07 4

4 DN468-精心設(shè)計(jì)IF信號(hào)鏈,最大限度提高16位、105Msps ADC的性能

2021-06-18 10:27:30 4

4 電子發(fā)燒友網(wǎng)站提供《最大限度地提高高壓轉(zhuǎn)換器的功率密度.doc》資料免費(fèi)下載

2023-12-06 14:39:00 308

308 電線、帶狀線纜或板對(duì)板連接器路由相互之間相鄰信號(hào)時(shí)所遇到的類似情況。

正如采用絕緣體隔離的任何其它導(dǎo)體一樣,任何相鄰布線的兩條電線都會(huì)在其之間產(chǎn)生電容。根據(jù)所用的線規(guī)和絕緣體材料,大部分標(biāo)準(zhǔn)帶狀線纜

2021-11-21 16:30:13 1935

1935

每年消耗 25 萬(wàn)億千瓦時(shí)的電力,其中 53% 是由傳統(tǒng)電動(dòng)機(jī)消耗的。因此,在減少碳足跡的同時(shí)最大限度地提高效率是一項(xiàng)強(qiáng)制性任務(wù)。

2022-08-04 17:22:02 2337

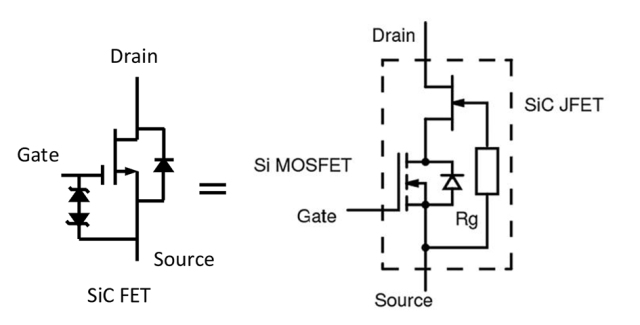

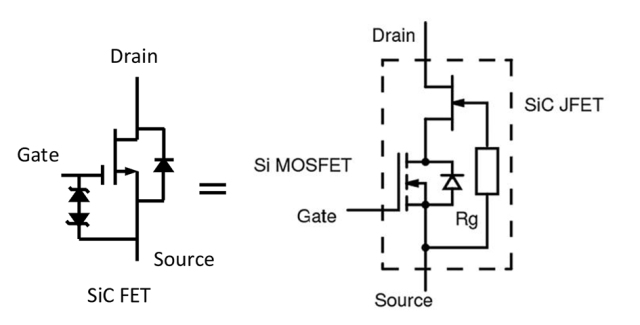

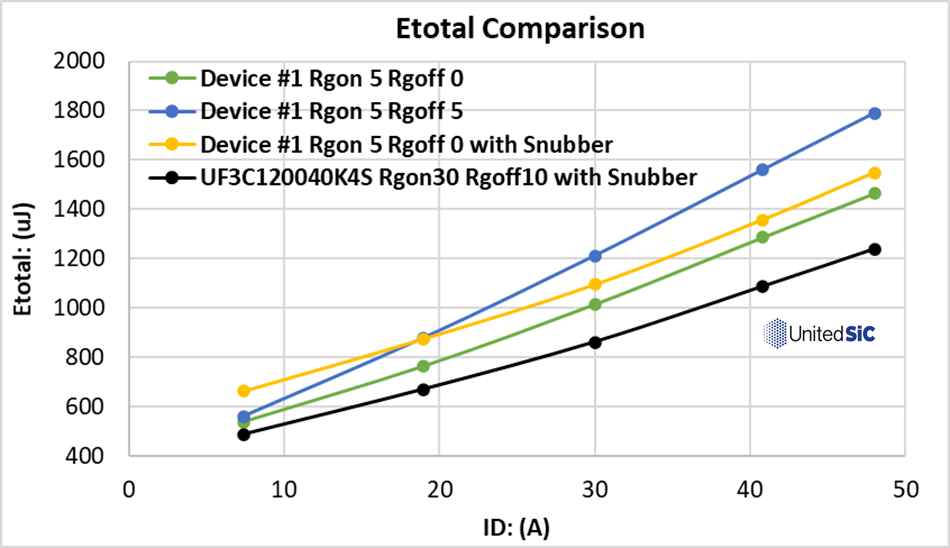

2337 SiC FET 速度極快,邊緣速率為 50 V/ns 或更高,這對(duì)于最大限度地減少開關(guān)損耗非常有用,但由此產(chǎn)生的 di/dt 可能達(dá)到每納秒數(shù)安培。這會(huì)通過封裝和電路電感產(chǎn)生高電平的電壓過沖和隨后

2022-08-04 09:30:05 729

729

智慧家庭系列文章 | 如何最大限度地減少智能音箱和智能顯示器的輸入功率保護(hù)

2022-10-31 08:23:54 0

0 一次性按鈕開關(guān)幫助最大限度延長(zhǎng)閑置時(shí)間

2022-11-04 09:52:06 0

0 時(shí)鐘采樣系統(tǒng)最大限度減少抖動(dòng)

2022-11-04 09:52:12 0

0 如何最大限度減少線纜設(shè)計(jì)中的串?dāng)_

2022-11-07 08:07:26 1

1 AN2014_設(shè)計(jì)者如何最大限度使用ST單片機(jī)

2022-11-21 17:07:41 0

0 如何最大限度地提高電子設(shè)備中能量收集的效率

2022-12-30 09:40:14 616

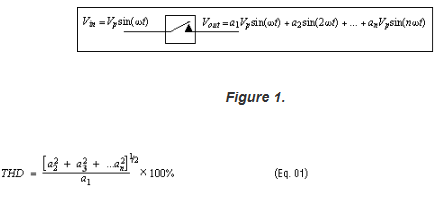

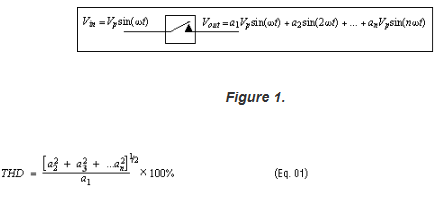

616 THD規(guī)格在確定通過音頻系統(tǒng)或由音頻系統(tǒng)生成的音頻信號(hào)的質(zhì)量或保真度方面起著至關(guān)重要的作用。因此,在設(shè)計(jì)音頻系統(tǒng)時(shí),必須重視選擇合適的元件和電路板布局,以最大限度地降低THD。

2023-01-16 15:55:45 1273

1273

使用直角齒輪電機(jī)最大限度地減少機(jī)器占地面積

2023-03-09 15:16:36 865

865

電子發(fā)燒友網(wǎng)站提供《最大限度地利用太陽(yáng)能讓您的家保持溫暖.zip》資料免費(fèi)下載

2023-06-13 15:20:06 0

0 電源輸出電容一般是100 nF至100 μF的陶瓷電容,它們耗費(fèi)資金,占用空間,而且,在遇到交付瓶頸的時(shí)候還會(huì)難以獲得。所以,如何最大限度減小輸出電容的數(shù)量和尺寸,這個(gè)問題反復(fù)被提及。

2023-06-16 10:25:19 372

372

開關(guān)穩(wěn)壓器,使用戶能夠在短短幾分鐘內(nèi)查看大多數(shù)開關(guān)穩(wěn)壓器的波形。 ? 精密的圖形用戶界面 LTspice是一種易于理解的電子電路模擬器,它使用戶不僅可以查看數(shù)值數(shù)據(jù),還可以查看模擬結(jié)果的圖形波形。 通過與LTspice 鏈接最大限度地減少設(shè)計(jì)重新設(shè)計(jì)并加速您的仿真 Quadcept允許用戶為

2023-06-26 16:04:18 623

623

電子發(fā)燒友網(wǎng)站提供《最大限度地提高數(shù)據(jù)庫(kù)效率和性能VMware環(huán)境使用32G NVMe光纖渠道.pdf》資料免費(fèi)下載

2023-08-07 10:10:18 0

0 電子發(fā)燒友網(wǎng)站提供《使用端到端HPE StoreFabric Gen 5 16GFC光纖通道最大限度地發(fā)揮所有閃存的潛力.pdf》資料免費(fèi)下載

2023-08-30 17:05:39 0

0 電子發(fā)燒友網(wǎng)站提供《切換以最大限度地利用SAN.pdf》資料免費(fèi)下載

2023-09-01 11:23:25 0

0 最大限度地減少SIC FETs EMI和轉(zhuǎn)換損失

2023-09-27 15:06:15 236

236

電子發(fā)燒友網(wǎng)站提供《最大限度提高∑-? ADC驅(qū)動(dòng)器的性能.pdf》資料免費(fèi)下載

2023-11-22 09:19:34 0

0 最大限度保持系統(tǒng)低噪聲

2023-11-27 16:58:00 161

161

如何最大限度減小電源設(shè)計(jì)中輸出電容的數(shù)量和尺寸?

2023-12-15 09:47:18 183

183

快充對(duì)電池有傷害嗎 如何最大限度地減少快充對(duì)電池的影響 快速充電(也被稱為快充)是一種可快速給手機(jī)電池充電的技術(shù)。雖然快充在我們?nèi)粘I钪袔砹吮憷芏嗳藫?dān)心它是否會(huì)對(duì)手機(jī)電池的壽命產(chǎn)生負(fù)面影響

2024-02-19 10:01:02 308

308

電子發(fā)燒友App

電子發(fā)燒友App

評(píng)論