電磁干擾的PCB設計方法

電磁干擾(Electromagnetic InteRFerence),簡稱EMI,有傳導干擾和輻射干擾兩種。傳導干擾主要是電子設

2009-04-07 22:13:01 843

843 隨著信號上升沿時間的減小及信號頻率的提高,電子產品的EMI問題越來越受到電子工程師的關注,幾乎60%的EMI問題都可以通過高速PCB來解決。以下是高速PCB設計抗EMI干擾的九大規則: 規則一:高速

2018-04-13 08:20:00 1567

1567

一站式PCBA智造廠家今天為大家講講高速PCB設計中的屏蔽方法有哪些?高速PCB設計中的屏蔽方法高速PCB設計布線系統的傳輸速率隨著時代的更迭也在不斷加快,但這也給其帶來了一個新的挑戰——抗干擾能力

2023-08-08 10:19:06 790

790

PCB設計布線(Layout)的好壞將直接影響到整個系統的性能,大多數高速的設計理論也要最終經過 Layout 得以實現并驗證,由此可見,布線在高速 PCB 設計中是至關重要的。下面將針對實際布線中可能遇到的一些情況,分析其合理性,并給出一些比較優化的走線策略。

2016-07-18 14:07:10 46478

46478 PCB布線在PCB設計中,布線是完成產品設計的重要步驟,可以說前面的準備工作都是為它而做的, 在整個PCB中,以布線的設計過程限定最高,技巧最細、工作量最大。PCB布線有單面布線、 雙面布線及多層

2018-12-07 09:44:39

產品的PCB設計中,我們常常對某些模塊進行屏蔽1、電源模塊(PMU+DCDC+LDO)如圖1-3所示,通常電源模塊做為一個發熱源及干擾源存在于PCB上,對其加上一個屏蔽罩而已有效的降低其對外的輻射干擾

2019-02-26 11:35:44

請問PCB設計中如何避免平行布線?

2020-01-07 15:07:03

請問PCB設計中如何避免平行布線?

2020-02-26 16:39:38

耦合,高頻時常見的輻射耦合,切斷其耦合途徑是在設計時務必應該給予充分重視的。本文主要講解PCB設計時要注意的地方,從而減低PCB板中的電磁干擾問題 PCB的設計原則 由于電路板集成度和信號頻率隨著

2018-09-21 11:51:38

缐,一來可以稍微提昇屏蔽罩的電磁隔絕能力,另一方面也可以為屏蔽夾無效時,馬上可以更改為屏蔽框,而無需要重新設計電路板。 02 屏蔽罩的使用模塊 在MID或VR產品的PCB設計中,我們常常對某些模塊

2023-04-18 14:07:13

PCB設計中的電磁干擾問題PCB的干擾抑制步驟

2021-04-25 06:51:58

,但對于低于這一頻率的電磁波則進行很大的衰減,合理應用截至波導的這種特性可以很好的屏蔽EMI的干擾。3.3 電磁兼容的合理PCB設計隨著系統設計復雜性和集成度的大規模提高,電子系統設計師們正在

2012-11-05 13:30:04

PCB設計工程師在設計PCB時,往往很想使用自動布線。通常,純數字的電路板(尤其信號電平比較低,電路密度比較小時)采用自動布線是沒有問題的。但是,在設計模擬、混合信號或高速電路板時,如果采用PCB設計軟件的自動布線工具,可能會出現一些問題,甚至很可能帶來嚴重的電路性能問題。

2019-07-10 06:11:44

PCB設計中跨分割的處理高速信號布線技巧

2021-02-19 06:27:15

小竅門。 下面是經過多年設計總結出來的,在PCB設計中降低噪聲與電磁干擾的24個竅門: (1) 能用低速芯片就不用高速的,高速芯片用在關鍵地方。 (2) 可用串一個電阻的辦法,降低控制電路上下沿

2018-09-18 15:40:54

:降低噪聲與電磁干擾的24個竅門》為PCB設計中降低噪聲與電磁干擾提供了非常實用的建議,值得筒子們閱讀收藏。

2019-05-31 06:39:14

在PCB設計中,布線是完成產品設計的重要步驟,可以說前面的準備工作都是為它而做的,在整個PCB中,以布線的設計過程限定最高,技巧最細、工作量最大。PCB布線有單面布線、雙面布線及多層布線。布線的方式

2019-08-01 08:04:25

,PCB設計的好壞對電路的干擾及抗干擾能力影響很大。要使電子電路獲得最佳性能,除了元器件的選擇和電路設計之外,良好的PCB布線在電磁兼容性中也是一個非常重要的因素。既然PCB是系統的固有成分,在PCB布線中

2010-06-11 08:28:08

電磁干擾是由電磁效應而造成的干擾,由于PCB上的元器件及布線越來越密集,如果設計不當就會產生電磁干擾。 為了抑制電磁干擾,可采取如下措施: (1)合理布設導線 印制線應遠離干擾源且不

2018-08-31 11:09:59

干擾問題。 在電磁干擾的原因,總結出在PCB設計時應考慮的減小電磁干擾的措施與原則。 1 電路板存在電磁干擾的原因 在由開關電源和微處理器構成的高速電子系統中,電路板的電磁干擾主要來自于自身存在的射頻

2018-09-19 15:38:49

屏蔽PCB設計技巧Tips15:設備內部的布線PCB設計技巧Tips16:屏蔽電纜的接地PCB設計技巧Tips17: 如何提高電子產品的抗干擾能力和電磁兼容PCB設計技巧Tips18:DSP系統的降噪

2014-11-26 15:19:20

PCB設計技巧Tips15:設備內部的布線PCB設計技巧Tips16:屏蔽電纜的接地PCB設計技巧Tips17: 如何提高電子產品的抗干擾能力和電磁兼容PCB設計技巧Tips18:DSP系統的降噪技術

2014-11-19 15:43:00

,高靈敏度,高密度,這種趨勢導致了PCB電路板設計中的電磁兼容(EMC)和電磁干擾問題嚴重化,電磁兼容設計已成為PCB設計中急待解決的技術難題。 1 電磁兼容 電磁兼容(Electro

2018-09-11 15:07:53

設備內部的布線第十六篇屏蔽電纜的接地第十七篇如何提高電子產品的抗干擾能力和電磁兼容性第十八篇DSP 系統的降噪技術 第十九篇PowerPCB 在印制電路板設計中的應用技術第二十篇PCB 互連設計過程中

2011-04-29 17:50:10

的一些小竅門。 下面是經過多年設計總結出來的,在PCB設計中降低噪聲與電磁干擾的24個竅門: (1) 能用低速芯片就不用高速的,高速芯片用在關鍵地方。 (2) 可用串一個電阻的辦法,降低控制電路

2018-11-28 17:05:55

設計,一些心得和大家交流、交流。規則一、高速信號走線屏蔽規則如上圖所示:在高速的PCB設計中,時鐘等關鍵的高速信號線,走線需要進行屏蔽處理,如果沒有屏蔽或只屏蔽了部分,都是會造成EMI的泄漏。建議屏蔽

2021-03-31 06:00:00

通過高速PCB來控制解決。做了4年的EMI設計,一些心得和大家交流、交流。規則一、高速信號走線屏蔽規則 如上圖所示:在高速的PCB設計中,時鐘等關鍵的高速信號線,走線需要進行屏蔽處理,如果沒有屏蔽或只

2022-04-18 15:22:08

本帖最后由 eehome 于 2013-1-5 10:01 編輯

高速PCB板信號接地設計中存在接地噪聲及電磁輻射等問題,提出了高速PCB接地模型,并從PCB設計中布線策略的分析和去耦電容的使用等幾個方面討論了解決高速PCB板的接地噪聲和電磁輻射問題的方法。

2012-03-31 14:31:52

輻射的敏感性兩方面。EMI表現為當數字系統加電運行時,會對周圍環境輻射電磁波,從而干擾周圍環境中電子設備的正常工作。它產生的主要原因是電路工作頻率太高以及布局布線不合理。目前已有進行 EMI仿真的軟件工具,但

2015-05-05 09:30:27

高速PCB設計中常規PCB布線,有以下基本要求:(1)QFP、SOP等封裝的矩形焊盤出線,應從PIN中心引出(一般采用鋪shape)(2)布線到板邊的距離不小于20MIL。(3)金屬外殼器件下

2017-02-16 15:06:01

` 本帖最后由 飛翔的烏龜005 于 2017-2-10 10:43 編輯

高速PCB設計中常規PCB布線,有以下基本要求:(1)QFP、SOP等封裝的矩形焊盤出線,應從PIN中心引出(一般采用

2017-02-10 10:42:11

高速PCB設計布線系統的傳輸速率在穩步加快的同時也帶來了某種防干擾的脆弱性,這是因為傳輸信息的頻率越高,信號的敏感性增加,同時它們的能量越來越弱,此時的布線系統就越容易受干擾。 干擾無處不在,電纜

2018-11-28 17:00:27

高速PCB設計布線系統的傳輸速率在穩步加快的同時也帶來了某種防干擾的脆弱性,這是因為傳輸信息的頻率越高,信號的敏感性增加,同時它們的能量越來越弱,此時的布線系統就越容易受干擾。干擾無處不在,電纜

2019-07-17 18:55:38

高速PCB設計布線系統的傳輸速率在穩步加快的同時也帶來了某種防干擾的脆弱性,這是因為傳輸信息的頻率越高,信號的敏感性增加,同時它們的能量越來越弱,此時的布線系統就越容易受干擾。干擾無處不在,電纜

2016-09-14 11:03:51

高速PCB設計布線系統的傳輸速率在穩步加快的同時也帶來了某種防干擾的脆弱性,這是因為傳輸信息的頻率越高,信號的敏感性增加,同時它們的能量越來越弱,此時的布線系統就越容易受干擾。干擾無處不在,電纜

2016-09-21 10:25:21

解決高速PCB設計中的相互干擾問題。 我們知道,在多層PCB中高頻信號的回流路徑應該在該信號線層臨近的參考地平面(電源層或者地層)上,這樣的回流和阻抗最小,但是實際的地層或電源層中會有分割和鏤空,從而

2018-09-10 16:37:21

高速PCB設計中的電磁輻射檢測技術目前大部分硬件工程師還只是憑經驗來設計PCB,在調試過程中,很多需要觀測的信號線或者芯片引腳被埋在PCB中間層,無法使用示波器等工具去探測,如果產品不能通過功能測試

2013-10-28 14:39:24

高速PCB設計中的電磁輻射檢測技術,總結的太棒了

2021-04-25 07:38:23

電路應具備信號分析、傳輸線、模擬電路的知識。錯誤的概念:8kHz幀信號為低速信號。 問:在高速PCB設計中,經常需要用到自動布線功能,請問如何能卓有成效地實現自動布線? 答:在高速電路板中,不能只是看

2019-01-11 10:55:05

在PCB設計中,布線是完成產品設計的重要步驟,可以說前面的準備工作都是為它而做的, 在整個PCB中,以布線的設計過程限定最高,技巧最細、工作量最大。PCB布線有單面布線、 雙面布線及多層布線。布線

2012-08-13 16:30:47

和互連工具可以幫助設計師解決部分難題,但高速PCB設計也更需要經驗的不斷積累及業界間的深入交流。 >>焊盤對高速信號的影響 在PCB中,從設計的角度來看,一個過孔主要由兩部分組成:中間

2012-10-17 15:59:48

本期講解PCB設計中高速信號關鍵信號的布線要求。一、時鐘信號布線要求在數字電路設計中,時鐘信號是一種在高態與低態之間振蕩的信號,決定著電路的性能。時鐘電路在數字電路中點有重要地位,同時又是產生

2017-10-19 14:25:36

的設計要求,結合筆者設計經驗,按照PCB設計流程,對PCB設計中需要重點關注的設計原則進行了歸類。詳細闡述了PCB的疊層設計、元器件布局、接地、PCB布線等高速PCB設計中需要遵循的設計原則和設計方法以及需要注意的問題等。按照筆者所述方法設計的高速復雜數模混合電路,其地噪很低,電磁兼容性很好。

2012-03-31 14:29:39

規則一:高速信號走線屏蔽規則 在高速的PCB設計中,時鐘等關鍵的高速信號線,走線需要進行屏蔽處理,如果沒有屏蔽或只屏蔽了部分,都會造成EMI的泄漏。建議屏蔽線,每1000mil,打孔接地

2016-01-19 22:50:31

高速PCB設計指南之(一~八 )目錄2001/11/21CHENZHI/LEGENDSILICON一、1、PCB布線2、PCB布局3、高速PCB設計二、1、高密度(HD)電路設計2、抗干擾技術3

2012-07-13 16:18:40

;走線時高速信號盡量布線在內層和少打過孔也是一個矛盾。因此在設計中,需要綜合考慮各有利因素,做出全面的電路設計。 只有這樣才能設計出抗干擾能力強,性能穩定,實時性高的高質量PCB電路板。

2018-09-12 15:09:57

電容的合理配置、屏蔽等抑制電磁干擾(EMI)的措施都是很有效的,在工程實踐中被廣泛應用.1.高頻數字電路PCB的電磁兼容性(EMC)設計中的布線規則高頻數字信號線要用短線,一般小于2inch(5cm

2014-04-17 21:15:29

高速高密度多層PCB設計和布局布線技術

2012-08-12 10:47:09

EMC之PCB設計技巧

電磁兼容性(EMC)及關聯的電磁干擾(EMI)歷來都需要系統設計工程師擦亮眼睛,在當今電路板設計和元器件封裝不斷縮小、OEM要求更高速系統的情況下,這兩大問題尤其令PCB布局

2023-12-19 09:53:34

小竅門。下面是經過多年設計總結出來的,在PCB設計中降低噪聲與電磁干擾的24個竅門:(1) 能用低速芯片就不用高速的,高速芯片用在關鍵地方。(2) 可用串一個電阻的辦法,降低控制電路上下沿跳變速

2018-03-10 21:32:11

高頻電路往往集成度較高,布線密度大,采用多層板既是布線所必須,也是降低干擾的有效手段。在PCB Layout階段,合理的選擇一定層數的印制板尺寸,能充分利用中間層來設置屏蔽,更好地實現就近接地

2017-01-20 11:44:22

在PCB設計中,布線是完成產品設計的重要步驟,可以說前面的準備工作都是為它而做的。在整個PCB設計中,布線的設計過程限定最高,技巧最細,工作量最大。PCB布線分為單面布線,雙面布線以及多層布線3種

2018-12-07 22:50:21

` 在PCB設計中,布線是完成產品設計的重要步驟,可以說前面的準備工作都是為它而做的。在整個PCB設計中,布線的設計過程限定最高,技巧最細,工作量最大。PCB布線分為單面布線,雙面布線以及多層布線3

2018-11-23 16:07:58

將為初學者提供一些技術參考。 合理使用多層板進行PCB布線 在PCB板的實際設計過程中,大部分工程師都會選擇使用多層板來完成高速信號布線工作,多層板是降低電路干擾的有效手段。在利用多層板來完成PCB

2023-04-19 16:05:28

高速PCB設計中常規PCB布線,有以下基本要求:(1)QFP、SOP等封裝的矩形焊盤出線,應從PIN中心引出(一般采用鋪shape)(2)布線到板邊的距離不小于20MIL。(3)金屬外殼器件下

2017-01-23 16:04:35

高速PCB設計中常規PCB布線,有以下基本要求:(1)QFP、SOP等封裝的矩形焊盤出線,應從PIN中心引出(一般采用鋪shape)(2)布線到板邊的距離不小于20MIL。(3)金屬外殼器件下

2017-01-23 09:36:13

在pcb設計中FPGA與高速并行DAC的布線應該注意什么?

2023-04-11 17:30:54

絡,PCB中主要表現為地線噪聲和電源噪聲.輻射干擾是指信號以電磁波的形式輻射出去,從而影響到另一個電網絡.在高速PCB及系統設計中,高頻信號線、芯片的引腳、接插件等都可能成為具有天線特性的輻射干擾源

2018-11-22 16:03:30

絡,PCB中主要表現為地線噪聲和電源噪聲。輻射干擾是指信號以電磁波的形式輻射出去,從而影響到另一個電網絡。在高速PCB及系統設計中,高頻信號線、芯片的引腳、接插件等都可能成為具有天線特性的輻射干擾源

2018-09-12 15:16:15

本文主要講解PCB設計時要注意的地方,從而減低PCB板中的電磁干擾問題。

2021-03-18 06:03:17

在PCB設計中,電磁兼容性(EMC)及關聯的電磁干擾(EMI)歷來是讓工程師們頭疼的兩大問題,特別是在當今電路板設計和元器件封裝不斷縮小、OEM要求更高速系統的情況下。本文給大家分享如何在PCB設計中避免出現電磁問題。

2021-02-01 07:42:30

如何抑制電磁干擾PCB是産生電磁干擾(EMI)的源頭,所以PCB設計直接關系到電子産品的電磁兼容性(EMC)。 如果在高速PCB設計中對EMC/EMI予以重視,將有助縮短産品研發周期加快産品上市

2013-03-13 11:35:03

PCB是産生電磁干擾(EMI)的源頭,所以PCB設計直接關系到電子産品的電磁兼容性(EMC)。 如果在高速PCB設計中對EMC/EMI予以重視,將有助縮短産品研發周期加快産品上市時間。 EMC

2013-01-22 09:52:31

射頻電路PCB設計的關鍵在于如何減少輻射能力以及如何提高抗干擾能力,合理的布局與布線是設計時頻電路PCB的保證。文中所述方法有利于提高射頻電路PCB設計的可靠性,解決好電磁干擾問題,進而達到電磁兼容的目的。

2021-04-25 06:16:26

,噪聲干擾的產生是第一影響因素,高頻電路還會產生輻射和沖突,而較快的邊緣速率則會產生振鈴、反射和串擾。如果不考慮高速信號布局布線的特殊性,設計出的電路板將不能正常工作。因此PCB板的設計成功是DSPs

2017-12-04 14:19:43

電磁兼容性(EMC)及關聯的電磁干擾(EMI)歷來都需要系統設計工程師擦亮眼睛,在當今電路板設計和元器件封裝不斷縮小、OEM要求更高速系統的情況下,這兩大問題尤其令PCB布局和設計工程師頭痛。EMC

2022-06-07 15:46:10

如何防止和抑制電磁干擾,提高PCB的電磁兼容性 ?PCB設計流程是怎樣的?如何進行PCB布線 ?

2021-04-21 07:14:56

媒體把一 個電網絡上的信號干擾到另一電網絡。在高速系統設計中,集成電路引腳、高頻信號線和各類接插頭都是PCB板設計中常見的輻射干擾源,它們散發的電磁波就是 電磁干擾(EMI),自身和其他系統都會因此

2018-09-18 15:33:03

對于高速信號,pcb的設計要求會更多,因為高速信號很容易收到其他外在因素的干擾,導致實際設計出來的東西和原本預期的效果相差很多。 所以在高速信號pcb設計中,需要提前考慮好整體的布局布線,良好

2023-04-12 14:22:25

求大神分享PCB設計中的布線經驗

2021-04-23 06:42:17

深入了解PCB設計,并且合理利用。熱門PCB設計技術方案:PCB設計的核心與解決方案高速PCB中電源完整性的設計闡述DFM技術在PCB設計中的應用闡述高速DSP系統的電路板級電磁兼容性設計高速PCB

2014-12-16 13:55:37

高速PCB設計布線系統的傳輸速率在穩步加快的同時也帶來了某種防干擾的脆弱性,這是因為傳輸信息的頻率越高,信號的敏感性增加,同時它們的能量越來越弱,此時的布線系統就越容易受干擾。干擾無處不在,電纜

2016-01-06 16:43:09

的PCB設計中,時鐘等關鍵的高速信號線,走線需要進行屏蔽處理,如果沒有屏蔽或只屏蔽了部分,都會造成EMI的泄漏。建議屏蔽線,每1000mil,打孔接地。規則二:高速信號的走線閉環規則由于PCB板的密度越來越高

2017-11-02 12:11:12

高速PCB設計指南之(一~八 )目錄 2001/11/21 一、1、PCB布線2、PCB布局3、高速PCB設計

二、1、高密度(HD)電路設計2、抗干擾技術

2008-08-04 14:14:42 0

0 本文針對高速PCB板信號接地設計中存在接地噪聲及電磁輻射等問題,提出了高速PCB接地模型,并從PCB設計中布線策略的分析和去耦電容的使用等幾個方面討論了解決高速PCB板的接地噪聲

2009-12-08 14:53:23 63

63 高速PCB設計指南之一

第一篇 PCB布線在PCB設計中,布線是完成產品設計的重要步驟,可以說前面的準備工作都是為它而做

2009-11-11 14:57:48 600

600 高速PCB設計布線系統的傳輸速率在穩步加快的同時也帶來了某種防干擾的脆弱性,這是因為傳輸信息的頻率越高,信號的敏感性增加,同時它們的能量越來越弱,此時的布線系統就

2010-10-30 11:54:01 610

610 PCB設計,布線設計非常詳細,轉需

2017-02-28 15:09:14 0

0 高速PCB設計布線系統的傳輸速率在穩步加快的同時也帶來了某種防干擾的脆弱性,這是因為傳輸信息的頻率越高,信號的敏感性增加,同時它們的能量越來越弱,此時的布線系統就越容易受干擾。 干擾無處不在,電纜

2017-10-09 17:27:03 0

0 此高速pcb設計指南可以說是史上最全設計資料,詳細講解使用pcb-板設計高速系統的一般原則,包括:

電源分配系統及其對boardinghouse產生的影響

傳輸線極其相關設計準則

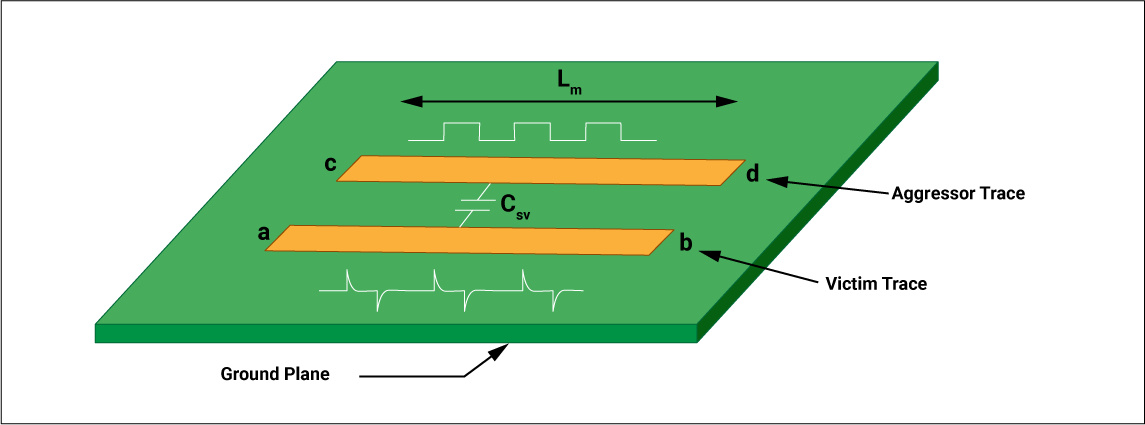

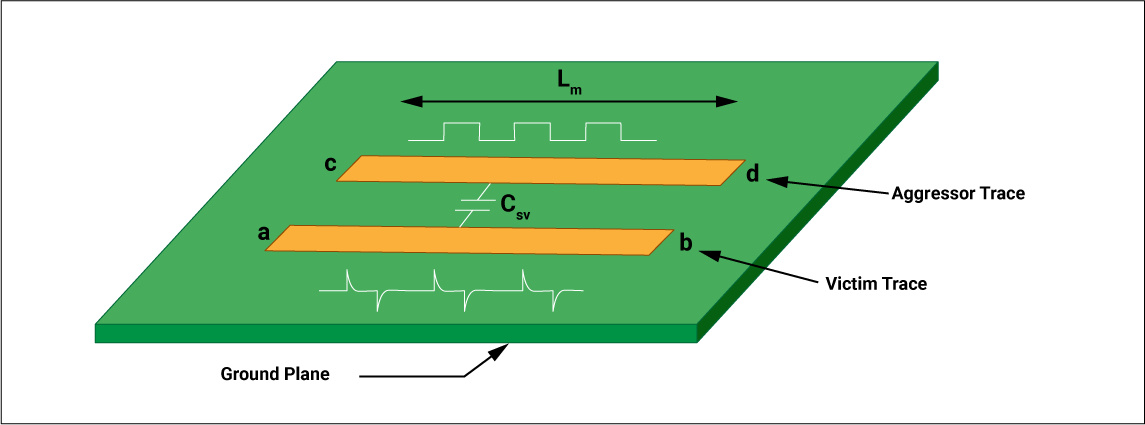

串擾(crosstalk)極其消除

電磁干擾

2017-11-07 13:43:28 0

0 綜合布線產品無論是非屏蔽系統還是屏蔽系統都有著廣泛的使用基礎,并可以針對不同用戶的不同需求(網絡的工作頻率和周圍的電磁環境的不同)提供各種端到端的解決方案,包括屏蔽、非屏蔽以及光纖布線解決方案。但在對抗干擾和保密性要求高(如政府機關、軍事設施)或下列電磁環境中,屏蔽系統將是非常適合的。

2018-07-23 10:30:00 3318

3318 高速PCB設計布線系統的傳輸速率在穩步加快的同時也帶來了某種防干擾的脆弱性,這是因為傳輸信息的頻率越高,信號的敏感性增加,同時它們的能量越來越弱,此時的布線系統就越容易受干擾。

2019-01-24 15:44:43 3354

3354 在高速的PCB設計中,時鐘等關鍵的高速信號線,走線需要進行屏蔽處理,如果沒有屏蔽或只屏蔽了部分,都會造成EMI的泄漏。建議屏蔽線,每1000mil,打孔接地。

2019-03-15 14:05:42 4494

4494

高速PCB設計布線系統的傳輸速率在穩步加快的同時也帶來了某種防干擾的脆弱性,這是因為傳輸信息的頻率越高,信號的敏感性增加,同時它們的能量越來越弱,此時的布線系統就越容易受干擾。

2020-02-27 17:19:32 718

718 高速PCB設計布線系統的傳輸速率在穩步加快的同時也帶來了某種防干擾的脆弱性,這是因為傳輸信息的頻率越高,信號的敏感性增加,同時它們的能量越來越弱,此時的布線系統就越容易受干擾。

2019-10-28 17:01:39 1924

1924 電磁干擾是由電磁效應而造成的干擾,由于PCB上的元器件及布線越來越密集,如果設計不當就會產生電磁干擾。

2019-08-22 11:06:37 680

680 在PCB設計中,電磁兼容性(EMC)及關聯的電磁干擾(EMI)歷來是讓工程師們頭疼的兩大問題,特別是在當今電路板設計和元器件封裝不斷縮小、OEM要求更高速系統的情況下。本文給大家分享如何在PCB設計中避免出現電磁問題。

2021-01-20 14:38:13 371

371 在PCB設計中,電磁兼容性(EMC)及關聯的電磁干擾(EMI)歷來是讓工程師們頭疼的兩大問題,特別是在當今電路板設計和元器件封裝不斷縮小、OEM要求更高速系統的情況下。本文給大家分享如何在PCB設計中避免出現電磁問題。

2021-01-22 09:54:18 20

20 在PCB設計中,經常出現電磁問題,如何有效避免呢,有以下七個小技巧。對于高頻信號,必須使用屏蔽電纜,其正面和背面均接地,消除EMI干擾。

2023-03-31 17:37:11 535

535

降低PCB設計中噪聲與電磁干擾24條

2023-07-04 16:57:23 327

327 一站式PCBA智造廠家今天為大家講講PCB設計差分布線有什么要求?PCB設計差分布線要求及操作技巧。高速串行總線的普及,使得PCB板上差分信號越來越多,那么,PCB設計如何進行差分布線呢?接下來

2023-07-07 09:25:21 3156

3156

可以很好的決定布線的走向和結構,電源與地之間的分割,以及電磁干擾和噪聲的控制。 不過在理解高速PCB設計前,需要知道什么是高速信號。 一般如果符合以下幾點,那它就可以被認為是高速信號(cadence公司做的定義): (1)頻率大于

2023-11-06 10:04:04 341

341

高速電路無疑是PCB設計中要求非常嚴苛的一部分,因為高速信號很容易被干擾,導致信號質量下降,所以在PCB設計的過程中就需要避免或降低這種情況的發生。 在具體的高速電路布局布線中,這些知識技能需要掌握

2023-11-06 15:14:06 263

263

電子發燒友App

電子發燒友App

評論