這才是學習FPGA的正確路徑

2016年06月07日 10:51 來源:網站整理 作者:春波綠影 我要評論(0)

學習FPGA,在不同層次的人明顯有不同的答案。先說一句,說不要開發版的都是菜鳥級選手。

我把FPGA層次劃分為,雞蛋級別,菜鳥級別,老鳥級別,高手級別四類。題主是雞蛋級別的吧!啥也不會。那些得贊高的不少都是菜鳥級別的選手。當然,我現在告訴你的如何成為一個菜鳥。當然以后有空我也會寫從菜鳥變成老鳥的方法。

1)熟悉語法,其實你不需要什么都會,但是要記住幾個經典的時序,邏輯電路的描述方式。

2)熟悉三個經典電路描述并仿真。仿真其實不是很重要,我開始學習壓根沒學那個玩意兒,因為要是只做接口那玩意兒沒啥用。直接用ChipSchop抓抓數據更快。仿真是給做算法,工程相對較大的人用的。三個經典電路分別是,分頻器,計數器(可做一個時鐘),序列檢測器。

這樣你就基本熟悉了開發環境了。

3)上板卡跑一個燈,熟悉一個板卡上時鐘資源使用,硬件的使用原理。

4)知道了FPGA學習主要不在于編程!壓根沒有編程這回事!!Verilog是硬件描述語言!描述!!寫代碼時腦子里必須有電路圖!!知道FPGA主要學的是硬件和算法!!軟件最多能占10%就不錯了!!

只要你能完成這上面的東西,恭喜你進入菜鳥行列,可以在別人設計好FPGA方案的條件下完成一些模塊的設計了。其實華為招聘員工,很多人FPGA水平一開始都差不多這么菜。

先寫一下老鳥需要會什么,以后再答怎么做到。

1)FPGA邏輯資源,特別是時鐘資源要非常熟悉。

2)做算法的必須熟悉sysgen的使用。說的容易了,sysgen畫畫圖也沒那么容易哦,你要熟悉使用各種濾波器,理論知識要求起點就不小。

3)充分理解FPGA從上而下的設計原則,能夠編寫中等程度的FPGA詳細設計方案。

4)熟悉時序優化,時序收斂,區域約束等知識。并且能運用到編程之中,解決菜鳥們解決不了的“不科學”的問題。說白了就是會使用planhead,以及ISE中那些你還沒接觸過的功能。一般菜鳥們ISE都只會編程,默認的編譯一下,然后下載,ChipSchop抓抓數看看。

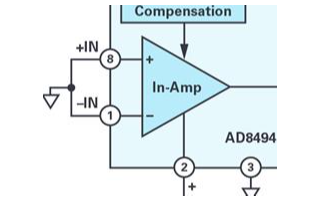

5)能夠熟悉FPGA常用的接口,不求都會編程,但是要知道他們功能是什么。比如ADC,DAC,串口,EMIF等等。并且熟悉DSP等FPGA周邊常用芯片工作原理。

6)熟悉硬件設計,至少要知道Bank上IO規劃怎么好,全局時鐘,區域時鐘大致怎么規劃等等。

等這些都熟悉了,差不多是老鳥了。

要成為高手,你沒有十來個FPGA程序設計經驗,解決過十來個中大項目核心問題,沒有做過大系統還是停留在小板卡,都是不行的。

發現入門沒那么容易。我覺得入門必須知道FPGA是做什么的,能做什么?和ARM,DSP,X86,GPU對比有啥優勢?

我下面簡單說說,FPGA現在有三個方面:

1)通信高速接口設計。一般速率太高了,需要用FPGA把高速數字信號分開,然后使信號容易處理,傳輸,存儲。3

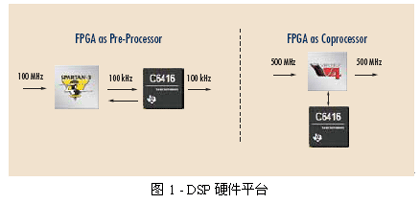

2)數字信號處理。包括圖像處理,雷達信號處理,醫學信號處理等。優勢是實時性好,用面積換速度,比CPU快的多。

3)SOPC。但是個人覺得這個方面不太主流。

基本上60%以上應用于做通信接口,也是FPGA最適合做,也是優勢最大的方面。30%做信號處理。其實很多情況做信號處理也是由于一個系統中已經需要一個做接口的FPGA,不想多花錢、費事在買個DSP而已!

以上各個芯片各有啥優勢請自己百度。

后記

聽到有人批評,其實我還是蠻高興的。有人說我水平是一個較高的菜鳥。確實嚴格來講沒有錯。仿真一直是我忽略的一個環節。我在這里承認自己說仿真不重要是不對的。仿真一般可以提高一個優秀的FPGA工程師的工作效率,一些低級的錯誤可以一下子反應出來。特別是不熟悉FPGA語法的人需要仿真。畢竟一個較大的FPGA程序需要編譯幾個小時。但是請大家合理的看待仿真這件事,菜鳥又要學編程又要學仿真。關鍵仿真正確后實際還不一定對!這樣會打擊信心。

在有條件的基礎上可以直接抓取信號看看波形,這樣比較準確。一下子可以讓你縮短做一個簡單工程的周期。菜鳥級別的工程一般直接寫出來也不怎么會錯的。所以在上面我說了仿真對于菜鳥不是很重要。各自還是看每個人處在的階段看問題吧!

一般從時間上來說一般1-2年能入門,就是我說的菜鳥水平沒有達到老鳥級別。3-5年算是一個老鳥級別吧!能不能到高手看個人造化。我學習FPGA目前是兩年左右,做過工程量大的項目2個,小項目記不清了,級別在菜鳥和老鳥之間。熟悉FPGA各個方面的工作,但不熟練。歡迎交流和高手們批評指正。

用戶評論

查看全部 條評論

查看全部 條評論>>