Cadence宣布業(yè)內(nèi)首個DDR4 Design IP解決方案在28納米級芯片上得到驗證

2012-09-10 09:53:24 1403

1403 楷登電子(NASDAQ:CDNS)今日宣布,發(fā)布增強型 Cadence? Voltus?IC 電源完整性解決方案,其面向先進工藝節(jié)點的電網(wǎng)簽核,其大規(guī)模并行(XP)算法選項采用了分布式處理技術。

2018-07-26 15:59:22 6977

6977 2022年6月28日,國微思爾芯面向全球客戶正式發(fā)布芯神瞳自動原型編譯軟件Player Pro-7(PPro-7)。新版本針對大規(guī)模芯片設計提供了有效的解決方案,擁有更高的編譯效率和更好的分割性能

2022-06-28 10:21:59 827

827

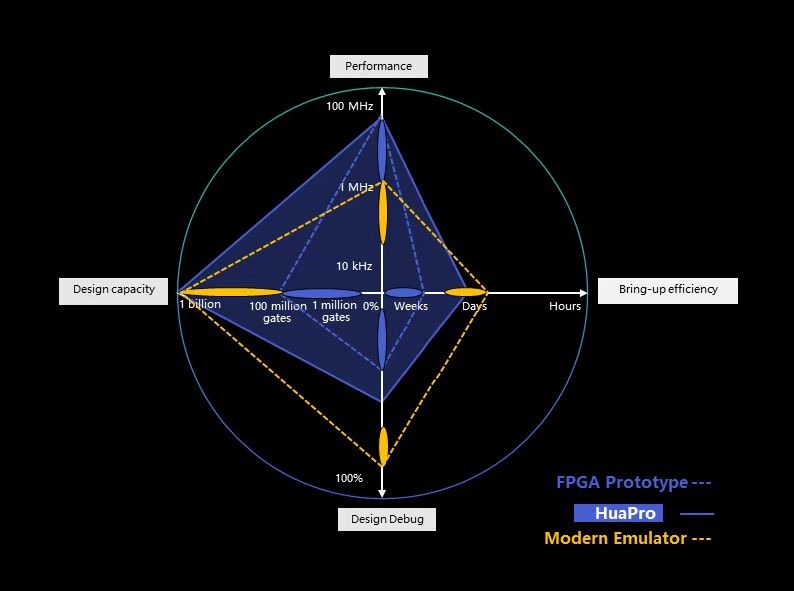

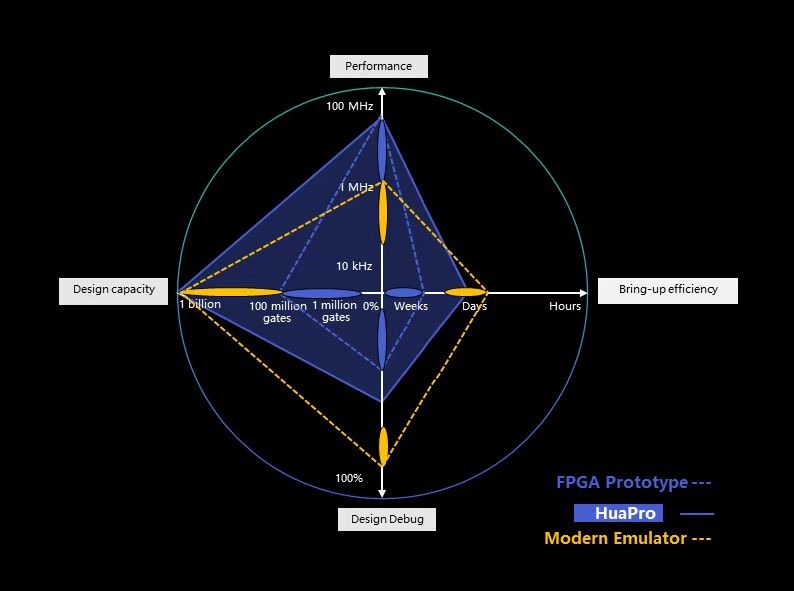

12月2日,芯華章生態(tài)及產(chǎn)品發(fā)布會在上海成功舉辦。作為國內(nèi)領先的系統(tǒng)級驗證EDA解決方案提供商,芯華章正式發(fā)布高性能FPGA雙模驗證系統(tǒng)樺捷HuaPro P2E,以獨特的雙模式滿足系統(tǒng)調(diào)試和軟件開發(fā)

2022-12-02 17:01:44 1117

1117

限制,以及一些現(xiàn)有通信系統(tǒng)中存在的挑戰(zhàn),諸如網(wǎng)絡的可靠性、覆蓋率、能效性、和延遲性等。大規(guī)模MIMO作為5G技術的一種實現(xiàn)方案,通過在基站收發(fā)信機(BTS)上使用大量的天線(超過64根)實現(xiàn)了更大的無線

2014-12-24 14:13:12

其測試方案。最后分析了國內(nèi)毫米波終端可能的商用計劃。【關鍵詞】毫米波終端,大規(guī)模天線技術,空中下載技術

2019-07-18 08:04:55

的數(shù)據(jù)庫架構,使用模型和庫為Cadence OrCAD和Allegro產(chǎn)品線提供完全可升級的PCB解決方案,加速你的設計速度并擴大設計規(guī)模,從而提高了設計效率,縮短了設計周期,以及更快地實現(xiàn)

2018-08-30 10:49:16

平臺是更廣泛的 Cadence 3D-IC 解決方案組合的一部分,該組合超越了數(shù)字,包括系統(tǒng)和驗證以及I??P 功能。更廣泛的解決方案通過由 Palladium? Z2 和 Protium? X2

2021-10-14 11:19:57

Cadence設計系統(tǒng)有限公司宣布推出業(yè)界第一套完整的能夠推動SiPIC設計主流化的EDA產(chǎn)品。Cadence解決方案針對目前SiP設計中依賴‘專家工程’的方式存在的固有局限性,提供了一套自動化

2008-06-27 10:24:12

大規(guī)模FPGA設計中的多點綜合技術

2012-08-17 10:27:46

IEEE Transactions on Information Forensics and Security上的一篇論文探討了這種類型的攻擊。他們發(fā)現(xiàn),在某些情況下,當使用大規(guī)模多入多出技術

2019-06-18 07:54:32

軌跡產(chǎn)生的容量斜坡仍然比需求線平坦。面對此挑戰(zhàn),3GPP 標準實體近來提出了數(shù)據(jù)容量“到2020 年增長1000 倍”的目標,以滿足演進性或革命性創(chuàng)意的需要。這種概念要求基站部署極大規(guī)模的天線陣

2019-07-17 07:54:10

大規(guī)模區(qū)域監(jiān)控與通信系統(tǒng)的SOPC芯片組,看完你就懂了

2021-05-26 06:46:11

作為提升5G系統(tǒng)頻譜效率最直觀的物理層技術之一,大規(guī)模天線技術自問世以來,受到了來自學術界、工業(yè)界的廣泛關注。樣機測試為了克服信道信息獲取困難、解決導頻污染、以及計算復雜度大幅提升等問題,測試驗證

2019-06-13 07:49:29

解讀5G通信的殺手锏大規(guī)模天線陣列

2021-01-06 07:11:35

信息系統(tǒng)處理的共同點如下:1、處理種類不多,且多系固定的、復用的;2、要求實時性;3、是決定信息質(zhì)量的因素之一 考慮到這些條件,設備結構則以硬件控制為宜,因此,需要邏輯運算和存儲器用的大規(guī)模

2014-09-11 11:27:25

是Mailbox的工作方式。 TDA4VM的IPC方案,基于Mailbox的實現(xiàn)的方式的不同,常用的核間通信方式有兩種。 基于RPMSG的核間通信解決方案,適合小塊數(shù)據(jù)消息傳遞。基于Share Memory

2022-11-03 07:26:19

功率處理能力,一直是首選解決方案。然而,在大規(guī)模MIMO系統(tǒng)的設計中,它們需要高偏置電壓以施加反向偏置(用于提供隔離)和高電流以施加正向偏置(用于實現(xiàn)低插入損耗),這就變成了缺點。圖3示出了一款用于

2021-05-19 09:33:41

高級數(shù)字成像解決方案供應商OmniVision發(fā)布的最新 AutoVision 成像解決方案可滿足汽車業(yè)對輔助駕駛系統(tǒng)應用(如倒車攝像頭和后視鏡死角監(jiān)視系統(tǒng))更高成像效果的要求。1/4 英寸的超小巧 OV7960 和 OV7962 型號可提供優(yōu)異的低光性能 (

2019-08-16 06:37:42

結合Altera公司推出的Nios II嵌入式軟核處理器,提出一種具有常規(guī)DSP處理器功能的NiosII系統(tǒng)SOPC解決方案;利用NiosII可自定叉指令的特點。

2019-09-26 08:31:16

隨著現(xiàn)代集成電路技術的發(fā)展,尤其是IP的大量使用,芯片的規(guī)模越來越大,系統(tǒng)功能越來越復雜,普通的EDA和FPGA仿真在速度和性能上已經(jīng)無法勝任芯片仿真驗證的要求,功能驗證已經(jīng)成為大規(guī)模芯片設計的一個

2010-05-28 13:41:35

Voltus-Fi 定制型電源完整性解決方案采用Spectre加速并行仿真器APS進行SPICE級仿真,提供一流的晶體管級EMIR精度。完善了Cadence的電源簽收解決方案。本方案具備晶體管級的電

2018-09-30 16:11:32

挑戰(zhàn)海嘯模擬將物理過程模擬與大量深海數(shù)據(jù)相結合。這些計算通常在大規(guī)模并行超級計算機上完成,但具有硬件利用率低和性能差的缺陷。解決方案通過硬件浮點 FPGA 加速模擬內(nèi)循環(huán)可實現(xiàn)高達 383

2018-07-27 15:04:13

些功能原本是用簡單C語言在處理器或DSP中實現(xiàn)的。人們希望能夠找到一種方法,在更高的層次下設計更復雜,更高速的系統(tǒng),并希望將軟件設計和硬件設計統(tǒng)一到一個平臺下。解決方案C/C++語言是軟件工程師在開發(fā)商

2015-01-13 16:34:40

期,產(chǎn)品形態(tài)和方案等各有不同。本文作者根據(jù)多年的研究成果,提出一種工作于Sub-6G的5G大規(guī)模天線的系統(tǒng)架構,并對其各系統(tǒng)組成部分進行介紹。

2019-07-16 08:12:54

什么是WiMAX物理層信號測試解決方案?有什么作用?

2019-08-08 08:04:19

本文提出了一種基于FPGA的適合大規(guī)模數(shù)字信號處理的并行處理結構。

2021-04-30 07:16:52

頂替枯大規(guī)模奪頂替頂替

2018-01-05 18:50:55

回收Agilent/Keysight86115D大規(guī)模/并行光收發(fā)信機測試模塊全國長期回收Agilent/Keysight86115D收購大規(guī)模/并行光收發(fā)信機測試模塊聯(lián)系人:陳先生:***《微信

2020-08-21 11:06:14

ADI公司提供基于單硅芯片的電池化成控制系統(tǒng)綜合解決方案 AD8452。憑借準確的化成工藝性能,可優(yōu)化每個電池的化成時間。高效的能量回收特性能夠明顯節(jié)省大規(guī)模電池制造的能耗。

2021-01-21 06:27:38

如何去推進FTTH大規(guī)模建設?影響FTTH大規(guī)模建設的原因有哪些?

2021-05-27 06:58:13

描述此 TI 驗證設計采用各種運算放大器,以絕緣電阻驅(qū)動 100pF 至 1uF 的電容負載。OPA192 的亮點在于其能夠以小型絕緣電阻驅(qū)動大規(guī)模電容負載。主要特色電源電壓:30 V (+/-15

2018-11-15 11:40:22

大規(guī)模電動汽車生產(chǎn)需要先進的電池化成和測試系統(tǒng)

2021-01-27 06:59:50

如何去設計一款合理的電子硬件解決方案,從而實現(xiàn)經(jīng)濟有效的大規(guī)模生產(chǎn)與部署?怎樣去驗證可部署目標硬件與軟件算法模型之間的算法性能一致性?System Generator是什么?有什么功能?

2021-04-08 06:25:48

的運算,實現(xiàn)物理時間和仿真時間的同步更新。第二是大規(guī)模,即整個系統(tǒng)在各部分各個時間尺度上都能覆蓋,而不是被簡化。在此要求下,必須對系統(tǒng)進行劃分,對每一個劃分出來的小型子系統(tǒng)采用多核處理器進行并行計算仿真

2016-12-03 20:42:42

的巨大投資將刺激變配電解決方案市場的進一步發(fā)展。從電力市場智能電網(wǎng)變配電變配電解決方案這四者的關系圖中可以看出,變配電解決方案市場與智能電網(wǎng)存在著較大的交集,這也意味著國家電網(wǎng)對智能電網(wǎng)產(chǎn)業(yè)的大規(guī)模投資

2012-12-12 15:13:29

構建大規(guī)模MIMO的難點在哪?高功率硅開關的應用案列分析

2021-03-11 07:05:03

我要如何發(fā)布我的HarmonyOS組件或解決方案?

2022-06-02 15:55:36

請教大神如何去管理大規(guī)模數(shù)據(jù)?

2021-05-11 06:56:54

大規(guī)模MIMO的原型怎么制作?

2021-05-24 06:25:09

輪胎壓力監(jiān)測(TPM)系統(tǒng)有望獲得大規(guī)模應用。

2021-05-12 06:02:56

大規(guī)模問題,HOBBIES軟件的千核規(guī)模電磁并行計算效率達到90%。2) 高效的核外求解技術:對于艦船、飛機編隊等大型電磁目標,其電磁特性計算量很大,任務不可能在內(nèi)存完成,HOBBIES核外求解技術

2019-06-27 07:47:44

基于基因電腦克隆軟件SiClone 和可變剪接分析軟件AltSplice 的并行優(yōu)化工作,提出一種基于大規(guī)模序列比對軟件的并行優(yōu)化方案。該方案對所要進行比對分析的大規(guī)模序列庫按某種策

2009-03-29 09:43:40 17

17 摘要:在使用傳統(tǒng)的動態(tài)仿真方法對通用微處理器這樣大規(guī)模的設計進行功能驗證時仿真速度成為了瓶頸,而使用FPGA物理原型驗證又不能提供很好的可調(diào)試性。本文主要介紹了基于

2010-06-07 11:20:54 0

0 服務范圍大規(guī)模集成電路芯片檢測標準●JESD22-A103/ A104/ A105/ A108/ A110●J-STD-020●JS-001/002●JESD78檢測項目(1)芯片級可靠性驗證試驗

2024-03-14 16:28:30

能源公司采用McDATA大規(guī)模IT整合解決方案

權威的多功能存儲網(wǎng)絡解決方案供應商McDATA公司宣布,在PPL公司實施了一套基于McDATA的IT整合和數(shù)據(jù)保護解決

2009-07-06 08:51:30 456

456 Cadence推出首個TLM驅(qū)動式設計與驗證解決方案

Cadence設計系統(tǒng)公司今天推出首個TLM驅(qū)動式協(xié)同設計與驗證解決方案和方法學,使SoC設計師們可以盡享事務級建模(TLM)的好處。

2009-08-07 07:32:00 674

674 Cadence推出首個TLM驅(qū)動式設計與驗證解決方案提升基于RTL流程的開發(fā)效率

Cadence設計系統(tǒng)公司推出首個TLM驅(qū)動式協(xié)同設計與驗證解決方案和方法學,使SoC設計師們可以盡

2009-08-11 09:12:18 499

499 Cadence 模型化的 Litho Physical 和 Litho Electrical AnalyzerLitho Physical 與 Litho Electrical Analyzer 解決方案提供了快速、精確硅認證的全芯片電氣 DFM 驗證流程

2009-10-20 09:54:02 990

990 Cadence為PCI Express 3.0推出首款驗證解決方案

Cadence設計系統(tǒng)公司宣布其已經(jīng)開發(fā)了基于開放驗證方法學(OVM)的驗證IP(VIP)幫助開發(fā)者應用最新的PCI Express Base Specification

2009-11-04 16:59:59 1142

1142 海思半導體大規(guī)模采用SpringSoft的驗證與定制設計解決方案

在高效能ASIC設計流程中部署Verdi自動偵錯、Siloti能見度自動增強科技以及Lak

2010-03-17 16:45:20 893

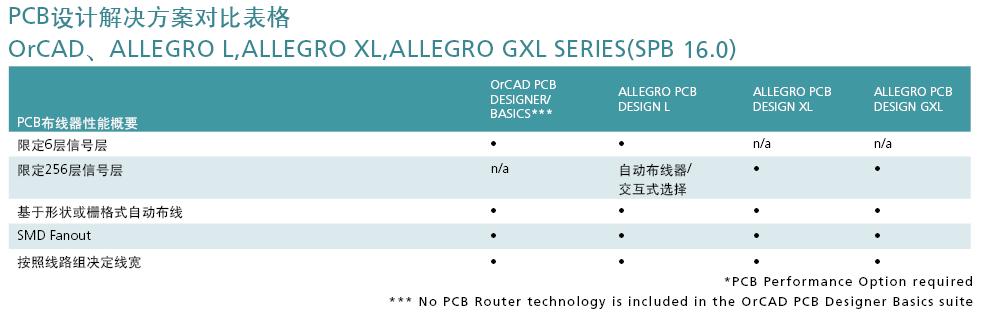

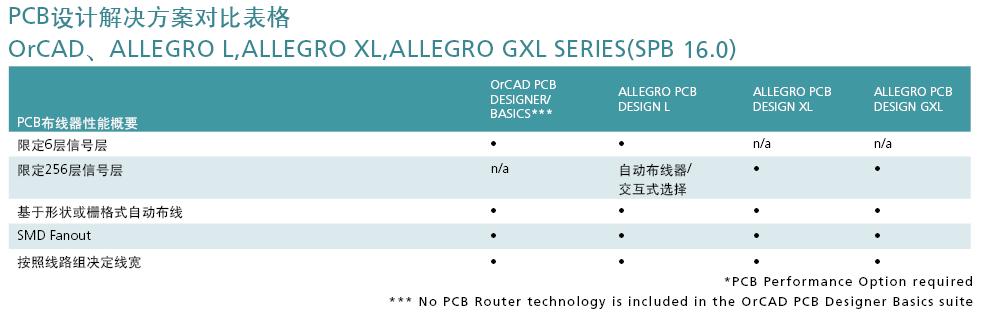

893 CADENCE PCB設計技術方案

CADENCE PCB設計解決方案能為解決與實現(xiàn)高難度的與制造密切相關的設計提供完整的設計環(huán)境,該設計解決方案集成了從設計構

2010-04-29 08:53:19 3756

3756

電子發(fā)燒友網(wǎng)核心提示 :全球電子設計創(chuàng)新領先企業(yè)Cadence設計系統(tǒng)公司于日前發(fā)布了具有一系列新功能的Cadence OrCAD 16.6 PCB設計解決方案,用戶定制功能增強,模擬性能提高20%, 使用戶

2012-10-16 08:44:25 1192

1192 全球電子設計創(chuàng)新領先企業(yè)Cadence設計系統(tǒng)公司日前宣布TSMC已選擇Cadence解決方案作為其20納米的設計架構。Cadence解決方案包括Virtuoso定制/模擬以及Encounter RTL-to-Signoff平臺。

2012-10-22 16:48:03 909

909 電子設計創(chuàng)新企業(yè)Cadence設計系統(tǒng)公司,今天宣布使用ARM AMBA協(xié)議類型的Cadence驗證IP(VIP)實現(xiàn)多個成功驗證項目,這是業(yè)界最廣泛使用的AMBA協(xié)議系列驗證解決方案之一。頂尖客戶,包括

2012-11-07 08:21:52 997

997 光刻物理分析器成功完成20納米系統(tǒng)級芯片(SoC)測試芯片流片。雙方工程師通過緊密合作,運用Cadence解決方案克服實施和可制造性設計(DFM)驗證挑戰(zhàn),并最終完成設計。

2013-07-09 15:53:24 769

769 Workbench搭配Cadence Interconnect Validator,組成了一套完整的功能驗證與性能檢驗解決方案。

2013-11-07 09:34:14 1130

1130 日益增長的驗證復雜性正推動著包括形式分析的多種互補驗證方法的需求,而 Jasper是快速增長形式分析行業(yè)的領導者,目標針對各種復雜驗證的挑戰(zhàn),Cadence與Jasper的結合將擴大產(chǎn)業(yè)最強與最廣泛的系統(tǒng)驗證產(chǎn)品的差異性優(yōu)勢。

2014-04-25 18:32:48 2326

2326 全球知名電子設計創(chuàng)新領先公司Cadence設計系統(tǒng)公司 (NASDAQ: CDNS),今日宣布臺積電采用了Cadence?16納米FinFET單元庫特性分析解決方案。

2014-10-08 19:03:22 1594

1594 2017年3月1日,上海——楷登電子(美國 Cadence 公司,NASDAQ: CDNS)今日發(fā)布業(yè)界首款已通過產(chǎn)品流片的第三代并行仿真平臺Xcelium? 。基于多核并行運算技術,Xcelium

2017-03-01 15:57:05 3341

3341 此方案可簡化,無電纜的設計分割,最多允許四個用戶同時使用。S2C公司,業(yè)內(nèi)領先的 FPGA 快速原型驗證系統(tǒng)供應商,發(fā)布了適用于超大規(guī)模設計的基于賽靈思Virtex UltraScale(VU

2018-06-29 08:09:00 4932

4932 該解決方案一舉解決了線上大規(guī)模部署物聯(lián)網(wǎng)以及安全管理設備和數(shù)據(jù)的關鍵問題。

2017-10-12 09:53:46 5155

5155 Cadence Palladium Verification Computing Platform是全集成、高性能的超大規(guī)模集成電路功能仿真驗證系統(tǒng)平臺。這種高度可擴展的集成電路功能仿真驗證硬件平臺

2018-11-06 11:37:36 4131

4131 RS CMW100 通信制造測試裝置 針對大規(guī)模生產(chǎn)、無線測試、5G NR的全新解決方案,是通用非信令測試套件,可用于6 GHz以下的5G NR測試。 主要特點:- 連續(xù)頻率范圍(最高達 6 GHz) - 多技術解決方案 - 可在最多八個射頻端口上并行測試 - 高測量性能

2020-04-13 11:47:00 2165

2165 FACE-VUP:大規(guī)模FPGA原型驗證平臺 FACE-VUP大規(guī)模FPGA原型驗證平臺是FACE系列的最新產(chǎn)品。FACE-VUP同時搭載16nm工藝的Virtex UltraScale+系列主器件

2020-05-19 10:50:05 2521

2521 ,加速超大規(guī)模設計驗證,提升設計性能 完整的原型驗證解決方案包括多FPGA深度調(diào)試,系統(tǒng)級協(xié)同建模及 90 多種應用接口子板庫 2020年10月22日,國微思爾芯,一站式EDA驗證解決方案專家,正式推出面向超大規(guī)模SoC原型市場的ProdigyTM S7-19P原型驗證系統(tǒng)。 S7-19P提供單、

2020-10-23 15:02:18 2374

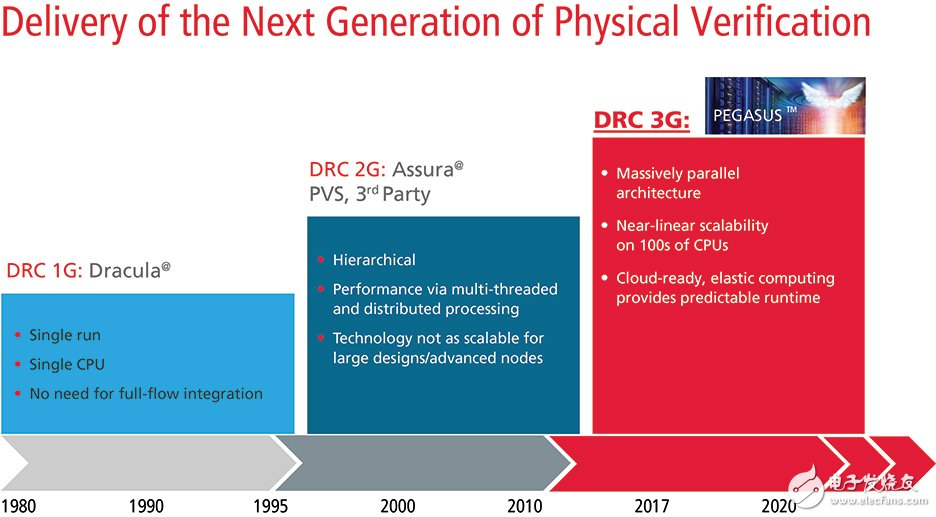

2374 新思科技(Synopsys)近日宣布推出最新版本IC Validator物理驗證解決方案,該解決方案包含多項創(chuàng)新技術,可加快前沿應用推向市場的時間。IC Validator獨特的彈性CPU調(diào)配技術

2020-11-24 14:42:52 2306

2306 的影響不超過 10%。 Cadence 與 GF 的合作讓采用 GF 12LP 和 12LP+ 解決方案的簽核工程師可以加速芯片設計和生產(chǎn),為 AI、數(shù)據(jù)中心、超大規(guī)模、航空航天和工業(yè)市場開發(fā)產(chǎn)品。 中國上海

2021-03-30 15:42:47 1371

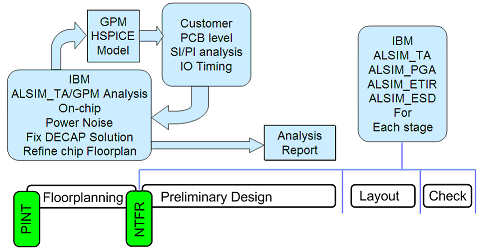

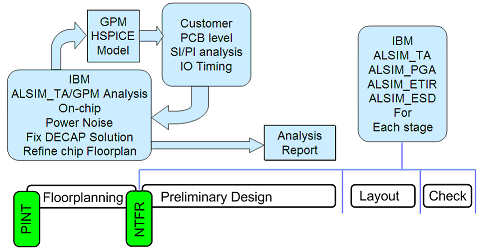

1371 針對超深亞微米工藝下超大規(guī)模通信集成電路所面臨的物理設計難點,IBM提出了相應的解決方案,具體介紹如下。

2021-06-21 11:01:46 3152

3152

的演示。是德科技提供先進的設計和驗證解決方案,旨在加速創(chuàng)新,創(chuàng)造一個安全互聯(lián)的世界。? 高速以太網(wǎng)生態(tài)系統(tǒng)中的網(wǎng)絡設備制造商(NEM)正在努力滿足超大規(guī)模數(shù)據(jù)中心對更快速度、更高流量密度的要求。為應對高速網(wǎng)絡解決方案的功耗和性能需求,QSFP-DD 多源協(xié)議

2021-06-23 14:40:38 1540

1540 Cadence Safety Solution 包括新的 Midas Safety Platform,為模擬和數(shù)字流程提供基于 FMEDA 功能安全設計和驗證的統(tǒng)一方案 該安全流程方案為汽車、工業(yè)

2021-10-26 14:24:34 4050

4050 Liberate Characterization 和 Tempus 解決方案已經(jīng)通過 Samsung Foundry 老化模型驗證,使客戶能夠快速、安心地完成高可靠性的設計簽核 Tempus 解決方案的全新

2021-11-19 11:00:13 2967

2967 隨著SoC設計規(guī)模呈指數(shù)級增長,芯片設計團隊原型驗證需求也變的越來越復雜。單通過增加系統(tǒng)容量的方式,還是會遇到諸多困難和挑戰(zhàn)。設計團隊需要有一個成熟的面向大規(guī)模SoC設計的高密原型驗證系統(tǒng)的軟硬件通用解決方案,來解決關鍵困難點的突破,降低項目風險。

2021-12-08 10:54:32 1657

1657 Cadence Conformal ECO Designer 使用形式驗證引擎提供經(jīng)過硅驗證的自動化 ECO 解決方案。它利用 Cadence 的物理邏輯綜合技術來映射和優(yōu)化 ECO 邏輯,從而支持考慮時序和擁塞的 pre-mask 和 post-mask 流程。

2022-04-12 09:59:49 912

912 楷登電子(美國 Cadence 公司,NASDAQ:CDNS)今日宣布推出 15 種新的驗證 IP(VIP)解決方案,助力工程師迅速有效地驗證設計,以滿足最新標準協(xié)議的要求。

2022-06-06 11:18:21 2665

2665 這一解決方案可實現(xiàn)對千億門超大規(guī)模集成電路的仿真驗證,更具備比傳統(tǒng)仿真器速度更高的性能,能夠3小時完成原本需要7天的仿真驗證任務。

2022-09-26 09:25:25 539

539 近日,芯華章科技宣布對高性能仿真軟件領先企業(yè)瞬曜電子進行核心技術整合,將超大規(guī)模軟件仿真技術融入芯華章智V驗證平臺,以增強其豐富的系統(tǒng)級驗證產(chǎn)品組合,鞏固芯華章敏捷驗證方案。同時,傅勇正式加盟芯華章

2022-09-26 10:03:15 274

274 Wi-SUN協(xié)議在遠程sub-GHz頻段提供基于標準的大規(guī)模網(wǎng)狀網(wǎng)絡解決方案,這是現(xiàn)有網(wǎng)狀網(wǎng)絡物聯(lián)網(wǎng)標準無法實現(xiàn)的。

2022-11-01 11:30:04 920

920 楷登電子(美國 Cadence 公司,NASDAQ:CDNS)近日宣布擴大與臺積電和微軟的合作,致力于加快千兆級規(guī)模數(shù)字設計的物理驗證。通過此次最新合作,客戶可以在帶有 Cadence

2023-04-26 18:05:45 710

710 日前,芯華章應邀參與國際電子媒體ASPENCORE舉辦的《高性能計算的AI設計挑戰(zhàn)及解決方案》線上直播論壇,與車載智能芯片平臺供應商芯礪智能一道,以汽車電子為例,圍繞系統(tǒng)級大規(guī)模芯片設計面臨的挑戰(zhàn)及驗證難題,進行深入交流和討論,吸引近500名集成電路相關從業(yè)者線上觀看。

2023-05-25 15:05:52 581

581 NEWS2022/6/282022年6月28日,國微思爾芯面向全球客戶正式發(fā)布芯神瞳自動原型編譯軟件PlayerPro-7(PPro-7)。新版本針對大規(guī)模芯片設計提供了有效的解決方案,擁有更高

2022-07-02 10:58:24 275

275

在 GPU 上使用大規(guī)模并行哈希圖實現(xiàn)性能最大化

2023-07-05 16:30:35 716

716

DAC 2023 7月12日,在一年一度的全球電子設計自動化盛會DAC 2023 上,面向來自世界各地的頂級EDA公司和芯片、系統(tǒng)廠商,國內(nèi)領先的系統(tǒng)級驗證EDA解決方案提供商芯華章,隆重推出

2023-07-12 09:28:55 108

108 解決方案,并與技術專家們面對面直接溝通交流。Cadence 期待您的參與! Cadence 將在 北京 、 成都 、 西安 開展線下研討會,您可以自由選擇您所在城市或就近城市報名參加 系統(tǒng)驗證及 IC

2023-09-21 17:20:02 339

339

平臺以獨特的方式將系統(tǒng)規(guī)劃、實現(xiàn)和系統(tǒng)層級分析整合成為一個解決方案,實現(xiàn)無縫的原型驗證 ●? 共同客戶可為其 AI、移動、5G、超大規(guī)模計算和物聯(lián)網(wǎng) 3D-IC 設計進行系統(tǒng)原型建模,加快

2023-10-08 15:55:01 249

249 電子設計自動化領域領先的供應商 Cadence,誠邀您參加“2023 Cadence 中國技術巡回研討會”。會議將集聚 Cadence 的開發(fā)者與資深技術專家,與您分享系統(tǒng)驗證及 IC 驗證解決方案

2023-10-23 11:55:02 287

287

電子設計自動化領域領先的供應商 Cadence,誠邀您參加“2023 Cadence 中國技術巡回研討會”。會議將集聚 Cadence 的開發(fā)者與資深技術專家,與您分享系統(tǒng)驗證及 IC 驗證解決方案

2023-10-25 10:40:02 190

190

●CelsiusStudio采用大規(guī)模并行架構,與之前的解決方案相比,性能快10倍●CelsiusStudio與Cadence芯片、封裝、PCB和微波設計平臺無縫集

2024-02-19 13:00:09 215

215

電子發(fā)燒友App

電子發(fā)燒友App

評論