講解xilinx FPGA 使用mig IP對DDR3的讀寫控制,旨在讓大家更快的學習和應用DDR3。 本實驗和工程基于Digilent的Arty Artix-35T FPGA開發板完成。 軟件

2020-12-16 15:47:59 1693

1693

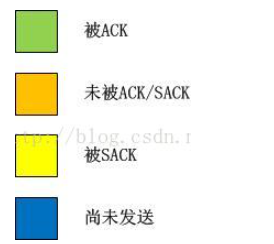

我一向覺得TCP擁塞控制算法太過復雜,而復雜的東西基本上就是用來裝逼的垃圾,直到遇到了bbr。

2020-11-06 09:26:07 2484

2484

在win8.1 pc上使用Vivado 2014.1,MIG IP生成器在啟動時收到Windows錯誤。相同的安裝文件已加載到win7 pc上,MIG IP生成器運行正常。在Win8.1機器上,我

2018-12-07 11:18:46

MIG-250焊機圖.pdf

2014-02-28 12:40:22

請幫忙。我通過MIG 2.3生成兩個內存控制器。在合成報告中合成后,已經寫了:粘合IOB的數量:560中的864 154%如何避免它?我使用Virtex-5和兩個UDIMM。

2020-06-02 16:28:46

求助大神!!!FPGA對于DDR3讀寫,FPGA是virtex6系列配置MIG IP 核時,需要管腳分配1.原理圖上dm是直接接地,管腳分配那里該怎么辦2.系統時鐘之類的管腳分配,是需要在原理圖上找FPGA與DDR3之間的連線嗎?還是?

2018-03-16 18:45:10

最近阿威也在玩MIG ,然后對我問了一大堆問題,主要針對MIG的時鐘。后來發現自己理解得還是不夠。這么一討論更加清晰了,做個筆記吧。第一個時鐘,也就是MIG 對DDR接口的時鐘。因為我用的是ddr3

2019-05-21 07:21:10

TCP-2-10+

2023-03-28 13:15:03

TCP-2-10-75+

2023-03-29 21:36:21

TCP-2-10-75X+

2023-03-29 21:36:21

TCP-2-10X+

2023-03-29 21:36:21

TCP-2-33X+

2023-03-29 21:44:56

TCP-5027UB-DT

2023-03-29 22:34:34

TCP-5082UA-DT

2023-03-28 18:08:52

請教各位大神,小弟剛學FPGA,現在在用spartan-3E的板子,想用上面的DDR SDRAM進行簡單的讀寫,用MIG生成DDR核之后出現了很多引腳,看了一些資料也不是很清楚,不知道怎么使用生成的這個IP核控制器來進行讀寫,希望大神們稍作指點

2013-06-20 20:43:56

課題要求是用光電傳感器控制ccd拍照我的想法是用光電開關(內含光電傳感器)直接接24V繼電器繼電器開關串另外一個直流穩壓5V電源電路控制CCD,是否可行?或者有什么其他的方法希望大家指導一下

2013-05-08 10:34:01

咖啡機光電式水位控制 的電路圖。

2018-11-19 21:29:13

LT1084MIG-XX - 5 AMP POSITIVE VOLTAGE REGULATOR - Seme LAB

2022-11-04 17:22:44

大家好, 當我使用ML605 DDR3 MIG參考設計ml605_MIG_rdf0011_12.4時,它會在下面顯示以下錯誤消息列表

2019-08-23 12:50:49

USR-TCP232-T2

2023-03-29 21:54:57

X76F101MIG-3.0 - Secure SerialFlash - IC MICROSYSTEMS

2022-11-04 17:22:44

嗨,大家好 我正在使用XUPV5 Virtex 5板,最近當我使用MIG創建DDR2內存控制器時,我意識到MIG創建的UCF文件與用戶手冊(我使用ML505的手冊)不同,因為差分時鐘的引腳根據

2019-08-21 10:24:03

有人用Xilinx ISE的mig生成ddr2,然后進行調試的嗎?如果選擇了內含pll,頂層時鐘怎么連接

2014-09-15 19:14:41

在DDR2 MIG的使用時,想把DDR2封裝成一個FIFO使用,但是有些問題不是太明白。在MIG的User Interface接口中,提供給控制器的數據是上升沿和下降沿的拼接,一個周期提供兩個數據到

2015-03-29 18:41:43

振蕩器和StateMachine的捕獲來控制MIG,我使用的是LX9 Microboard。D0信號是我的狀態機控制MIG的啟用信號D1信號是StateMachine(WAIT)的返回D2是cmd_en

2019-07-23 14:46:25

里的例子,ddr正常。但實際是要使用user design文件夾下的.v文件,此時如果編寫頂層讀寫控制程序對mig-39-2.v進行例化,應如何操作才能使用sim_tb_top.v仿真文件,(直接編寫一個

2018-06-22 17:14:40

本帖最后由 elecfans跑堂 于 2015-9-14 09:21 編輯

最近在做FPGA板子用了兩片16位的FPGA,在MIG中發現ODT 和CK CS等信號需要分別連接到FPGA。如下圖,是我在MIG中設置的問題嗎?還是xilinx DDR2 MIG就要求這么做?

2015-09-13 14:21:32

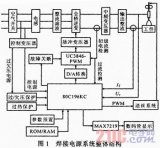

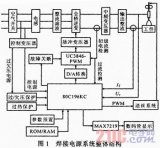

1. 文章研究主要問題雙弧脈沖 MIG 焊是一種低能量輸入焊接方法, 其原有的雙電源供電系統結構復雜、協同控制困難、易受干擾。2. 結論提出了雙弧脈沖 MIG 焊一體化專用電源的設計方案, 主弧和旁

2021-11-16 09:20:25

我可以使用mig生成ddr控制器(xc6vlx130t)嗎?mig向導只支持ddr2和ddr3!

2020-06-12 07:32:48

如何使用MIG?我閱讀了手冊,但仍然有點困惑如何使用它來做到這一點。通過寫一些地址并閱讀一些地址并在地址上放置與地址相對應的指示燈來計劃做一些較小的事情。

2020-08-04 10:51:22

該軟件的版本是MIG2.1,ISE10.1.01。 FPGA是XC5VLX110T-1136,速度-1。我使用MIG2.1生成了DDR2內存控制器內核。首先,根據ML523用戶指南中的DDR2引腳

2019-08-21 10:04:56

我在Kintex7 FPGA上使用MIG7控制器毀掉了對DDR3芯片的一些測試。在MIG7控制器內啟用XADC模塊。對于低于60℃的溫度,每件事都可以。當溫度達到60-65c時,我可以看到“app_rdy”信號變低并保持低電平直到FPGA重新編程。任何想法可能是錯誤的以及如何解決它?

2020-08-24 10:03:05

親愛的先生Vivado:v2016.4裝置:Artix-7我嘗試在Vivado中使用MIG設計DDR3 SODIMM接口。但是,MIG只生成一對ddr_ck。我認為DDR3 SODIMM需要2對ddr_ck,如ddr_ck0和ddr_ck1。我該如何生成2對ddr_ck?謝謝。

2020-08-24 06:45:17

大家好,我最近經歷了整整一周的時間,想知道如何在ZC706評估板上處理MIG。我的環境:ZC706評估板,帶微米DDR3 SODIMM存儲器(支持高達800MHz / 1,600 MT / s

2019-10-14 09:27:12

1. 文章研究主要問題在雙弧脈沖熔化極惰性氣體保護焊的過程中存主旁弧脈沖電流波形匹配以及耦合電弧穩定性的問題。2. 結論分析了雙弧脈沖 MIG 焊的特點和控制要求,實現雙弧脈沖 MIG 焊方法必須

2021-12-20 06:26:47

大家好,我用MIG 3.61生成DDR2內存控制器。在ISE 12.4中的映射期間,我有一個非常奇怪的錯誤,我不明白。錯誤:位置:864 - 不兼容的IOB被鎖定到同一個存儲區27沖突的IO標準

2020-06-11 11:52:56

嗨,我是jongbum。目前,MIG UltraScale DDR4支持最高2級。https://forums.xilinx.com/t5/Memory-Interfaces

2020-04-22 08:36:21

我有一段時間讓惡意生成的內容工作。我是一個超級菜鳥,所以我認為這對我來說是一個非常普遍的過程,但我需要一只手學習如何克服困難。我想我來自編程,我希望MIG能夠生成應該自己編譯的庫。但是,我發現事實

2019-08-06 07:54:35

存儲器接口生成器(MIG)解決方案---Virtex-4 存儲器接口和Virtex-II Pro存儲器解決方案 Virtex-4? FPGAs solve

2009-10-24 12:02:14

大家好 我的問題是DDR3校準完成失敗。調試結果:dbg_wrcal_err = 1,通過波形,我們可以看到寫入模式不匹配。 我的問題是MIG IP Core配置中是否有任何參數可以調整它?或者我

2020-07-23 10:09:37

創建我放置Zynq PS和互連的設計,并將主引腳作為輸出,以便在Artix中我使用Slave引腳作為輸入進行另一種設計并通過AXI控制MIG ,來自Zynq?將Zynq項目導出到SDK時,如果找不到

2020-08-04 10:04:05

嗨,我正在嘗試用我的設計生成帶有MIG3.2的DDR3控制器,并修改example_design項目以適應我的電路板。在更改.ucf文件之前,實現成功。但在改變.ucfaccording我的設計后

2020-06-10 08:25:16

所以我在Vivado 2013.4中有一個使用MIG 7 IP模塊的設計,它之前完成了合成和實現。我收到一條消息說合成和實現已經過時并決定再次運行它,據我所知,在此之前我沒有改變項目中的任何內容

2020-04-06 15:47:46

求大神指導,我用的芯片是k7系列XC7K325TFFG676,內存是MT41K256M16HA,在vivado環境下通過AXI總線將MIG與microblaze相連,實現控制數據在DDR3的存讀。差

2018-04-24 18:44:45

嗨,我有一個新的VCU108板。我正在嘗試運行預定義的MIG測試,以便開始使用。我使用本指南作為參考。https://www.xilinx.com/support/documentation

2019-09-30 06:18:43

你好,先生,當我使用mig 7核心時,我遇到了這些錯誤(合成傳遞),[放置30-69]實例U_mig_7series_0 / u_mig_7series_0_mig

2020-08-24 09:15:36

請問光電開關如何控制步進電機正反轉?

2021-10-14 08:31:50

DDR3的系統時鐘?如何在MIG工具中使用NO BUFFER?clcok資源能實現這一目標嗎?我已經嘗試了,但它失敗了。我注意到它在數據表中說系統時鐘必須與mig相同,它是否重要?我很想知道如何將這個MRCC引入MMCM,PLL或BUFGDS,或其他類似的東西。謝謝。

2020-07-22 07:43:59

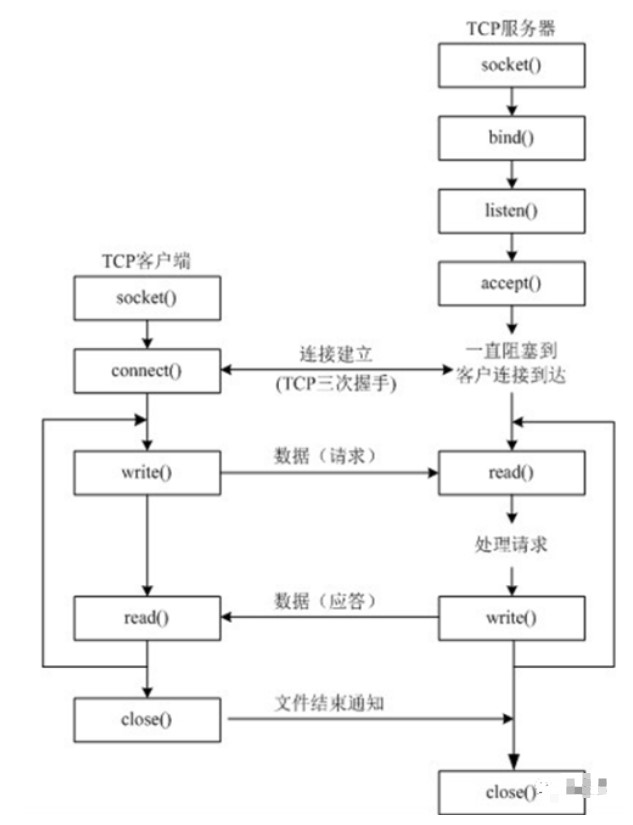

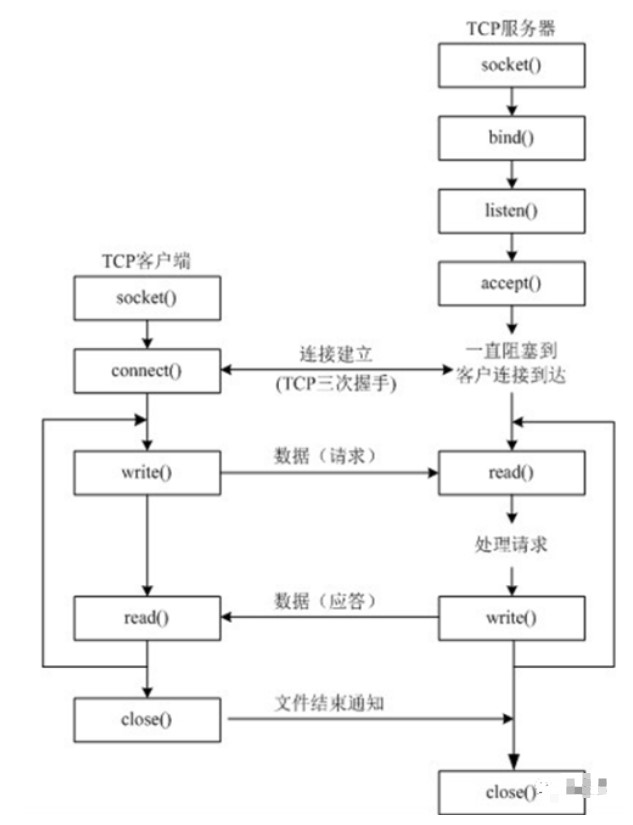

針對七自由度機械臂遠程控制的需要,構建了基于TCP/IP 網絡的控制系統。首先通過設計單片機系統實現本地端控制,然后運用WinSockets 類創建基于TCP/IP 的遠程控制程序,使連接在Inte

2009-08-15 16:01:43 22

22 針對TCP 在高速網絡中的缺陷,提出了改進的BIC TCP 擁塞控制算法。優化算法通過監控鏈路緩存的變化,調整探索可用帶寬過程中的擁塞窗口增加值,當擁塞發生時將慢啟動門限和擁

2009-09-17 10:18:17 15

15 TCP端到端等效噪聲模型及擁塞控制方法研究:針對傳統TCP擁塞控制協議在有線/無線混合網絡中存在的問題,采用通信系統加性噪聲分析方法和信道容量理論,將端到端鏈路背景流量等

2009-10-20 17:49:47 7

7 光電式液位開關和控制器

2009-12-16 15:15:40 20

20 隨著互聯網規模的增長,擁塞已經成為一個重要的研究熱點。介紹了TCP 擁塞控制的四種基本算法。TCP 擁塞算法對這些基本算法進行組合,分析其不同的特點,并且通過建模對算法組

2009-12-25 15:14:29 20

20 本文針對30mm厚的7A52中厚板高強鋁合金,進行了單絲單脈沖、復合脈沖和雙絲Tandem MIG焊工藝的研究,并應用于生產中。

2009-12-26 15:06:57 9

9 研究了雙脈沖MIG焊工藝對2219高強鋁銅合金焊縫組織及性能的影響,通過正交試驗確定了適合于2219鋁銅合金焊接的最佳雙脈沖MIG焊工藝參數。實驗結果表明,采用上述工藝參數焊接,

2009-12-26 15:09:46 11

11

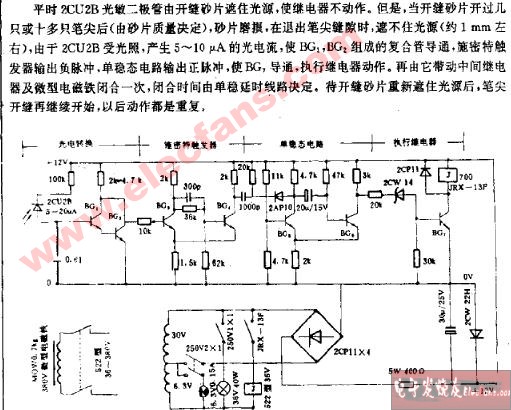

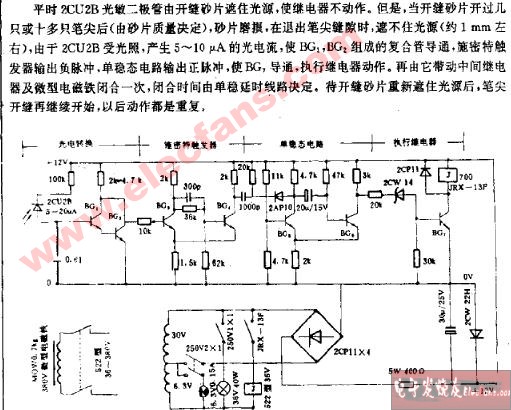

筆尖開縫控制的光電控制電路

2009-02-06 00:28:09 710

710

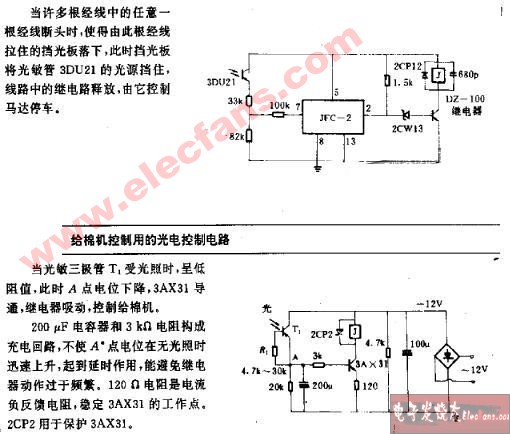

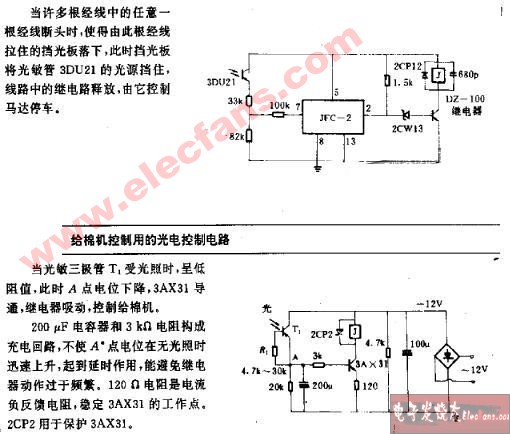

給棉機控制用的光電控制電路

2009-02-06 12:00:56 489

489

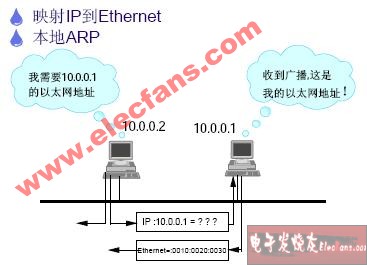

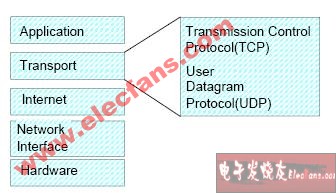

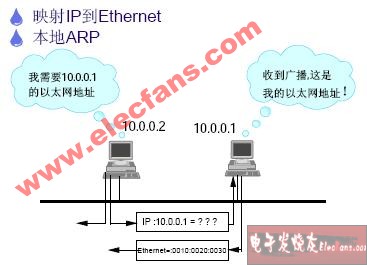

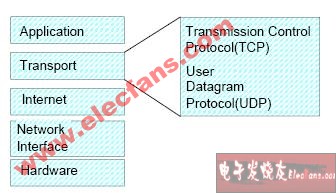

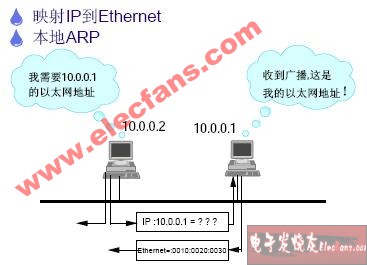

TCP/IP 傳輸層協議概攬

傳輸控制協議 TCP 是一個面向聯接的協議,允許從一臺

2009-06-09 21:51:51 732

732

TCP/IP傳輸層協議概攬

傳輸控制協議 TCP 是一個面向聯接的協議,允許從一臺

2009-06-09 21:52:31 869

869

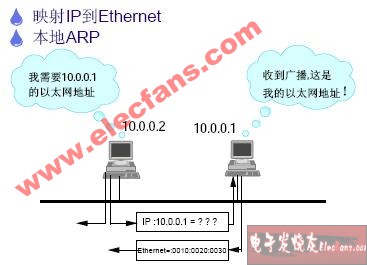

TCP/IP協議簡介

TCP/IP傳輸層協議概攬

傳輸控制協議 TCP 是一

2009-06-09 23:07:31 1205

1205

什么是TCP

英文原義:Transmission Control Protocol

中文釋義:(RFC-793)傳輸控制協議

注

2010-02-23 11:45:26 936

936 傳輸控制協議(TCP)/網絡層協議是什么意思

傳輸控制協議(TCP)

TCP提供的是一種可靠的數據流服務。當傳

2010-04-06 16:44:14 2688

2688 首先分析了面向控制應用TCP/IP協議的特點,隨后闡述了兩種針對專用控制網絡的以太網網關實現方案,即MCU或DSP+以太網網絡接口的TCP/IP實現。

2011-10-09 18:23:26 40

40 MIG 亞洲會議同時開啟中國物聯網企業的創新體驗之旅

2015-08-05 11:34:34 910

910 經典款逆變氣保焊MIG250一體機整機接線圖。

2016-03-17 10:42:25 6

6 全數字脈沖MIG逆變焊接電源的研制,下來看看。

2016-03-30 14:37:55 22

22 TCP-IP詳解卷2 TCP:傳輸控制協議,學習TCP很好的資料。歡迎下載。

2016-05-09 14:33:50 0

0 學習TCP-IP的很好的書。TCP-IP詳解卷3。

2016-05-09 14:33:50 0

0 學習TCP-IP的很好的書。TCP-IP詳解卷3。

2016-05-09 16:07:18 0

0 學習TCP-IP的很好的書。TCP-IP詳解卷3。

2016-05-09 16:07:18 0

0 學習TCP-IP的很好的書。TCP-IP詳解卷3。

2016-05-09 16:07:18 0

0 學習TCP-IP的很好的書。TCP-IP詳解卷3。

2016-05-09 16:07:18 0

0 學習TCP-IP的很好的書。TCP-IP詳解卷1。

2016-05-10 15:44:50 0

0 基于滑模控制的TCP網絡自適應研究_馮衛華

2017-01-28 21:37:15 0

0 TCP( Transmlssion Control Protocol)處于Internet協議棧體系結構中的傳輸層,它采用確認重發和流量控制機制,為傳輸層提供了可靠的、面向連接的字節流服務。它的傳輸

2018-02-08 16:29:08 0

0 軟開關型脈沖MIG焊接電源系統整體結構如圖1所示,由主電路、控制電路、驅動電路3個主要部分組成。系統采用目前較為常用的AC/ DC/AC/DC的逆變模式,脈沖開關信號來自單片機給出的控制指令,經驅動和放大后,為功率開關管提供固定頻率為20 kHz的高頻脈沖開關信號。

2018-04-13 08:25:00 3169

3169

對于mig與DDR3/DDR2 SDRAM的讀寫時序我們不需要了解太多,交給mig就可以了。

2019-03-03 11:11:53 5644

5644

本文檔的主要內容詳細介紹的是MIG250 MOS管整機電路原理圖免費下載。

2019-04-22 08:00:00 23

23 本文檔的主要內容詳細介紹的的是MIG-250單管IGBT整機電路原理圖免費下載。

2019-04-22 08:00:00 31

31 DDR對于做項目來說,是必不可少的。一般用于數據緩存和平滑帶寬。今天介紹下Xilinx DDR控制器MIG IP核的例化及仿真。 FPGA芯片:XC7K325T(KC705) 開發工具:Vivado

2020-11-26 15:02:11 7391

7391

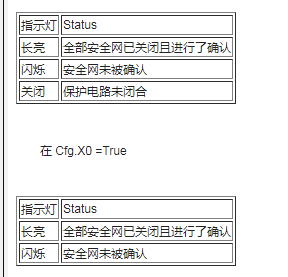

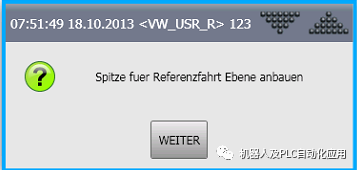

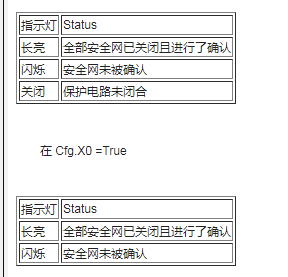

VASS標準中急停得接法與控制方法 1.硬線連接使用外部供電或者內部供電,雙通道監控。 SIL3/PLe?????? ??????? 必須通過兩個通道對傳感器/編碼器信號進行分析(“2 out

2020-12-23 16:48:35 3949

3949

其實不想用這個題目的,只因為TCP相關的東西比較吸引人的眼球,這篇文章的主題還是eBPF,而不是TCP。 用eBPF寫TCP擁塞控制算法只是本文所講內容的一個再平凡不過的例子。 先看兩個問題,或者說

2020-12-26 09:44:14 1437

1437 VASS標準PLC工位時序控制要點

1.順序塊 順序控制

2021-03-10 11:33:41 1854

1854 VASS標準中安全門的接法與控制方法

系統安全程序使用 : SFDOOR:安全門監視

2021-03-18 09:55:10 4204

4204

Profinet 診斷 操作頁面包含以下功能范圍: ? 顯示所有 Profinet 參與者的狀態信息和導航到 Profinet 詳細診斷 ? Profinet I/O 拓撲 這一點VASS06的界面

2021-06-09 16:46:55 2707

2707 1. 文章研究主要問題雙弧脈沖 MIG 焊是一種低能量輸入焊接方法, 其原有的雙電源供電系統結構復雜、協同控制困難、易受干擾。2. 結論提出了雙弧脈沖 MIG 焊一體化專用電源的設計方案

2021-11-08 20:51:02 11

11 TCP(Transmission Control Protocol 傳輸控制協議)是一種面向連接(連接導向)的、可靠的、 基于IP的傳輸層協議。

2022-05-25 15:38:45 1330

1330

為了實現 VASS 標準中的預期功能范圍,CPU 1517F至少需要固件版本 V2.5。

2022-07-15 10:50:01 1600

1600 傳輸控制協議(TCP,Transmission Control Protocol)是一種面向連接的、可靠的、基于字節流的傳輸層通信協議。

2022-08-19 09:17:23 2433

2433

VASS06由于PLC使用博途1500,博途1500,具有ProDiag功能,因此VASS06PLC的報警功能通過ProDiag來實現的!

2023-01-05 10:04:44 793

793 TCP(Transmission Control Protocol,傳輸控制協議),它是最常用傳輸層協議,也是最穩定傳輸層協議,很多上層應用都是依賴于TCP進程傳輸數據。

2023-02-14 10:26:23 2141

2141 之前有人發表論文說用chatGPT寫了一個MCU 還流片了,一副很膩害的樣子,在這個新聞的前幾天我就在朋友圈里說了,用chatGPT寫verilog代碼還是有一段距離的。今天我就手把手教大家,如何把這段距離給走了。今天用我讓chatGPT寫MIG 控制器為例,一句代碼都不想寫。

2023-07-10 09:12:11 222

222

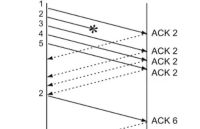

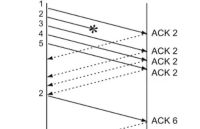

今天分享一篇文章,是關于 TCP 擁塞控制對數據延遲產生的影響的。作者在服務延遲變高之后進行抓包分析,結果發現時間花在了 TCP 本身的機制上面:客戶端并不是將請求一股腦發送給服務端,而是只發送

2024-01-19 09:44:05 202

202

電子發燒友App

電子發燒友App

評論