如圖所示是亮度延遲線應用電路。當亮度信號輸入到這一延遲線后,其輸出信號便經(jīng)過了一定時間的延遲,約延遲0.6us

2012-02-22 11:44:39 2263

2263

產(chǎn)品分類延遲線延遲線技術數(shù)字的延遲線類型固定的包裝類型表面貼裝時間延遲25 至 250 納秒上升時間2 納秒特征高工作頻率 (100 MHz)。非常低的地彈噪聲。電壓和溫度補償。可自動插入。TTL

2021-06-07 16:44:12

精度。全 CMOS 3D7428 集成電路被設計為可靠、經(jīng)濟的混合替代方案TTL 可編程延遲線。 它提供標準的 16 針自動插入式 DIP 和表面貼裝16 針 SOL。 8 引腳 SOIC 封裝可用

2021-06-07 16:52:35

856717延遲線濾波器產(chǎn)品介紹856717報價856717代理856717咨詢熱線856717現(xiàn)貨,王先生 深圳市首質(zhì)誠科技有限公司856717是一個延遲線濾波器設計為一個極寬帶設備與中心頻率為

2018-07-16 10:18:00

近年來,有關將CMOS工藝在射頻(RF)技術中應用的可能性的研究大量增多。深亞微米技術允許CMOS電路的工作頻率超過1GHz,這無疑推動了集成CMOS射頻電路的發(fā)展。目前,幾個研究組已利用標準

2021-07-29 07:00:00

CMOS數(shù)字集成電路是什么?CMOS數(shù)字集成電路有什么特點?CMOS數(shù)字集成電路的使用注意事項是什么?

2021-06-22 07:46:35

CMOS模擬電路設計教材本書共11章大小:22M微電子學系列1.半導體器件-物理與工藝2.表面安裝技術手冊3.多晶硅發(fā)射極晶體管及其集成電路4.超大規(guī)模集成電路設計基礎-系統(tǒng)與電路5.SOI技術—21世紀的硅集成電路技術6.CMOS模擬電路設計[hide]CMOS模擬電路設計.pdf[/hide]

2009-11-19 17:04:30

CMOS設計就是數(shù)字電路設計么?

2014-10-14 19:32:10

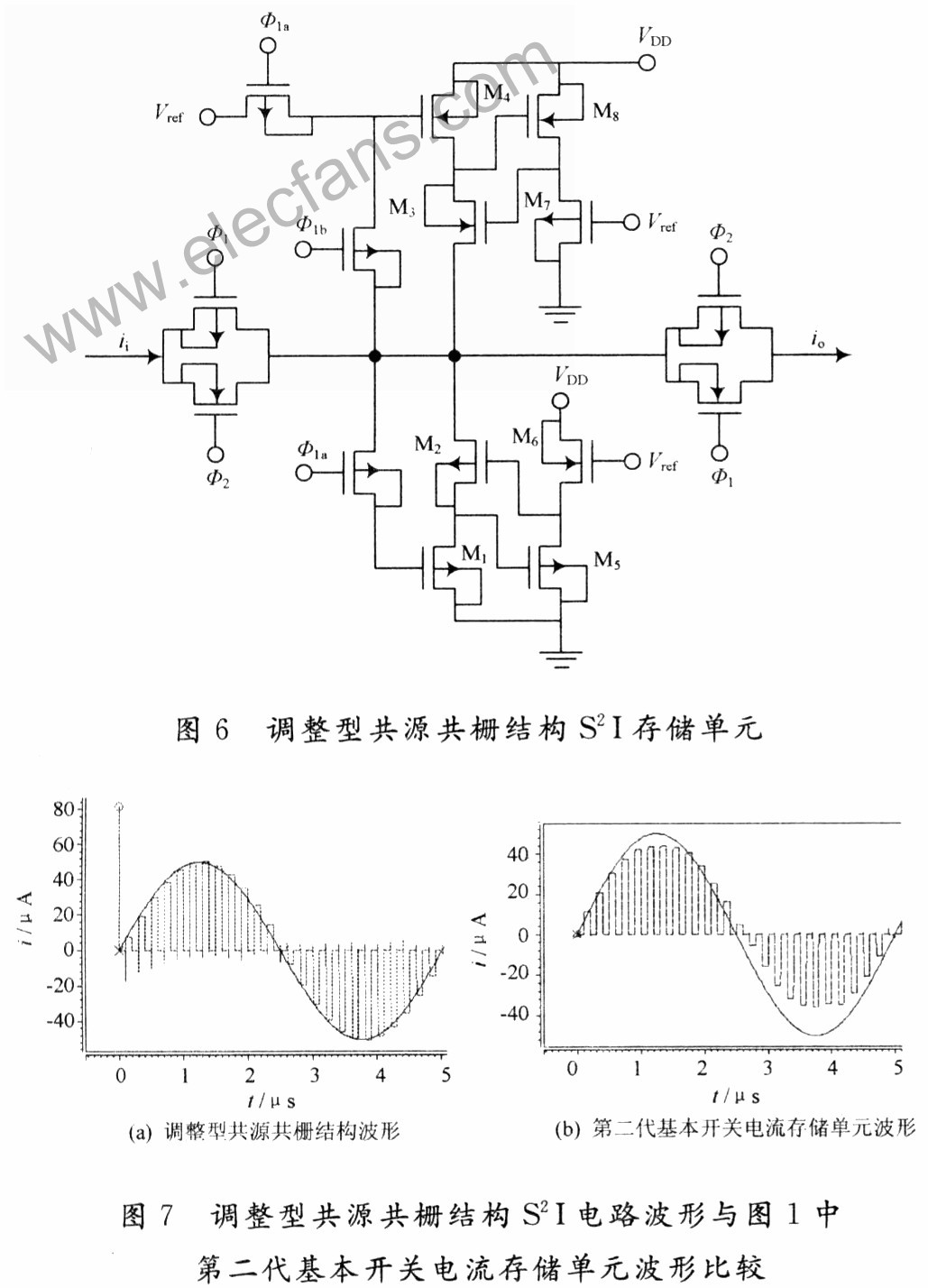

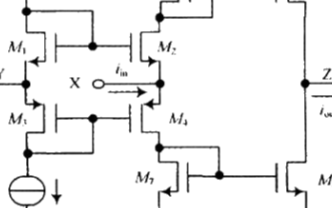

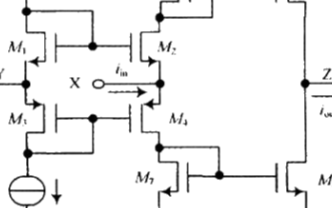

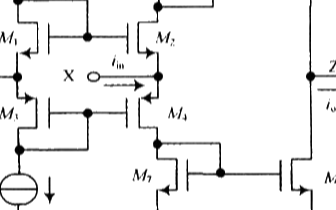

改善開關電流電路主要誤差的方案

2019-04-26 11:43:23

數(shù)字射頻技術對手機電路設計帶來的影響是什么?

2021-06-01 06:53:56

中的問題13 數(shù)字設計的質(zhì)量評價14 小結15 進一步探討第2章 制造工藝21 引言22 CMOS集成電路的制造23 設計規(guī)則——設計者和工藝工程師之間的橋梁24 集成電路封裝25 綜述:工藝技術

2009-02-12 09:51:07

技術。CMOS集成電路設計手冊原書由淺入深介紹從模型到器件,從電路到系統(tǒng)的全面內(nèi)容,可作為CMOS基礎知識的重要參考書

2019-03-15 18:09:22

Dallas Semiconductor的延遲線如何工作

2009-03-27 15:52:37

(數(shù)字可編程脈沖發(fā)生器、動態(tài)記憶定時器、門控振蕩器和脈沖控制器)。Data Delay Device, Inc數(shù)字延遲線與最常用的半導體系列(如 TTL、FAST、ECL、100K ECL、CMOS

2021-06-04 17:06:46

(數(shù)字可編程脈沖發(fā)生器、動態(tài)記憶定時器、門控振蕩器和脈沖控制器)。Data Delay Device, Inc數(shù)字延遲線與最常用的半導體系列(如 TTL、FAST、ECL、100K ECL、CMOS

2021-06-04 17:02:58

STD-020的無鉛要求。3、 有關濕度靈敏度水平(MSL),請參見EL9115的設備信息頁。有關MSL的更多信息,請參閱技術簡介TB363。典型性能曲線應用程序信息EL9115是一個三重模擬延遲線接收器

2020-09-17 17:22:08

我有 STM32F746/769 DISCO 模塊的音頻直通工作項目,其中來自輸入的 4 個樣本塊(2 個左通道和 2 個右通道)被傳遞到輸出通道 DMA 緩沖區(qū)。我的延遲線實現(xiàn)如下:#define

2023-01-11 07:10:58

SY89296L評估板,用于SY89296L,2.5V / 3.3V,2.5 GHz可編程延遲線的評估板,可使用數(shù)字控制信號延遲輸入信號。 SY89296L是一個可編程延遲線,使用數(shù)字控制信號延遲

2019-03-05 09:14:19

SY89297U,GB以太網(wǎng)交換機延遲線評估板。 SY89297U,2.5 / 3.3V 3.2Gbps雙通道CML可編程延遲線評估板

2019-01-30 15:24:59

TDA46611H基帶色度信號延遲線資料下載內(nèi)容包括:TDA46611H引腳和功能TDA46611H內(nèi)部方框圖TDA46611H典型應用電路

2021-03-29 07:32:15

隨著射頻無線通信事業(yè)的發(fā)展和移動通訊技術的進步,射頻微波器件的性能與速度成為人們關注的重點,市場對其的需求也日益增多。目前,CMOS工藝是數(shù)字集成電路設計的主要工藝選擇,對于模擬與射頻集成電路來說,有哪些選擇途徑?為什么要選擇標準CMOS工藝集成肖特基二極管?

2019-08-01 08:18:10

從工藝轉模擬電路設計可能嗎?求幫助啊 本人本科微電子專業(yè)現(xiàn)在在fab做工藝,想轉模擬電路設計 。大學期間學習過cmos模擬電路設計半導體器件pspice。不知道現(xiàn)在學學有機會沒想跳出制造業(yè)神啊給個機會吧

2012-01-12 15:49:19

如圖所示,兩個射頻信號要在混頻器里面混頻,但是那個信號到達混頻器的時間不一樣,國內(nèi)有這種延遲線系統(tǒng),可以調(diào)節(jié)射頻信號的延遲嗎?

2020-06-07 14:14:28

請問各位,如何將延遲線與示波器集成?剛剛學習labview,求思路謝謝!

2019-12-14 14:11:19

=2023685633&uk=1564223783&fid=2241318043[/hide]內(nèi)容簡介詳細講述CMOS數(shù)字集成電路的相關內(nèi)容,反映現(xiàn)代技術發(fā)展水平并提供了電路設計的最新資料。《CMOS

2013-11-30 11:25:19

的頻率特性第7章 噪聲第8章 反饋第9章 運算放大器第10章 穩(wěn)定性與頻率補償?shù)?1章 帶隙基準第12章 開關電容電路第13章 非線性與不匹配第14章 振蕩器第15章 鎖相環(huán)第16章 短溝道效應與器件模型第17章 CMOS工藝技術第18章 版圖與封裝英漢詞匯對照查看全部↓前言/序言······下載鏈接:`

2017-12-20 17:57:10

了具有256個狀態(tài)的CARRY4基元的延遲線,這些狀態(tài)捕獲來自LFSR(線性反饋移位寄存器)的稱為觸發(fā)的數(shù)字信號。在tdc_clock的每個上升時鐘轉換(400 MHz)時,我通過DFlipFlop

2020-06-19 12:44:35

為數(shù)字量,經(jīng)高速鎖存器鎖存后得到代表延時信息的溫度計編碼值來實現(xiàn)高分辨率的時間測量。提出了一種實用的高速時鐘下(400MHz)延遲線延時信息的鎖存方法,并設計了FPGA時間數(shù)字轉換電路及其延遲單元時間

2010-05-13 09:04:22

那個大神給我講一下什么是超聲延遲線的色度信號分離??和超聲波色度延遲線有什么區(qū)別嗎??

2013-12-29 22:44:34

如何實現(xiàn)CMOS圖像敏感器驅(qū)動電路設計?CMOS圖像敏感器STAR250的技術指標是什么?如何實現(xiàn)Verilog HDL驅(qū)動時序設計?

2021-04-20 06:59:27

延遲線用于需要幾納秒(ns)信號延遲的應用中,或者需要增量定時校正才能使系統(tǒng)正常工作的應用中。本文討論了輸入信號可能具有的最大頻率。計算最大輸入頻率在計算固定值延遲線的最大輸入頻率時,要考慮的關鍵

2020-06-03 13:48:07

異步電路匹配延遲的延遲線如何設計能實現(xiàn)自適應連續(xù)地調(diào)整延遲長度。這是一個新的想法,希望有大神能和我一起討論一下

2019-03-19 17:19:50

概述:MN3868是一款作用于CRT彩色電視機中的彩色基帶延遲線IC芯片,MN3868采用16引腳DIP封裝工藝。

2021-04-08 07:59:30

概述:STV2180是意法半導體公司(STMicroelectronics)出品的一款用作于CRT彩電中的圖像處理芯片,它具有一個線路延遲的延遲線,用于將色度解碼器與顏色匹配差分信號輸出(R-Y)和(B-Y)。

2021-04-07 07:05:41

當前固體微光器件以EBCCD 及EMCCD 器件為主,隨著CMOS 工藝及電路設計技術的發(fā)展, 微光CMOS 圖像傳感器的性能在不斷提高,通過采用專項技術,微光CMOS 圖像傳感器的性能已接

2018-11-12 15:37:40

我正在嘗試使用virtex 5上的Block RAM來實現(xiàn)延遲線。延遲線需要將數(shù)據(jù)延遲一個時鐘周期。這可能使用Block RAM嗎?我嘗試使用簡單的雙端口RAM,“先讀”作為操作模式。我正在寫一個

2020-06-18 15:40:33

近年來,有關將CMOS工藝在射頻(RF)技術中應用的可能性的研究大量增多。深亞微米技術允許CMOS電路的工作頻率超過1GHz,這無疑推動了集成CMOS射頻電路的發(fā)展。目前,幾個研究組已利用標準

2019-08-22 06:24:40

【簡介】模擬集成電路的設計與其說是一門技術,還不如說是一門藝術。它比數(shù)字集成電路設計需要更嚴格的分析和更豐富的直覺。嚴謹堅實的理論無疑是嚴格分析能力的基石,而設計者的實踐經(jīng)驗無疑是誕生豐富直覺的源泉

2016-10-07 08:38:30

·····我對延遲線不太了解·那位大蝦能夠介紹一下·和使用方法·我要對一個信號進行幾微秒的延遲·····用哪款型號的比較好·最好能夠有使用方法·先謝謝了·

2011-09-05 09:16:12

CMOS 模擬開關對傳輸信號的影響是什么呢?如何實現(xiàn)改進型模擬開關電路設計?

2021-04-02 07:15:27

檢測時,可通過測量亮度延遲線輸入端與輸出端之間的電阻值是否正常來判斷其是否損壞。用萬用表R×10 kΩ檔測量亮度延遲線輸入端與輸出端之間的電阻值(正常值為30~40 Ω)。若測得阻值為無窮大,則表明

2021-05-24 07:43:48

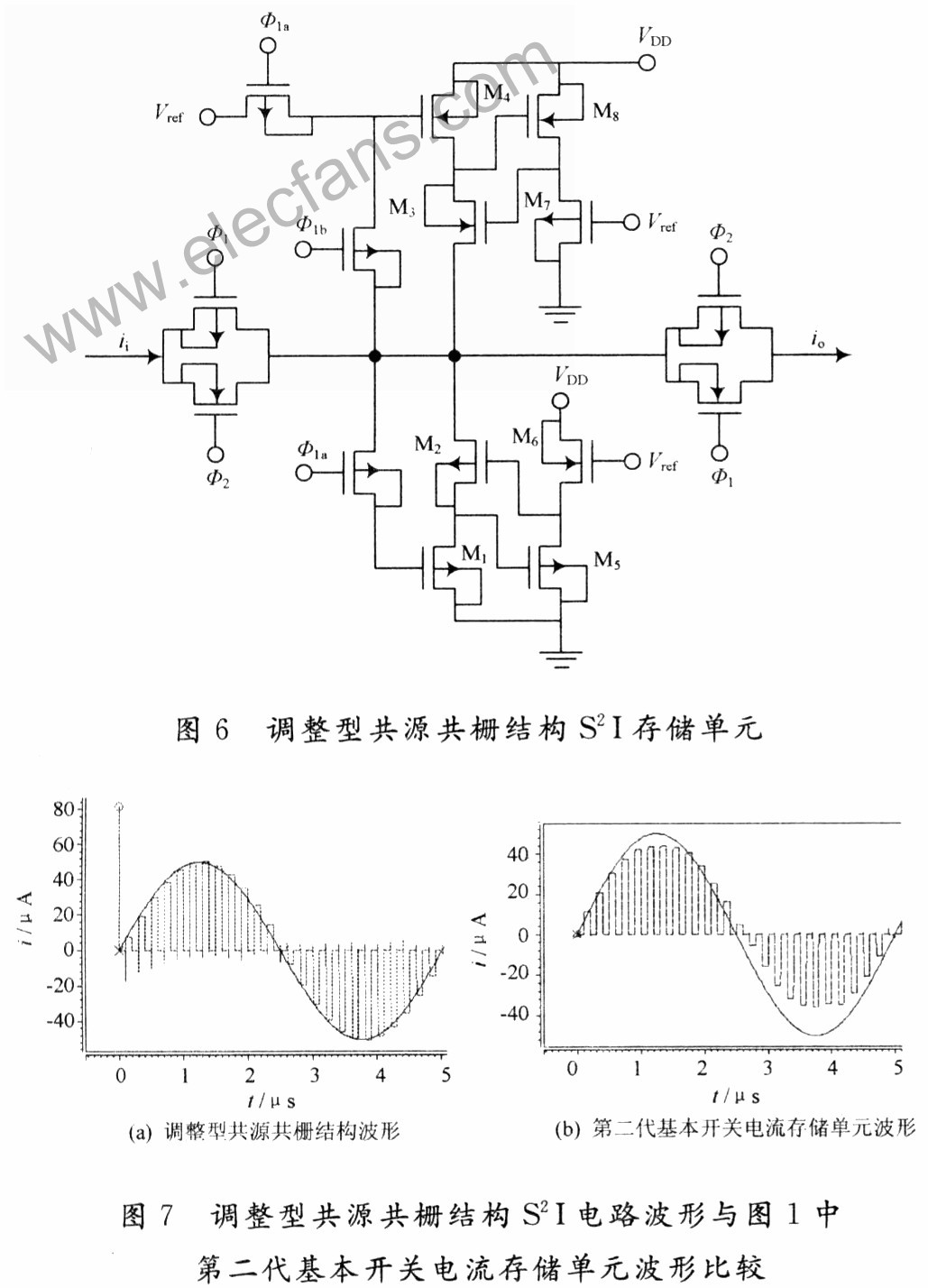

基于開關電流技術與數(shù)字CMOS工藝的延遲線電路設計

2019-04-26 11:41:28

11位的輸入信號,低5位用延遲線和多選器實現(xiàn),高6位用計數(shù)器和比較器實現(xiàn),有木有大神會寫這個的,其中那個延遲線怎么實現(xiàn)啊,直接用D觸發(fā)器可以嗎

2020-11-28 20:44:44

開關電流電路中的時鐘饋通誤差和傳輸誤差分析,如何解決開關電流電路的誤差問題?

2021-04-12 07:04:33

SY89295L評估板,用于SY89295L,2.5V / 3.3V,2.5 GHz可編程延遲線的評估板,可使用數(shù)字控制信號延遲輸入信號。 SY89295L是一個可編程延遲線,使用數(shù)字控制信號延遲

2019-03-05 08:20:02

小波變換開關電流電路CAD設計(2)

2019-04-18 07:55:58

Dallas Semiconductor的延遲線如何工作

2009-03-23 18:42:47 20

20 本文主要講述的是Dallas Semiconductor的延遲線如何工作?

2009-04-26 16:16:12 7

7 本文主要講述的是Dallas Semiconductor的延遲線如何工作。

2009-04-29 10:28:59 34

34 針對蘭州重離子加速器冷卻儲存環(huán)(HIRFL-CSR)踢軌磁鐵(Kicker)電源的需要,設計了一種基于可編程邏輯器件(CPLD)的高速可程控數(shù)字延遲線系統(tǒng)。文中分析介紹了數(shù)字延遲線系統(tǒng)

2009-09-21 10:17:00 14

14 描述Data Delay Devices 的 1503-60A 是一種延遲線,延遲范圍為 0 至 60 ns,上升時間為 12 nS。標簽:表面貼裝,機械可變,攻絲

2023-02-03 12:34:03

CMOS工藝中GG2NMOS結構ESD保護電路設計:采用GG2NMOS 結構的ESD 保護電路的工作原理和對其進行的ESD 實驗,提出了一種保護電路的柵耦合技術方案,并達到了預期效果. 通過實驗可以看出其性

2009-11-20 14:48:43 41

41 產(chǎn)品簡介上海屹持專業(yè)推薦的自由空間光學延遲線,性能穩(wěn)定,結構緊湊,性價比高。經(jīng)過廣泛的實驗驗證,可高效穩(wěn)定的運行與各種太赫茲時域光譜儀系統(tǒng)中。產(chǎn)品特點—— 內(nèi)置電機—— 小巧緊湊—— 穩(wěn)定性高

2023-03-15 13:57:46

MDL-002系列光纖延遲線 產(chǎn)品簡介上海屹持光電推出的電動可變光延遲線提供高達 17 cm 的精確光路延遲,對應于時域中 560 皮秒的最大延遲。產(chǎn)品特點——通過 RS-232 進行獨立

2023-03-21 15:01:29

隨著工藝進入深亞微米階段,漏電流帶來的靜態(tài)功耗已經(jīng)成為不可忽視的部分。多閾值CMOS技術是一種降低電路漏電流功耗的有效方法。本文在延遲不敏感異步電路中應用多閾值CMOS技

2010-02-24 15:51:06 12

12 TTM Technologies 的 XDL09-9-204 是一款延遲線,頻率為 869 至 894 MHz,平均延遲 20.25 nS,插入損耗 0.35 dB,功率 1 W,回波

2023-08-15 14:15:56

TTM Technologies 的 XDL09-9-224S 是一款延遲線,頻率為 855 至 894 MHz,平均延遲 22.6 nS,插入損耗 7.2 ±1.0 dB,功率 1 W,回波損耗

2023-08-15 14:18:06

TTM Technologies 的 XDL15-3-030S 是一款延遲線,頻率為 135 至 2700 MHz,群延遲 2.85 nS,插入損耗 -1.5 dB,功率 1 W,回波損耗 -12

2023-08-15 14:20:08

TTM Technologies 的 XDL20-11-180S 是一款延遲線,頻率為 869 至 894 MHz,平均延遲 11.25 ns,插入損耗 0.4 dB,功率 1 W,回波損耗 20

2023-08-15 14:21:58

摘要:為了提高數(shù)字通信電路的速度,設計了兩種BiCMOS開關電流存儲器。設計過程中在電路的關鍵部位配置有限的雙極型晶體管(BJT),但在電路的主體部分則設置MOS器件。推導出了存

2010-05-13 09:04:13 16

16 對第一代開關電流存儲單元產(chǎn)生的時鐘饋通誤差做了合理的近似分析,設計了一種高性能開關電流存儲單元。該電路僅在原存儲單元的基礎上增加了一個MOS管,使誤差降為原來的4%,

2010-07-05 14:50:48 22

22 基于開關電流電路提出一種用小波濾波器實現(xiàn)小波變換的方法。通過對母小波的一種數(shù)值逼近得到小波函數(shù)的有理公式,并以Mexican Hat小波為例模擬該逼近過程,用Matlab對逼近過程進

2010-12-10 17:41:19 26

26 開關電流技術(SI)是一種可取代開關電容技術的數(shù)據(jù)采樣技術。首先介紹了SI技術,然后以SI電路基本單元為例,分析了SI電路存在的各種誤差,并針對這些誤差提出了解決方法

2010-12-20 09:45:35 37

37 低電壓甲乙類開關電流存儲單元

引言 開關電流存儲單元是電流模式采樣數(shù)據(jù)信號處理系統(tǒng)的基本單元電路,其性能的優(yōu)

2007-08-15 16:06:29 563

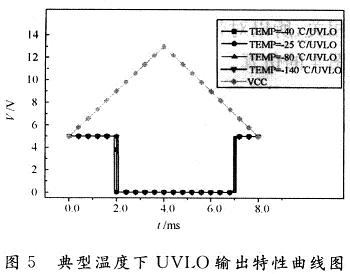

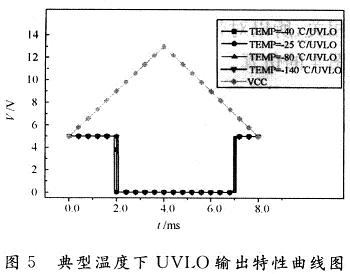

563 基于0.5μm BCD工藝的欠壓鎖存電路設計

隨著集成電路技術的發(fā)展,對電源管理芯片的開關頻率、傳輸延遲、穩(wěn)定性、功耗等各種要求越來越高,以保證電源電壓在波動

2009-11-26 09:27:23 1750

1750

延遲線電路,延遲線電路是什么意思

延遲線電路的定義

2010-03-09 11:30:46 1148

1148 延遲線,延遲線是什么意思

延遲線 delay line 用于將電信號延遲一段時間的元件或器件稱為延遲線。延遲線應在通

2010-03-09 11:33:16 7629

7629 延遲線的分類有哪些?

延遲線可分為兩大類:即電磁延遲線和超聲波延遲線,尤以後者可獲較大時延。

2010-03-09 11:39:56 1536

1536 開關電流技術是一種新的模擬信號采樣、保持、處理技術。它具有電流模電路的特有優(yōu)點,如速度快,適合于低電壓工作等。與傳統(tǒng)的開關電容技術相比,開關電流技術不需

2010-08-11 09:32:55 1034

1034

講述了用信號流圖和積分器設計 開關電流濾波器 的方法。本方法簡明直觀,無力概念清楚,容易推廣到其他開關電流濾波器的設計

2011-06-13 18:28:48 59

59 文中介紹了一種無需外部時鐘、可抵消部分工藝偏差的差分延遲線ADC,并對其建模。該ADC結構簡單、控制信號在內(nèi)部產(chǎn)生、轉換速率快、功耗低,可應用在高頻數(shù)字DC/DC控制芯片中。

2011-08-23 11:43:09 1236

1236

本書是模擬集成電路設計課的一本經(jīng)典教材。全書共分5個部分。主要介紹了模擬集成電路設計的背景知識、基本MOS半導體制造工藝、CMOS技術、CMOS器件建模,MOS開關、MOS二極管、有源電

2012-02-15 15:26:02 0

0 超聲波色度延遲線電路,電路中的DL是超聲波色度延遲線。VT1是色度信號F延遲放大管,VT2是紅色差信號分量V信號放大管,VT3是藍色差信號分量U信號放大管。

2012-03-27 15:48:34 1332

1332

為了提高數(shù)字集成電路芯片的驅(qū)動能力,采用優(yōu)化比例因子的等比緩沖器鏈方法,通過Hspice軟件仿真和版圖設計測試,提出了一種基于CSMC 2P2M 0.6 m CMOS工藝的輸出緩沖電路設計方案。本

2012-04-05 15:17:32 51

51 近年來,有關將CMOS工藝在射頻(RF)技術中應用的可能性的研究大量增多。深亞微米技術允許CMOS電路的工作頻率超過1GHz,這無疑推動了集成CMOS射頻電路的發(fā)展。目前,幾個研究組已利

2012-05-21 10:06:19 1850

1850

亮度延遲線的選用、檢測與代換,色度延遲線的選用、檢測與代換, 自制延遲線的結構

2012-06-19 11:49:20 1480

1480

CMOS工藝,具體的是CMOS結構對集成電路設計有幫助,謝謝

2016-03-18 15:35:52 21

21 基于聲體波延遲線的火控雷達組網(wǎng)標定信標_周文佳

2017-01-07 20:32:20 0

0 基于IIR數(shù)字網(wǎng)絡的開關電流電路小波變換方法_童耀南

2017-01-07 21:45:57 0

0 本文研究了在CMOS工藝中I/O電路的ESD保護結構設計以及相關版圖的要求,其中重點討論了PAD到VSS電流通路的建立。

2017-09-07 18:29:51 7

7 開關電流--數(shù)字工藝的模擬技術

2017-09-11 17:01:17 6

6 基于開關電流電路提出一種用小波濾波器實現(xiàn)小波變換的方法。通過對母小波的一種數(shù)值逼近得到小波函數(shù)的有理公式,并以Mexican Hat小波為例模擬該逼近過程,用Matlah對逼近過程進行仿真,同時

2017-12-06 17:15:25 18

18 開關電流技術是一種模擬取樣信號處理新技術,主要應用于開關電流濾波器和模數(shù)轉換器設計。由于開關電流電路無需使用雙層多晶硅電容,因此電路可以采用標準的CMOS數(shù)字工藝實現(xiàn),從而降低了制造成本;采用

2020-05-21 08:03:00 1280

1280

電視機的亮度延遲線的制作,Luminance delay line

關鍵字:亮度延遲線制作

亮度延遲線的選用、檢測與代換

??? 亮度

2018-09-20 19:15:25 925

925 開關電流技術是近年來提出的一種新的模擬信號采樣、保持、處理技術。與已成熟的開關電容技術相比,開關電流技術不需要線性電容和高性能運算放大器,整個電路均由MOS管構成,因此可與標準數(shù)字CMOS工藝兼容

2018-09-29 08:57:00 11558

11558

《CMOS模擬集成電路設計》(第2版)是模擬集成電路設計課的一本經(jīng)典教材。全書共分5個部分。主要介紹了模擬集成電路設計的背景知識、基本MOS半導體制造工藝、CMOS技術、CMOS器件建模,MOS開關

2019-03-11 08:00:00 0

0 是模擬集成電路設計課的一本經(jīng)典教材。全書共分5個部分。主要介紹了模擬集成電路設計的背景知識、基本MOS半導體制造工藝、CMOS技術、CMOS器件建模,MOS開關、MOS二極管、有源電阻、電流阱和電流

2019-08-13 08:00:00 146

146 開關電流技術是一種模擬取樣信號處理新技術,主要應用于開關電流濾波器和模數(shù)轉換器設計。由于開關電流電路無需使用雙層多晶硅電容,因此電路可以采用標準的CMOS數(shù)字工藝實現(xiàn),從而降低了制造成本;采用

2021-03-23 09:38:02 1562

1562

延遲開關電路指的是當電路開關按下時,負載需要經(jīng)過一定時間后才能夠獲得電源。

2023-03-13 13:54:21 1396

1396

![]()

![]()

電子發(fā)燒友App

電子發(fā)燒友App

評論