本文中的測控系統(tǒng)是某型號無人機(jī)電子系統(tǒng)中的一個重要部分。為了對測控系統(tǒng)的改進(jìn)優(yōu)化設(shè)計(jì)進(jìn)行驗(yàn)證,需要對軟件進(jìn)行長期運(yùn)行考核,對該分系統(tǒng)進(jìn)行單機(jī)驗(yàn)收與聯(lián)試,驗(yàn)證其與其它分系統(tǒng)接口的匹配性;同時還要為測控系統(tǒng)提供真實(shí)的物理連接接口、動態(tài)輸入參數(shù),進(jìn)而提供與無人機(jī)同步的仿真運(yùn)行環(huán)境。遙測解調(diào)及遙控注入測試卡是根據(jù)驗(yàn)證測控系統(tǒng)工作的需要而設(shè)計(jì)開發(fā)的,它能為其提供遙測解調(diào)、遙控?cái)?shù)據(jù)注入、直接指令注入、觸點(diǎn)信號和40kHz時鐘等接口信號。能對原測控系統(tǒng)進(jìn)行測試的遙測解調(diào)及遙控注入測試卡是ISA插卡,使用分離器件來實(shí)現(xiàn)。隨著計(jì)算機(jī)硬件的發(fā)展,PCI總線已經(jīng)成為當(dāng)今高性能微型計(jì)算機(jī)事實(shí)上的總線標(biāo)準(zhǔn),PCI總線的性能遠(yuǎn)遠(yuǎn)高于ISA總線,因此基于PCI的遙測解調(diào)及遙控注入測試卡更符合實(shí)際應(yīng)用的需要。FPGA技術(shù)的應(yīng)用日益成熟和廣泛,用FPGA芯片替代分離器件將大大提高測試卡的可靠性。本文論述了基于Altera公司的Acex1K系列芯片(如ACEK1K30QC208等),采用PCI局部總線標(biāo)準(zhǔn),設(shè)計(jì)基于PCI的遙測解調(diào)及遙控注入測試卡的一些關(guān)鍵技術(shù)。

1 PCI局部總線

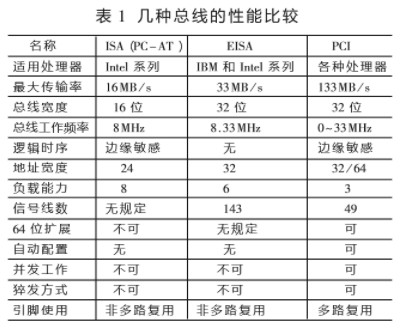

以Intel公司為首的PCI SIG小組推出的PCI總線標(biāo)準(zhǔn)是一種高端現(xiàn)代局部總線,它具有符合工業(yè)標(biāo)準(zhǔn)、性能高、成本低、獨(dú)立于處理器、允許靈活配置、使用壽命長、可操作性強(qiáng)和軟件兼容性好等優(yōu)點(diǎn),因此在嵌入式計(jì)算機(jī)和工業(yè)控制計(jì)算機(jī)領(lǐng)域具有廣闊的應(yīng)用前景。PCI總線與傳統(tǒng)ISA總線、現(xiàn)代的EISA總線的性能比較如表1所示。

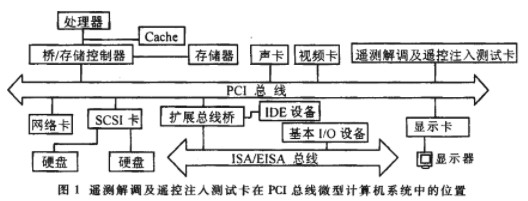

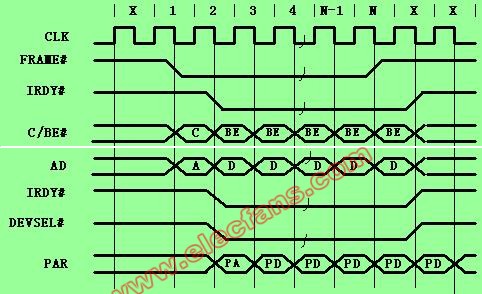

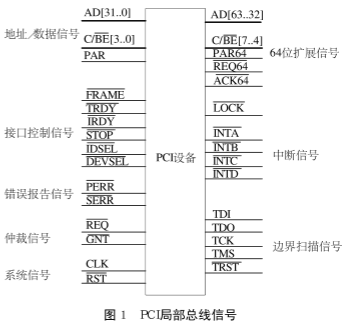

PCI局部總線是微型計(jì)算機(jī)中處理器/存儲器與外圍控制部件、擴(kuò)展卡之間的互連接口。PCI總線規(guī)范是互連機(jī)構(gòu)的協(xié)議及電氣和機(jī)械配置的規(guī)范,其用途是在高度集成的外設(shè)控制器器件、擴(kuò)展板和處理器之間提供一種內(nèi)部聯(lián)結(jié)機(jī)制。本文中的基于PCI的遙測解調(diào)及遙控注入測試卡是由PCI總線完成測試卡和處理器/存儲器的連接,其在PCI總線微型計(jì)算機(jī)系統(tǒng)中的位置如圖1所示。

2 FPGA技術(shù)

在現(xiàn)代電子系統(tǒng)領(lǐng)域,EDA技術(shù)已經(jīng)逐漸成為電子系統(tǒng)的主要設(shè)計(jì)手段。FPGA(現(xiàn)場可編程門陣列)是EDA技術(shù)中的一種重要應(yīng)用。FPGA器件在結(jié)構(gòu)上由邏輯功能塊排列為陣列,并由可編程的內(nèi)部連線連接這些功能塊,來實(shí)現(xiàn)一定的邏輯功能。設(shè)計(jì)遙測解調(diào)及遙控注入測試卡的數(shù)字和邏輯電路部分均由FPGA器件來完成。

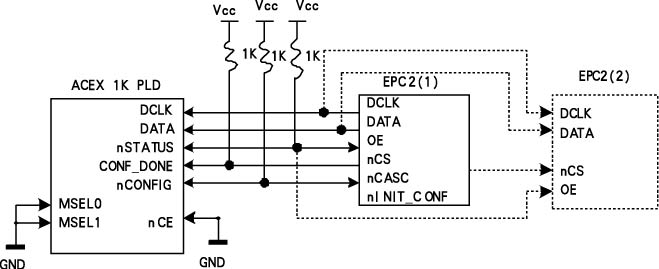

考慮到遙測解調(diào)及遙控注入測試卡邏輯功能的需要,本設(shè)計(jì)采用Altera公司的FPGA芯片ACEK1K50QC208。該芯片具有5萬門可編程邏輯單元,屬于Sram型的FPGA芯片,邏輯信息保存在專門的靜態(tài)存儲器中(本設(shè)計(jì)中使用EPC1PC8芯片作為靜態(tài)儲存器),上電時動態(tài)加載。這種類型的器件在驗(yàn)證期間可以使用下載工具將邏輯加載到芯片中,驗(yàn)證完畢后需要將邏輯信息燒寫在靜態(tài)存儲器中,以后系統(tǒng)上電時,FPGA從靜態(tài)存儲器中自動加載邏輯。

使用FPGA進(jìn)行電路設(shè)計(jì)的步驟為:首先采用目前流行的硬件描述語言Verilog HDL設(shè)計(jì)輸入,即將設(shè)計(jì)的邏輯、時序關(guān)系輸入計(jì)算機(jī);之后,使用Maxplus II軟件進(jìn)行前仿真、綜合、布局布線和后仿真,即驗(yàn)證輸入的硬件描述語言的邏輯關(guān)系是否正確,若正確則用抽象語言將邏輯描述分解為具體的邏輯單元,在FPGA器件中實(shí)現(xiàn),并驗(yàn)證布局布線后仿真是否正確;最后,進(jìn)行硬件驗(yàn)證,將計(jì)算機(jī)上布局布線之后生成的文件加載到FPGA中,以驗(yàn)證它的實(shí)際工作情況同設(shè)計(jì)是否一致。

3 遙測解調(diào)及遙控注入測試卡的設(shè)計(jì)

3.1 測試卡的測試接口信號要求

測試卡要根據(jù)測試的需要提供測試接口信號。這些測試接口信號共包括五類:

(1)遙測解調(diào)信號:測試卡集成了兩路遙測解調(diào)器的功能。其中每一路遙測解調(diào)器都能夠輸出幀同步信號、路同步信號和數(shù)據(jù)時鐘信號。被測系統(tǒng)根據(jù)解調(diào)器卡輸出的上述三個信號,按照一定的時序關(guān)系輸出串行的遙測數(shù)據(jù)。

(2)遙控?cái)?shù)據(jù)注入:測試卡集成了兩路遙控?cái)?shù)據(jù)注入單元。其中每一路遙控?cái)?shù)據(jù)注入單元都能夠提供數(shù)據(jù)有效信號、時鐘信號和數(shù)據(jù)信號。

(3)遙控指令:測試卡提供1套24路直接遙控指令輸出。每路指令處于工作狀態(tài)時,集電極開路門接通(低電平);處于非工作狀態(tài)時,集電極開路門不接通(高電平)。

(4)觸點(diǎn)信號:測試卡提供1套11路(共22根引腳)觸點(diǎn)輸出信號。每路觸點(diǎn)信號為開關(guān)閉合有效,斷開無效。

(5)時鐘輸出:測試卡提供1路40kHz的時鐘輸出信號。

3.2 測試卡硬件系統(tǒng)的實(shí)現(xiàn)

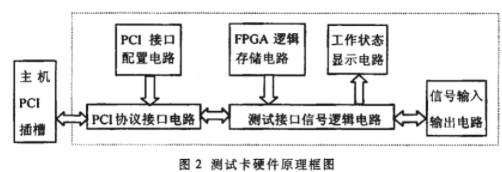

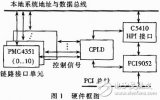

在該測試卡的電路系統(tǒng)中,由FPGA芯片提供測試接口信號并實(shí)現(xiàn)軟件接口邏輯設(shè)計(jì);由PCI接口芯片實(shí)現(xiàn)測試卡同計(jì)算機(jī)上PCI總線的連接;由分離器件實(shí)現(xiàn)測試接口信號的輸入輸出。測試卡的硬件原理框圖如圖2所示。

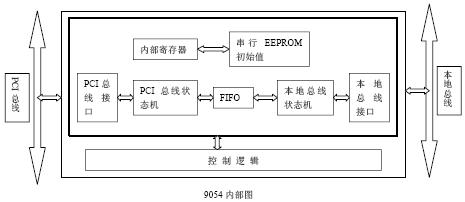

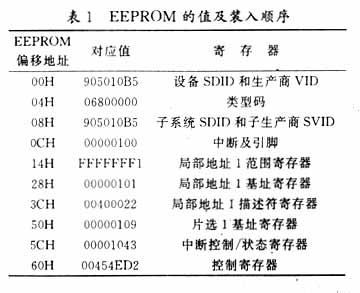

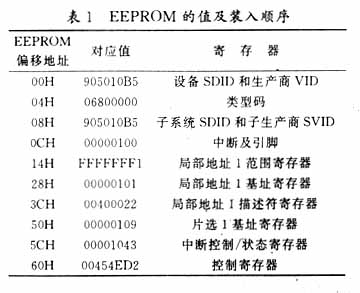

在圖2中,PCI協(xié)議接口電路主要是使用PCI總線接口芯片9052來提供高性能的PCI總線接口,其使用需要對它的PCI配置寄存器和本地配置寄存器進(jìn)行設(shè)置。在PCI接口配置電路中,采用93CS46N串行EEROM芯片對9052芯片PCI配置寄存器和本地配置寄存器進(jìn)行設(shè)置。

測試接口信號邏輯電路圍繞FPGA芯片ACEK1K30QC208進(jìn)行設(shè)計(jì)。該芯片能夠完成測試卡需要的五類測試信號的邏輯設(shè)計(jì),還能實(shí)現(xiàn)可供使用人員配置的測試卡軟件接口,以及和PCI總線接口進(jìn)行信號傳輸?shù)倪壿嫛CEK1K30QC208芯片是Sram型的FPGA芯片,還需要專門的邏輯存儲電路來保存上述邏輯信息。邏輯存儲電路使用靜態(tài)存儲器芯片EPC1PC8芯片,系統(tǒng)上電時,FPGA從存儲器中自動加載邏輯。

測試信號輸入輸出電路完成測試卡與被測設(shè)備的信息交換。對于測試卡提供的五類測試信息,遙控指令和觸電信號需要模擬器件和電子開關(guān)進(jìn)行轉(zhuǎn)換,而其它信號則可以通過連接器直接輸入輸出。

工作狀態(tài)顯示電路提供測試卡的工作狀態(tài),如測試卡是否加電成功、是否邏輯下載成功、是否在進(jìn)行遙控指令注入、是否在進(jìn)行遙測數(shù)據(jù)接收等。工作狀態(tài)顯示電路的邏輯也來自于測試接口信號邏輯電路。

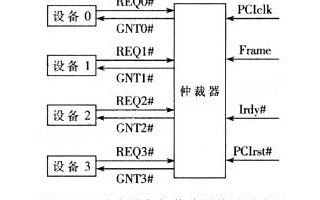

3.3 PCI局部總線和測試卡本地總線的連接

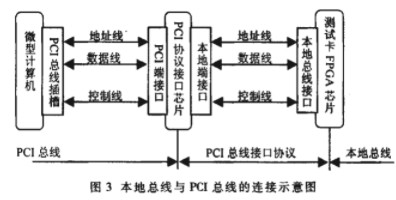

本設(shè)計(jì)采用了PLX Technology公司的PCI總線協(xié)議接口芯片9052來實(shí)現(xiàn)PCI 總線和本地總線之間的連接。PCI總線協(xié)議接口芯片9052為各類適配卡提供高性能的PCI總線接口,可以將PCI總線同各種傳輸速率低于132Mb/s的本地總線進(jìn)行連接。采用PCI總線協(xié)議接口芯片9052來實(shí)現(xiàn)PCI總線和本地總線之間的連接,如圖3所示。

由于9052是專門的PCI協(xié)議芯片,所以它的PCI端可以直接通過插卡上的引線和PCI插槽連接。二者連接時不用做任何變換,將二者的復(fù)用數(shù)據(jù)線和地址線直接連通,將9052的PCI端的控制線與PCI插槽上的作為從設(shè)備的控制線直接連通即可。

9052芯片本地端接口和FPGA芯片的連接也就是PCI總線接口和測試卡本地總線的連接,是本接口卡設(shè)計(jì)的一個關(guān)鍵。在FPGA芯片的邏輯設(shè)計(jì)中,根據(jù)測試卡對主機(jī)系統(tǒng)資源的需求,提供了一個測試卡本地總線接口。本地總線接口包括4K字節(jié)的存儲器和16字節(jié)的寄存器,所以將要使用9052芯片的兩個地址空間分別設(shè)置為4K字節(jié)和16字節(jié),將存儲器和寄存器空間分開。在地址線和數(shù)據(jù)線的設(shè)計(jì)上,采用地址線和數(shù)據(jù)線非復(fù)用模式,本地的地址線和數(shù)據(jù)線分別與9052本地端的地址線和數(shù)據(jù)線連接。在控制線的設(shè)計(jì)上,根據(jù)二者的讀寫時序,將9052芯片設(shè)置為直接讀寫的方式,用9052芯片的讀信號和寫信號直接驅(qū)動本地總線的讀寫信號。另外還要使用9052芯片提供的一個片選信號,來選擇不同的16個字節(jié)的寄存器地址空間。9052本地端和BU-61580要采用同一個時鐘信號,以保證二者讀寫時序的同步。

3.4 測試卡軟件接口的設(shè)計(jì)

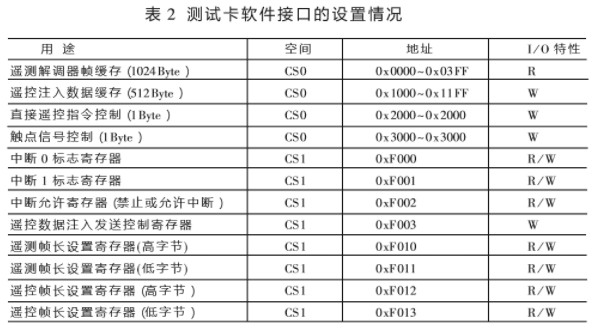

測試用戶需要對測試卡進(jìn)行軟件設(shè)置,來實(shí)現(xiàn)遙控注入數(shù)據(jù)、遙測和遙控幀長、遙控?cái)?shù)據(jù)發(fā)送等。這些軟件接口是通過FPGA芯片進(jìn)行邏輯設(shè)計(jì)來提供的。測試卡加電后,這些軟件接口就存在于測試卡上,通過軟件編程可以控制軟件接口,來實(shí)現(xiàn)測試卡的測試工作。測試卡實(shí)現(xiàn)的軟件接口如表2所示。

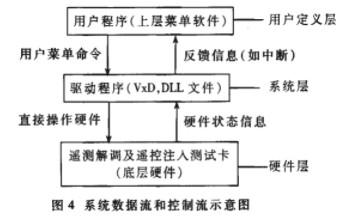

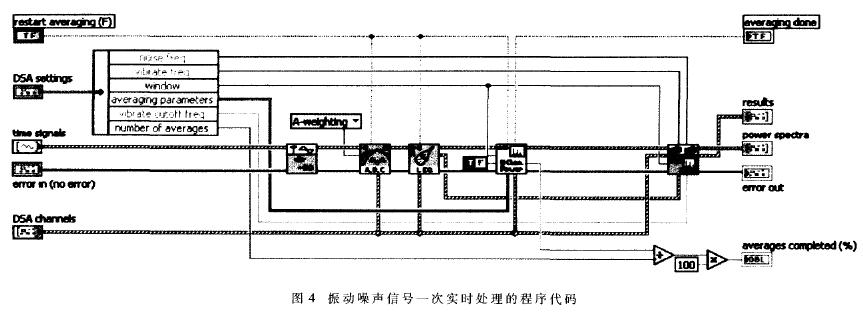

4 測試卡與其配套軟件的數(shù)據(jù)流和控制流

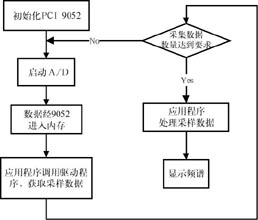

遙測解調(diào)及遙控注入測試卡要和其配套的軟件接口卡驅(qū)動程序(VxD)及用戶菜單應(yīng)用軟件共同使用。遙測解調(diào)及遙控注入測試卡作為硬件BIU同被測測控系統(tǒng)連接,負(fù)責(zé)接收與發(fā)送各類測試數(shù)據(jù),并且可以由主機(jī)來配置測試卡上的寄存器。驅(qū)動程序則作為遙測解調(diào)及遙控注入測試卡和用戶菜單軟件的接口程序,負(fù)責(zé)接收菜單軟件的命令,并依據(jù)此命令來操作硬件,或者向菜單軟件報告總線適配器的工作情況(如通知中斷已經(jīng)產(chǎn)生以及告知中斷原因),包括安裝信息文件(INF)、虛擬設(shè)備驅(qū)動程序(VxD)、接口函數(shù)文件(DLL)三個組成部分。菜單軟件作為用戶界面程序接收用戶的輸入,并以可視的方式將結(jié)果數(shù)據(jù)反饋。遙測解調(diào)及遙控注入測試卡與處理器之間所構(gòu)成系統(tǒng)的數(shù)據(jù)流和控制流如圖4所示。

責(zé)任編輯:gt

電子發(fā)燒友App

電子發(fā)燒友App

評論