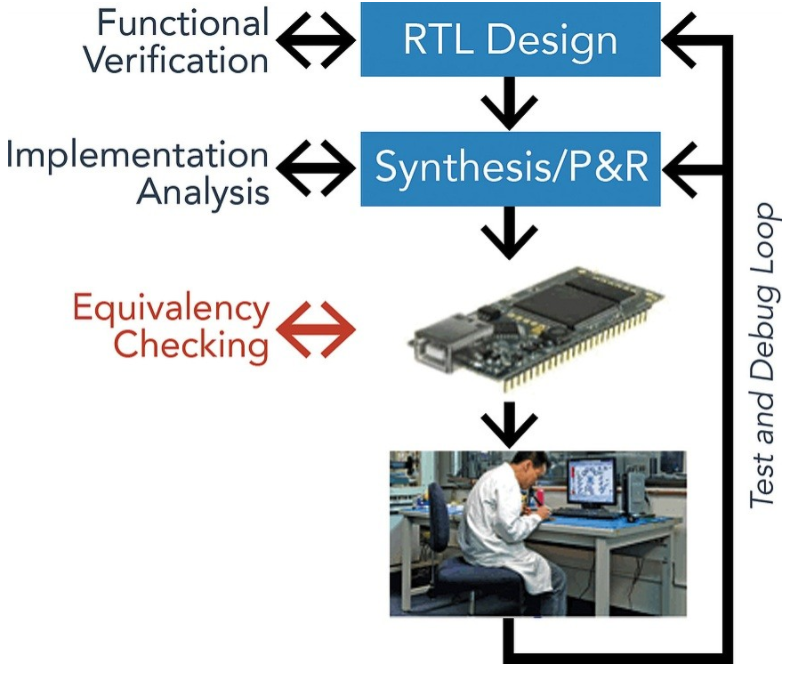

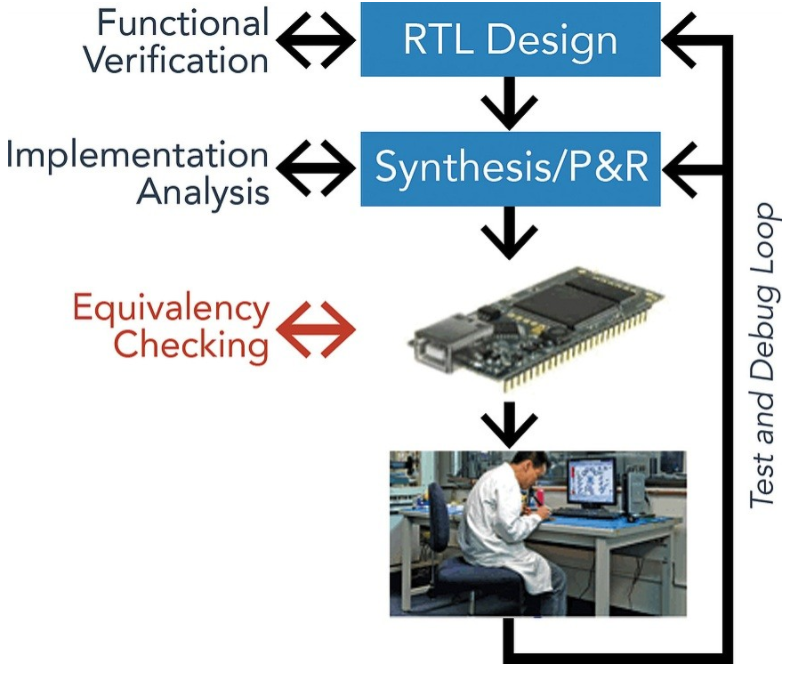

什么是FPGA原型?? FPGA原型設(shè)計(jì)是一種成熟的技術(shù),用于通過將RTL移植到現(xiàn)場可編程門陣列(FPGA)來驗(yàn)證專門應(yīng)用的集成電路(ASIC),專用標(biāo)準(zhǔn)產(chǎn)品(ASSP)和片上系統(tǒng)(SoC)的功能

2022-07-19 16:27:29 1736

1736 ,然后通過外部物理連接回環(huán)TX-->RX測試誤碼率來驗(yàn)證鏈路的信號完整性,所以我想進(jìn)行如下測試:

? ? ? ? 測試路徑: FPGA --> DSP SRIO SerDes ?-->

2018-06-21 06:25:29

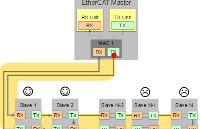

的實(shí)時性能和拓?fù)涞撵`活性樹立了新的標(biāo)準(zhǔn),同時,它還符合甚至降低了現(xiàn)場總線的使用成本。EtherCAT的特點(diǎn)還包括高精度設(shè)備同步,可選線纜冗余,和功能性安全協(xié)議(SIL3)。

2016-01-16 08:52:19

EtherCAT的原理是什么?EtherCAT有哪些功能?怎樣去實(shí)現(xiàn)EtherCAT的應(yīng)用層?EtherCAT有哪些應(yīng)用實(shí)例?

2021-07-02 06:52:14

各位大佬,我想問一下怎么用FPGA驗(yàn)證偽隨機(jī)數(shù)發(fā)生器呀,都有哪些步驟呀,有知道了回答一下,謝謝了

2018-11-29 19:56:52

FPGA原型驗(yàn)證已是當(dāng)前原型驗(yàn)證的主流且成熟的芯片驗(yàn)證方法——它通過將RTL移植到現(xiàn)場可編程門陣列(FPGA)來驗(yàn)證ASIC的功能,并在芯片的基本功能驗(yàn)證通過后就可以開始驅(qū)動的開發(fā),一直到芯片

2020-08-21 05:00:12

FPGA按下圖做的菊花鏈的電路連接,FPGA為spartan3E XC2S250E,PROM為18v02,但下載時initialize chain識別不到三個器件,只顯示一個但也下載不了,根據(jù)大家的經(jīng)驗(yàn),可能是什么原因呢?下載方式不對?還是什么的?請大家多多指教啊!謝謝啦!

2014-05-08 23:01:27

FPGA設(shè)計(jì)驗(yàn)證關(guān)鍵要點(diǎn)不同于ASIC設(shè)計(jì),FPGA設(shè)計(jì)中的標(biāo)準(zhǔn)元件或客制化實(shí)作,一般欠缺大量的資源及準(zhǔn)備措施可用于設(shè)計(jì)驗(yàn)證。由于可以重新程式化元件,更多時候驗(yàn)證只是事后的想法。本文將探討在FPGA

2010-05-21 20:32:24

時序仿真的重要性是什么傳統(tǒng)的FPGA驗(yàn)證方法是什么FPGA設(shè)計(jì)的驗(yàn)證技術(shù)及應(yīng)用原則是什么

2021-05-08 09:05:32

AD9361 BIST功能驗(yàn)證相關(guān)事項(xiàng)想請問各位大拿,AD9361 BIST功能驗(yàn)證是用于驗(yàn)證收發(fā)通道的鏈路部分,而數(shù)據(jù)接口部分是不是驗(yàn)證不到?當(dāng)前調(diào)試過程中出現(xiàn)的問題是:配置模式FDD 1R1T

2021-09-14 22:29:00

不用再花費(fèi)大量時間等待生成BIT文件下載到FPGA才能實(shí)際驗(yàn)證。下面我們以簡單的QPSK調(diào)制解調(diào)為例,為大家展示AD9361+Simulink是如何快速搭建鏈路并實(shí)時仿真的。首先我們在simulink

2016-11-25 17:38:07

...............................................11.2 FPGA 驗(yàn)證技術(shù)...............................................31.3 Altera

2015-09-18 15:26:25

ASIC設(shè)計(jì)-FPGA原型驗(yàn)證

2020-03-19 16:15:49

安全引導(dǎo)和安全調(diào)試是CryptoCell(CC)引導(dǎo)服務(wù)的基本功能。

安全引導(dǎo)和安全調(diào)試基于使用RSA私鑰和公鑰方案的證書鏈機(jī)制。

本教程介紹安全引導(dǎo)和安全調(diào)試證書鏈的定義、生成和驗(yàn)證。

它還描述了

2023-08-24 06:09:48

優(yōu)異特性,在不需要再生的情況下,可以遠(yuǎn)距離傳輸大量數(shù)據(jù)、聲音和視頻信號。隨著飛機(jī)和船舶的電子系統(tǒng)日益復(fù)雜,重量和空間變得十分重要。以其重量輕、體積小的光纖系統(tǒng)變得更加有吸引力。光纖鏈路還有其他幾個優(yōu)點(diǎn)

2018-07-03 10:13:09

動態(tài)均衡技術(shù),在spec中被稱作“Link Equalizati on”(鏈路均衡,簡稱為LEQ)。本文理論篇主要介紹PCIe 3.0/4.0的鏈路均衡的工作原理。

2020-11-25 06:19:43

接收端鏈路均衡測試(Rx LEQ)進(jìn)入環(huán)回模式進(jìn)行誤碼率測試

2020-12-02 06:49:35

各位大神,小弟做FPGA不久,最近設(shè)計(jì)了一個XC3S1500的FPGA板子,經(jīng)測試電源供電沒問題,但是JTAG鏈路建立不起來,初步懷疑是FPGA芯片和配置芯片(XCF08P)的VCCO不一致

2013-04-03 16:30:12

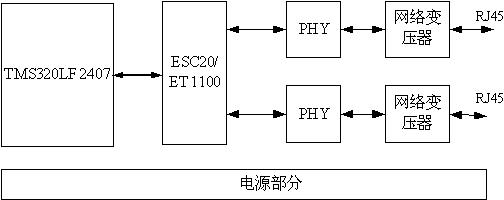

項(xiàng)目名稱:基于FPGA的EtherCAT通訊試用計(jì)劃:本人正在學(xué)習(xí)和研究基于FPGA的EtherCAT通訊模塊,目前采用的是altera的CycloneV系列的FPGA,想通過國產(chǎn)的FPGA來嘗試

2019-06-03 16:02:36

EtherCAT是什么?EtherCAT有何特點(diǎn)?EtherCAT的基本原理是什么?EtherCAT系統(tǒng)是由哪些部分組成的?

2021-09-02 06:23:22

鏈路預(yù)算表用于計(jì)算Maxim工業(yè)、科學(xué)與醫(yī)療無線頻段(ISM-RF)產(chǎn)品(Tx、Rx、TRx)的鏈路性能,估算特定的射頻電路在幾種環(huán)境下的通信覆蓋范圍和鏈路裕量。該Excel?表格還可用于估算100MHz至10GHz載頻范圍的其它射頻系統(tǒng)的鏈路裕量。

2019-08-22 07:00:30

,EtherCAT硬件將環(huán)回EtherCAT數(shù)據(jù)幀。請查看TI的TLK1xx以太網(wǎng)PHY收發(fā)器系列,這個系列的器件支持快速鏈路斷開特性。在EtherCAT中使用ASIC或FPGA會增加成本和電路板面積。一

2018-09-06 15:25:39

使用Keysight E5910A串行鏈路優(yōu)化工具測試和優(yōu)化高速串行鏈路

2019-10-15 08:49:27

一、概述隨著通訊網(wǎng)絡(luò)和技術(shù)的飛速發(fā)展,通信網(wǎng)絡(luò)運(yùn)營商已經(jīng)從單純注重業(yè)務(wù)的提供,轉(zhuǎn)向更加注重網(wǎng)絡(luò)可靠和業(yè)務(wù)的快速恢復(fù),從而提高了對光傳送網(wǎng)保護(hù)能力的要求。光鏈路實(shí)時監(jiān)測倒換

2009-12-02 09:50:10

明德?lián)P已經(jīng)實(shí)現(xiàn)基于FPGA的Ethercat協(xié)議棧,技術(shù)指標(biāo)達(dá)到國內(nèi)一流水平:最小周期為125us,抖動小于80ns,最大可以同步接入32個伺服驅(qū)動器。

2018-05-29 09:42:07

隨著SoC設(shè)計(jì)上的混合信號組件數(shù)量增加了,基本的功能驗(yàn)證對于硅初期能否成功也愈來愈重要。FPGA在系統(tǒng)整合難題上加入了一個新特點(diǎn)。在核心上,此新范例-可編程系統(tǒng)單芯片(programmable

2011-10-16 22:55:10

FPGA在視頻處理方面可能很有用處,但在驗(yàn)證基于FPGA的視頻系統(tǒng)時,則需要仔細(xì)關(guān)注您所用的方法。

2019-07-23 06:36:45

但是,如果FPGA通過接口與DSP核心連接,并且高速視頻數(shù)據(jù)是通過它來傳輸,那么它根本不是簡單的系統(tǒng)。這種更高的設(shè)計(jì)復(fù)雜度導(dǎo)致了額外的驗(yàn)證難題,并且如果您在設(shè)計(jì)階段晚期發(fā)現(xiàn)一處重大錯誤,那么這還會導(dǎo)致高成本的系統(tǒng)板重制。為了消除這一隱患,您必須仔細(xì)考慮自己采用的驗(yàn)證方法,以便降低重制風(fēng)險。

2019-09-19 06:00:59

輸入的準(zhǔn)確性,其次不用再花費(fèi)大量時間等待生成BIT文件下載到FPGA才能實(shí)際驗(yàn)證。 下面我們以簡單的QPSK調(diào)制解調(diào)為例,為大家展示AD9361+Simulink是如何快速搭建鏈路并實(shí)時仿真的。首先我們

2019-02-19 10:52:13

基于賽靈思的FPGA的EtherCAT主站總線控制 ,論壇有做運(yùn)動控制這方面的技術(shù)嗎?目前我已實(shí)現(xiàn)帶32軸同步運(yùn)行,同步抖動±75ns,控制精度125us。感興趣的可以一起探討下

2018-07-23 12:00:39

了確定性延遲,確定包含德州儀器 (TI) LM97937 ADC 和 Xilinx Kintex 7 FPGA 的系統(tǒng)的鏈路延遲。主要特色保證 JESD204B 鏈路中的確定性延遲理解鏈路延遲與鏈路

2018-11-21 16:51:43

1 鏈路預(yù)算 上行和下行鏈路都有自己的發(fā)射功率損耗和路徑衰落。在蜂窩通信中,為了確定有效覆蓋范圍,必須確定最大路徑衰落、或其他限制因數(shù)。在上行鏈路,從移動臺到基站的限制因數(shù)是基站的接受靈敏度。對下行

2019-06-12 08:27:32

為了縮短卷積編碼器設(shè)計(jì)周期,使硬件設(shè)計(jì)更具靈活性,在介紹卷積編碼器原理的基礎(chǔ)上,論述了一種基于可編程邏輯器件,采用模塊化設(shè)計(jì)方法,利用VHDL硬件描述語言實(shí)現(xiàn)CDMA2000系統(tǒng)前向鏈路卷積編碼器

2019-08-27 07:41:05

EtherCAT技術(shù)組 (ETG) 框架之下,而EtherCAT技術(shù)組是一個由大約2600家成員公司組成的工業(yè)現(xiàn)場總線組織。EtherCAT常見于工廠自動化、半導(dǎo)體工具、包裝機(jī)器人技術(shù)以及其它應(yīng)用領(lǐng)域。我

2022-11-18 06:44:42

CANOPEN轉(zhuǎn)EtherCAT協(xié)議轉(zhuǎn)換網(wǎng)關(guān)是一款能夠?qū)ANOPEN接口設(shè)備連接到EtherCAT網(wǎng)絡(luò)系統(tǒng)的產(chǎn)品。該網(wǎng)關(guān)作為EtherCAT網(wǎng)絡(luò)的從站,可以將CANOPEN設(shè)備集成到

2023-12-12 11:31:03

的基站上行鏈路和下行鏈路生成波形。請幫忙。問候。 以上來自于谷歌翻譯 以下為原文Hi, I am playing with Agilent Signal Studio

2019-01-23 15:11:42

信號接收器系統(tǒng)的設(shè)計(jì)師常常需要進(jìn)行系統(tǒng)性能的級聯(lián)鏈路分析(從天線一直到ADC)。在鏈路分析中,噪聲是一個至關(guān)重要的參數(shù),它限制了接收器的總體靈敏度。對系統(tǒng)拓?fù)浣Y(jié)構(gòu)來說更加重要,原因是拓?fù)浣Y(jié)構(gòu)的選擇

2019-10-18 07:46:34

PRU-ICSS 固件支持的八個現(xiàn)場總線存儲器管理單元 (FMMU) 和同步管理器 (SM)用于環(huán)路控制的增強(qiáng)型鏈路丟失檢測功能這消除了與外部存儲器訪問相關(guān)的延遲,有助于提升系統(tǒng)性能

2018-10-16 10:43:09

本文考慮了系統(tǒng)的綜合要求:系統(tǒng)容量、作用距離、收發(fā)時延及算法實(shí)現(xiàn)復(fù)雜度,采用了8倍圖像壓縮、RS編碼加交織的方式進(jìn)行了無線鏈路的設(shè)計(jì),采用大規(guī)模FPGA完成發(fā)送端及接收端的算法實(shí)現(xiàn),并通過試驗(yàn)驗(yàn)證設(shè)計(jì)指標(biāo)滿足系統(tǒng)要求。

2021-05-31 07:00:51

無線鏈路的作用就是將來自模擬信源的信息經(jīng)過一個模擬無線傳輸信道傳到模擬信宿,信息的數(shù)字化僅僅是為了增加鏈路的可靠性。比如語音編碼就是模擬信號數(shù)字化的一個典例。下圖1.1,1.2描述的是一個具體

2021-02-02 16:46:17

作者:John Johnson,德州儀器 本文介紹時鐘抖動對高速鏈路性能的影響。我們將重點(diǎn)介紹抖動預(yù)算基礎(chǔ)。 用于在更遠(yuǎn)距離對日益增長的海量數(shù)據(jù)進(jìn)行傳輸?shù)囊恍?biāo)準(zhǔn)不斷出現(xiàn)。來自各行業(yè)的工程師們組成

2018-09-19 14:23:47

本文介紹時鐘抖動對高速鏈路性能的影響。我們將重點(diǎn)介紹抖動預(yù)算基礎(chǔ)。 用于在更遠(yuǎn)距離對日益增長的海量數(shù)據(jù)進(jìn)行傳輸?shù)囊恍?biāo)準(zhǔn)不斷出現(xiàn)。來自各行業(yè)的工程師們組成了各種委員會和標(biāo)準(zhǔn)機(jī)構(gòu),根據(jù)其開發(fā)標(biāo)準(zhǔn)的目標(biāo)

2022-11-23 06:59:24

team:1.team也是鏈路聚合的一種方式a.最多支持八塊網(wǎng)卡b.支持模式:廣播、輪詢、主備、負(fù)載均衡

2019-07-12 07:03:36

用于Xilinx FPGA的Keysight E5910A串行鏈路優(yōu)化工具

2019-10-16 10:49:30

,兩個Bitwave 54M的產(chǎn)品進(jìn)行聚合測試,前后兩次均達(dá)到了一條無線聯(lián)路帶寬的2倍, 為了驗(yàn)證聚合不同帶寬聯(lián)路 的能力,我們使用了一條11M無線鏈路再加上一條54M的無線鏈路,交換機(jī)在經(jīng)過不到10

2010-03-18 12:51:36

在紅外線的增強(qiáng)處理中,怎么用quartusII進(jìn)行算法的實(shí)現(xiàn)及其仿真驗(yàn)證,重點(diǎn)是直方圖算法,這里面的代碼是什么。

2015-05-06 23:01:22

缺陷成團(tuán)對FPGA片內(nèi)冗余容錯電路可靠性的影響是什么?缺陷成團(tuán)對冗余容錯電路可靠性的影響是什么?

2021-04-08 06:50:18

本帖最后由 eehome 于 2013-1-5 10:01 編輯

EDA先鋒工作室的精品書籍,國內(nèi)少有的系統(tǒng)講述FPGA設(shè)計(jì)和驗(yàn)證的好書,特別是驗(yàn)證部分很精華,現(xiàn)在和大家分享,同時附上本書的實(shí)例源代碼和Verilog HDL語法國際標(biāo)準(zhǔn)。

2011-08-02 14:54:41

gprs模塊的鏈路是個什么概念啊 ???

2019-04-16 03:31:39

請問如何排除無線電鏈路故障?

2021-06-17 11:17:16

射頻鏈路設(shè)計(jì)一般用的什么軟件,可以仿真鏈路參數(shù)的那種。

2018-12-05 23:57:51

我在FPGA開發(fā)板上可以建立鏈路,能夠抓到204這邊的波形。但是在AD9164那邊的軟件上的寄存器顯示的是沒有建立鏈路。請問這是怎么回事?另外是否能夠提供示例設(shè)計(jì)。萬分感謝!

2019-02-15 08:58:29

采用modbus的串口鏈路,這3個設(shè)備公用一條鏈路,該如何設(shè)設(shè)置?有一個主控屏,一臺pc上位機(jī),和一個受控設(shè)備.PC遠(yuǎn)控端,屏近地控制

2023-05-05 16:17:00

高級數(shù)據(jù)鏈路控制涉及三種類型的站,即主站、從站和復(fù)合站。 主站的主要功能是發(fā)送命令(包括數(shù)據(jù)信息)幀、接收響應(yīng)幀,并負(fù)責(zé)對整個鏈路的控制系統(tǒng)的初啟、流程的控制、差錯檢測或恢復(fù)等。

2019-11-01 09:10:17

高速串行鏈路系統(tǒng)對信號的影響是什么?常用的補(bǔ)償技術(shù)有哪些?

2021-06-10 06:20:34

。基于FPGA的原型驗(yàn)證方法憑借其速度快、易修改、真實(shí)性的特點(diǎn),已經(jīng)成為ASIC芯片設(shè)計(jì)中重要的驗(yàn)證方法。本文主要描述高頻RFID芯片的FPGA原型驗(yàn)證平臺的設(shè)計(jì),并給出驗(yàn)證結(jié)果。1、RFID芯片的FPGA

2019-05-29 08:03:31

闡述H.264/AVC 二進(jìn)制算術(shù)編碼的原理,論述此編碼的IP 核設(shè)計(jì)方案及其FPGA 驗(yàn)證。整個設(shè)計(jì)使用VerilogHDL 語言描述,在 ALDEC 的Active_HDL6.2 平臺上進(jìn)行時序仿真,在 Synplicity 的Synplify7.0平

2009-09-03 09:11:20 25

25 FPGA驗(yàn)證是基于VHDL的VLSI設(shè)計(jì)中非常重要的一個環(huán)節(jié)。用戶設(shè)計(jì)的電子系統(tǒng)首先必須是可綜合的,綜合之后再通過FPGA原型驗(yàn)證,即可在物理層面對用戶設(shè)計(jì)完成實(shí)物驗(yàn)證。通過FPGA驗(yàn)證

2010-07-12 19:13:59 28

28

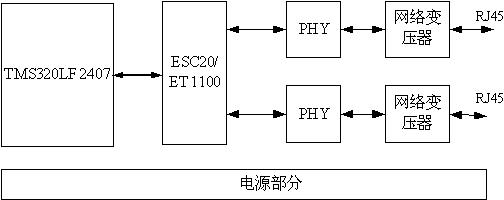

工業(yè)以太網(wǎng)EtherCAT技術(shù)的原理及其實(shí)現(xiàn)

一、引言

2009-07-24 16:24:24 5141

5141

該方案采用Altera公司的IP核和Cyclone系列FPGA,建立了串行RapidIO(SRIO)接口通信系統(tǒng),并對其功能進(jìn)行驗(yàn)證。詳細(xì)分析了RapidIO應(yīng)用系統(tǒng)及其驗(yàn)證模型的功能結(jié)構(gòu)和運(yùn)行原理,為提高嵌入式

2011-12-23 14:47:22 38

38 第一編 驗(yàn)證的重要性 驗(yàn)證,顧名思義就是通過仿真、時序分析、上板調(diào)試等手段檢驗(yàn)設(shè)計(jì)正確性的過程,在 FPGA / IC 開發(fā)流程中,驗(yàn)證主要包括功能驗(yàn)證和時序驗(yàn)證兩個部分。為了了解

2012-05-18 11:50:21 7664

7664 壓縮感知的冗余字典及其迭代軟閾值實(shí)現(xiàn)算法_趙慧民

2017-01-07 16:52:06 1

1 狀態(tài)機(jī),并通過解析各階段數(shù)據(jù)狀態(tài)變化,驗(yàn)證了各節(jié)點(diǎn)通信數(shù)據(jù)的正確性。實(shí)驗(yàn)結(jié)果表明,基于上述狀態(tài)機(jī)的FPGA實(shí)現(xiàn)EtherCAT從站基本通信鏈路是完全可行的。

2017-11-15 12:04:01 17164

17164

設(shè)計(jì)了一種基于FPGA的驗(yàn)證平臺及有效的SoC驗(yàn)證方法,介紹了此FPGA驗(yàn)證軟硬件平臺及軟硬件協(xié)同驗(yàn)證架構(gòu),討論和分析了利用FPGA軟硬件協(xié)同系統(tǒng)驗(yàn)證SoC系統(tǒng)的過程和方法。利用此軟硬件協(xié)同驗(yàn)證

2017-11-17 03:06:01 13139

13139

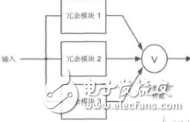

基于SRAM 的FPGA對于空間粒子輻射非常敏感,很容易產(chǎn)生軟故障,所以對基于FPGA的電子系統(tǒng)采取容錯措施以防止此類故障的出現(xiàn)非常重要。通過對敏感電路使用三模冗余( TMR)方法并利用FPGA 的動態(tài)可重構(gòu)特性,可以有效的增強(qiáng)FPGA 的抗單粒子性能,解決FPGA對因空間粒子輻射而形成的軟故障。

2017-11-18 11:40:02 10826

10826

FPGA設(shè)計(jì)和驗(yàn)證工程師當(dāng)今面臨的最大挑戰(zhàn)之一是時間和資源制約。隨著FPGA在速度、密度和復(fù)雜性方面的增加,完成一個完整時序驗(yàn)證對人力和計(jì)算機(jī)處理器、存儲器提出了更多更高的要求。 隨著FPGA器件

2019-10-06 17:57:00 953

953

介紹了循環(huán)冗余校驗(yàn)(CRC)編碼器的設(shè)計(jì)及FPGA實(shí)現(xiàn)過程,采用原理圖輸入法對整個系統(tǒng)進(jìn)行了編譯和仿真,并在芯片EPlK30TCl44-3中對該設(shè)計(jì)的核心部分進(jìn)行了測試驗(yàn)證。結(jié)果表明,試驗(yàn)數(shù)據(jù)與理論分析結(jié)果完全相符。

2021-02-05 17:00:00 19

19 介紹了一種雙接口NFC芯片的架構(gòu)和功能,提岀并實(shí)現(xiàn)了用于該雙接口NFC芯片的FPGA驗(yàn)證系統(tǒng)及其驗(yàn)證流程。該FPGA驗(yàn)證系統(tǒng)包括FPGA、PIC單片機(jī)以及帶NFC功能的手機(jī),可有效縮短芯片設(shè)計(jì)周期

2021-05-26 14:03:26 16

16 隨著 FPGA 變得越來越大和越來越復(fù)雜,它們的設(shè)計(jì)和功能驗(yàn)證趨向于 ASIC。在現(xiàn)代 FPGA 設(shè)計(jì)流程的先進(jìn)性的推動下,這種趨勢現(xiàn)在正在擴(kuò)展到實(shí)現(xiàn)驗(yàn)證領(lǐng)域。EC 現(xiàn)在是該流程的必要組成部分,保留了 FPGA 生產(chǎn)過程中的固有效率。

2022-06-14 09:21:55 1081

1081

在現(xiàn)代SoC芯片驗(yàn)證過程中,不可避免的都會使用FPGA原型驗(yàn)證,或許原型驗(yàn)證一詞對你而言非常新鮮,但是FPGA上板驗(yàn)證應(yīng)該是非常熟悉的場景了。

2023-03-28 09:33:16 854

854 我們當(dāng)然希望在項(xiàng)目中盡快準(zhǔn)備好基于FPGA原型驗(yàn)證的代碼,以便最大限度地為軟件團(tuán)隊(duì)和RTL驗(yàn)證人員帶來更客觀的收益。

2023-05-30 11:10:27 769

769

在現(xiàn)代SoC芯片驗(yàn)證過程中,不可避免的都會使用FPGA原型驗(yàn)證,或許原型驗(yàn)證一詞對你而言非常新鮮,但是FPGA上板驗(yàn)證應(yīng)該是非常熟悉的場景了。

2023-05-30 15:04:06 905

905

憑借大量的EtherCAT客戶現(xiàn)場應(yīng)用經(jīng)驗(yàn)和客戶實(shí)地測試,acontis EtherCAT主站可以通過使用兩個獨(dú)立網(wǎng)卡支持線纜冗余功能。

2023-04-14 14:56:10 707

707

很多其他行業(yè)也能從電子器件的增加受益,當(dāng)然保障功能安全是大的前提。本文討論SOC芯片設(shè)計(jì)驗(yàn)證、驗(yàn)證計(jì)劃和策略以及驗(yàn)證方法。它定義了功能模擬、功能覆蓋、代碼覆蓋以及設(shè)計(jì)驗(yàn)證中使用的重要術(shù)語。本文還涉及FPGA驗(yàn)證及其在S

2023-07-20 09:05:59 597

597 什么是線纜冗余 EtherCAT冗余技術(shù)如何實(shí)現(xiàn)通信線纜斷開的補(bǔ)救? 線纜冗余是指在工業(yè)自動化領(lǐng)域中,通過在通信線纜中引入冗余連接,以提高系統(tǒng)的可靠性和容錯性。其中,EtherCAT(以太網(wǎng)控制

2024-02-06 10:16:39 1281

1281 現(xiàn)場總線技術(shù)是自動化控制領(lǐng)域發(fā)展的熱點(diǎn),應(yīng)用于多個設(shè)備間的實(shí)時通信,在設(shè)備連接中,若某一處線纜發(fā)生斷線將影響到設(shè)備間的通信。一起看看EtherCAT冗余技術(shù)是如何實(shí)現(xiàn)對通信線纜斷線時進(jìn)行補(bǔ)救與鎖定

2024-02-19 12:11:44 311

311

FPGA驗(yàn)證和UVM驗(yàn)證在芯片設(shè)計(jì)和驗(yàn)證過程中都扮演著重要的角色,但它們之間存在明顯的區(qū)別。

2024-03-15 15:00:41 94

94 FPGA原型驗(yàn)證流程是確保FPGA(現(xiàn)場可編程門陣列)設(shè)計(jì)正確性和功能性的關(guān)鍵步驟。它涵蓋了從設(shè)計(jì)實(shí)現(xiàn)到功能驗(yàn)證的整個過程,是FPGA開發(fā)流程中不可或缺的一環(huán)。

2024-03-15 15:05:33 97

97

電子發(fā)燒友App

電子發(fā)燒友App

評論