引言

隨著電子技術(shù)的不斷發(fā)展,數(shù)據(jù)的傳輸速度越來(lái)越快,高速時(shí)鐘的應(yīng)用日益廣泛,如何保證時(shí)鐘在高速跳變過(guò)程中的信號(hào)完整性、抖動(dòng)、功耗等問(wèn)題,已逐漸成為關(guān)注的問(wèn)題。傳統(tǒng)的時(shí)鐘設(shè)計(jì)方法大多依靠經(jīng)驗(yàn)和理論計(jì)算,但是隨著時(shí)鐘頻率越來(lái)越高,時(shí)鐘的電磁環(huán)境日趨復(fù)雜,時(shí)鐘的傳輸線效應(yīng)、過(guò)沖/欠沖、反射、振鈴效應(yīng)、趨膚效應(yīng)都成為影響時(shí)鐘設(shè)計(jì)的關(guān)鍵因素,只有使用現(xiàn)代科技手段,利用計(jì)算機(jī)的強(qiáng)大計(jì)算能力進(jìn)行仿真才能夠保證時(shí)鐘電路設(shè)計(jì)成功。 HyperLynx是Mentor(GraphICS開(kāi)發(fā)的一款板級(jí)信號(hào)完整性的仿真工具。它可以進(jìn)行損耗傳輸線的精確仿真,支持IBIS模型和HSPICE模型,可以使用過(guò)孔模型,允許多種激勵(lì)源,可以分析信號(hào)的眼圖、抖動(dòng)以及EMC(電磁兼容性)輻射,用戶界面簡(jiǎn)單直觀。

在目前的高速時(shí)鐘的電平標(biāo)準(zhǔn)中,PECL(正電壓射極耦合邏輯)是應(yīng)用較廣泛的一種,絕大多數(shù)高速ADC(A/D轉(zhuǎn)換器)、DAC(D/A轉(zhuǎn)換器)器件都支持這一時(shí)鐘電平。本文敘述。PECL的原理和常見(jiàn)端接方式,結(jié)合在ADc系統(tǒng)中的應(yīng)用,使用HyperLynx工具對(duì)設(shè)計(jì)后的電路進(jìn)行仿真以驗(yàn)證設(shè)計(jì)思想。

l PECL工作原理

PECL由EcL(射極耦合邏輯)標(biāo)準(zhǔn)發(fā)展而來(lái),在PECL電路中省去了負(fù)電源,較EcL電路更便于使用。PECL信號(hào)的擺幅相對(duì)EcL要小,欲了解更多信息請(qǐng)登錄電子發(fā)燒友網(wǎng)(http://www.nxhydt.com),這使得該邏輯更適合于高速數(shù)據(jù)的串行或并行連接。

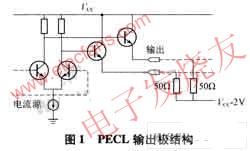

一個(gè)標(biāo)準(zhǔn)的PECL輸出極如圖1所示。

差分對(duì)管的射極通過(guò)電流源連接到地,差分對(duì)管驅(qū)動(dòng)一對(duì)射隨器以提供正、負(fù)輸出。輸出射隨器工作在正電源范圍內(nèi),其電流始終存在,這樣有利于提高開(kāi)關(guān)速度。LVPECL(低電壓。PECL)輸出極的標(biāo)準(zhǔn)輸出負(fù)載是接50 Ω電阻至 Vcc一2 V的電平,在這種負(fù)載條件下,由于射隨器的基極一射極有0.7 V壓降,故輸出+與輸出一的靜態(tài)電平典型值為Vcc一1.3 V,0.7 V壓降加在50 Ω終端電阻上的電流為14 mA,可知輸出+與輸出一電流為14 mA。PECL結(jié)構(gòu)的輸出阻抗典型值為4 Ω~5 Ω,表明它有很強(qiáng)的驅(qū)動(dòng)能力。

2時(shí)鐘電路設(shè)計(jì)

下面根據(jù)具體應(yīng)用進(jìn)行設(shè)計(jì)。首先從時(shí)鐘的發(fā)送端(輸出)和接收端(輸入)各自的特性著手進(jìn)行設(shè)計(jì)。

2.1時(shí)鐘輸出結(jié)構(gòu)

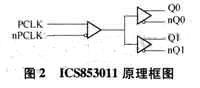

時(shí)鐘輸出端由時(shí)鐘扇出芯片ICS853011的一對(duì)輸出引腳擔(dān)任。ICS853011是一款將任意差分時(shí)鐘扇出為兩路PEcL電平的時(shí)鐘扇出芯片,其原理見(jiàn)圖2。

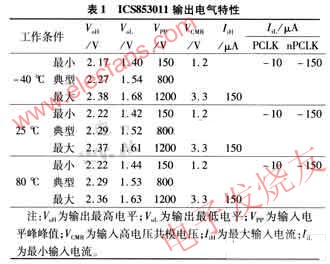

當(dāng)其供電電壓為3.3 V時(shí),其輸出電氣特性如表l所示,輸出高電平在2.295 V左右,輸出低電平在1.52 V左右,輸出峰峰值約為800 mV。

2.2時(shí)鐘輸入結(jié)構(gòu)

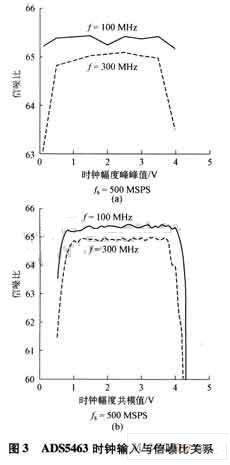

ADS5463的時(shí)鐘輸入特性如圖3所示。

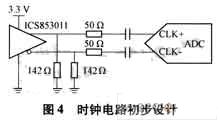

由圖3可看出時(shí)鐘的輸入幅度和共模電壓與ADC信噪比的關(guān)系,當(dāng)輸入時(shí)鐘為300 MHz時(shí),只有峰峰值大于O.5 V、小于3.5 V,共模電壓大于1 V、小于3.5 V才有最佳的信噪比指標(biāo),LVPECL電平的共模電壓為Vcc一1.3 V="3".3 V-1.3 V="2" V,典型峰峰值700 mV,剛好滿足ADS5463對(duì)時(shí)鐘的要求。ADS5463在時(shí)鐘輸入端由內(nèi)部電阻將時(shí)鐘輸人共模電壓偏置到2.4 V,這與發(fā)送端的共模電壓不同,故采用交流耦合是最好的方式。時(shí)鐘電路初步設(shè)計(jì)見(jiàn)圖4。

如圖4所示,在ICS8530ll的每個(gè)輸出端都并聯(lián)了一個(gè)142 Ω的電阻到地,這個(gè)電阻的作用是:由于輸出共模電壓固定在Vcc一1.3 V="2" V,為了使輸出電流維持在14 mA,故直流偏置電阻值選擇2 V/14 mA="142" Ω,實(shí)際選取時(shí)可選擇140~200 Ω。此時(shí)雙端傳輸線特性阻抗為50 Ω。

3電路仿真

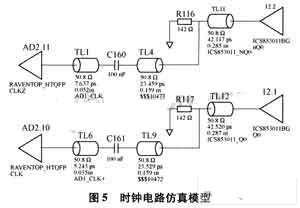

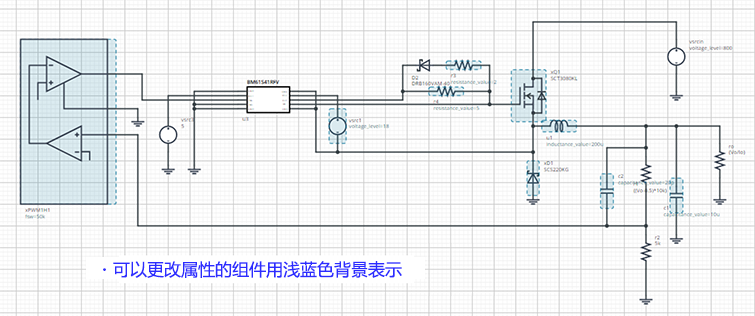

下面打開(kāi)HyperLynx,將上述電路導(dǎo)入其中的LineSim工具下,該工具是HyperLynx的一個(gè)子工具,主要用來(lái)進(jìn)行傳輸線的拓?fù)浣Y(jié)構(gòu)的仿真,可以對(duì)不同端接方式下的信號(hào)完整性進(jìn)行分析。LineSim中的傳輸線模型構(gòu)筑如圖5所示。

圖5中的傳輸線模型由發(fā)送端、線阻抗、路徑上的相關(guān)器件與接收端組成。發(fā)送端和接收端的仿真模型是一種IBIS仿真文件。IBIS是對(duì)輸入輸出端口的電氣特性快速準(zhǔn)確建模的方法,是反映芯片驅(qū)動(dòng)和接收電氣特性的一種國(guó)際標(biāo)準(zhǔn),它提供一種標(biāo)準(zhǔn)的文件格式來(lái)記錄如驅(qū)動(dòng)源輸出阻抗、上升/下降時(shí)間及輸入負(fù)載等參數(shù),非常適合用于振蕩和串?dāng)_等高頻效應(yīng)的計(jì)算與仿真。這里選擇發(fā)送端為ICS85301l的模型,而接收端為ADS5463的模型,圖中線路阻抗選擇50 Ω,兩個(gè)輸出端并聯(lián)到地的電阻為142 Ω,線路上的隔直電容為100 nF。

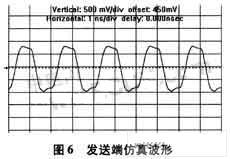

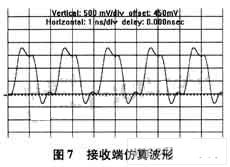

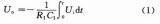

輸入激勵(lì)設(shè)置為.500 MHz、占空比為50的時(shí)鐘源,在LineSim的數(shù)字示波器的仿真結(jié)果窗口中顯示的波形如圖6和圖7所示。

圖6和圖7顯示的是信號(hào)的差分值。可以看出,信號(hào)在發(fā)送端的失真還可以接受,但是在接收端的波形出現(xiàn)了較嚴(yán)重的振鈴現(xiàn)象,其原因可能是:傳輸線阻抗和負(fù)載阻抗不匹配,導(dǎo)致信號(hào)發(fā)生反射,引起振鈴現(xiàn)象;端接的拓?fù)浣Y(jié)構(gòu)不對(duì),采用了錯(cuò)誤的端接方式。 傳輸線理論中對(duì)于振鈴現(xiàn)象原因的分析是:當(dāng)傳輸線阻抗大于信號(hào)源阻抗時(shí),信號(hào)源段反射系數(shù)為負(fù)值,這時(shí)將產(chǎn)生振鈴現(xiàn)象。結(jié)合本電路分析,由于信號(hào)源阻抗是ICS853011內(nèi)部的輸出射隨器的輸出阻抗,約為4 Ω,而此時(shí)的傳輸線阻抗為50 Ω,過(guò)強(qiáng)的驅(qū)動(dòng)能力導(dǎo)致負(fù)載端出現(xiàn)振鈴現(xiàn)象。

消除振鈴現(xiàn)象的方法有降低系統(tǒng)時(shí)鐘頻率、縮短傳輸線長(zhǎng)度、采用正確的端接方式3種。由于本系統(tǒng)的時(shí)鐘頻率是固定的,而傳輸線長(zhǎng)度又由PCB(印制電路板)的物理布局所限定,故只有采用正確的端接方式最為經(jīng)濟(jì)靈活。常見(jiàn)的端接方式有源匹配和負(fù)載匹配,下面介紹這兩種方法的原理。

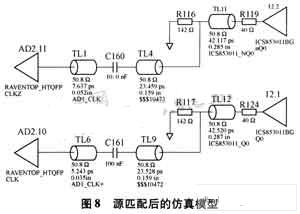

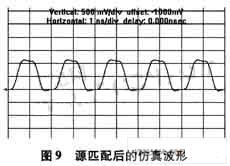

源匹配要求為輸出端串聯(lián)一個(gè)電阻,使源阻抗R。等于線路阻抗Z。,串聯(lián)后,源反射系數(shù)等于0,從而消除了負(fù)載上的反射信號(hào)。換言之,串聯(lián)的電阻吸收了發(fā)射的信號(hào)。本電路改進(jìn)后如圖8所示,在輸出端串聯(lián)了一個(gè)的電阻Rs,Rs=z0一R0=50-4=46 Ω,串聯(lián)后的接收端波形見(jiàn)圖9。從圖9可看出,串聯(lián)一個(gè)電阻后,接收端的波形得到了很大改善。但是這種方式稍微減小了接收波形的幅度值。但總的來(lái)說(shuō),信號(hào)還在ADC的接受范圍內(nèi),不會(huì)對(duì)ADC性能有較大影響。

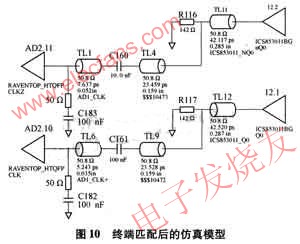

為了不衰減時(shí)鐘信號(hào)的幅度,另一種較好的匹配方式是終端匹配。終端匹配的原理是在走線路徑終端并聯(lián)一個(gè)電阻RL在接收端負(fù)載上,使總的負(fù)載ZL=Z0,從而使反射系數(shù),以消除反射,在這里采用交流負(fù)載匹配,即由一個(gè)電阻RL串聯(lián)一個(gè)電容CL然后并聯(lián)到原接收端負(fù)載上,這樣相比單接一個(gè)電阻最大的好處是可以降低直流功耗。改進(jìn)的電路如圖10所示。

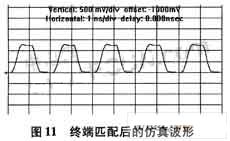

圖11所示為由HyperLynx的仿真波形,可見(jiàn)這種方式也改善了接收端波形,同時(shí)減少了直流功耗。

在實(shí)際的時(shí)鐘電路設(shè)計(jì)中,不僅需要考慮端接方式和器件值大小,還需要考慮器件的擺放,如端接電阻和必須盡可能靠近接收端、源電阻必須盡可能靠近發(fā)送端、器件與走線方向一致等;同時(shí),布線必須嚴(yán)格按照差分規(guī)則,保證兩差分線之間間距相等、兩線線長(zhǎng)相等,與周?chē)咚贁?shù)字線保持2倍以上的線間距,只有這樣才能最終實(shí)現(xiàn)高性能的時(shí)鐘設(shè)計(jì)。

4結(jié)束語(yǔ)

在高速時(shí)鐘電路的設(shè)計(jì)中,信號(hào)完整性問(wèn)題一直是困擾設(shè)計(jì)人員的問(wèn)題,本文提出的PECIL高速時(shí)鐘設(shè)計(jì)是在ADC設(shè)計(jì)中成功與否的關(guān)鍵因素。通過(guò)HyperLynx仿真,可以在最大程度上避免設(shè)計(jì)中的信號(hào)完整性問(wèn)題。本時(shí)鐘設(shè)計(jì)已在PcB實(shí)物上得到驗(yàn)證,取得了與仿真一致的效果,證明使用 HyperLynx輔助設(shè)計(jì)人員進(jìn)行關(guān)鍵時(shí)鐘路徑的設(shè)計(jì)是可行的。欲了解更多信息請(qǐng)登錄電子發(fā)燒友網(wǎng)(http://www.nxhydt.com)

電子發(fā)燒友App

電子發(fā)燒友App

評(píng)論