0、引言

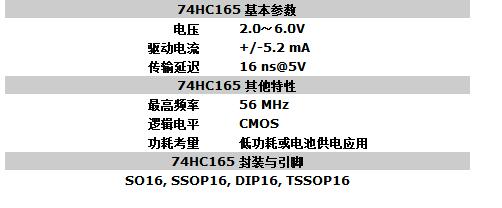

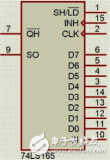

74HC165是一款高速CMOS移位寄存器,電壓為2.0~6.0V,驅(qū)動電流為+/-5.2mA。74HC165引腳兼容TTL(LSTTL)系列(定義于JEDEC標準№.7A)。

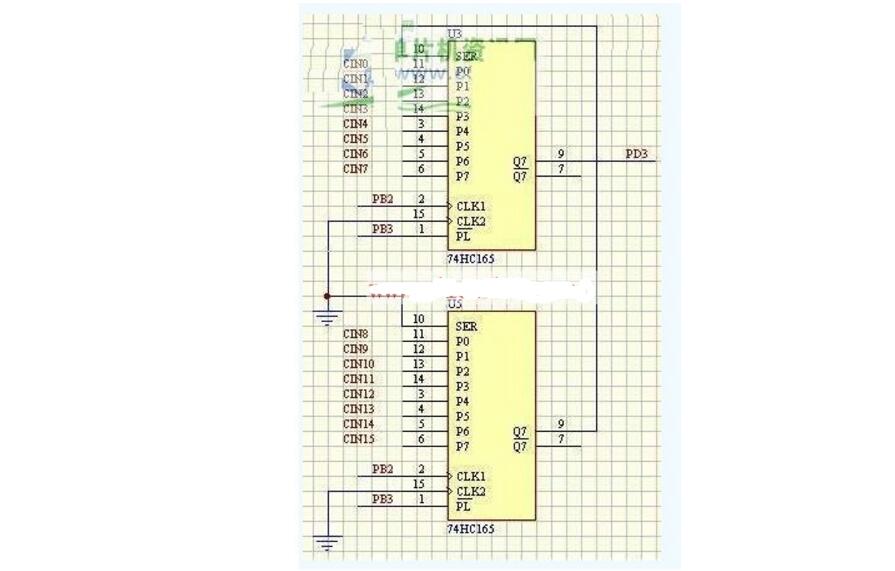

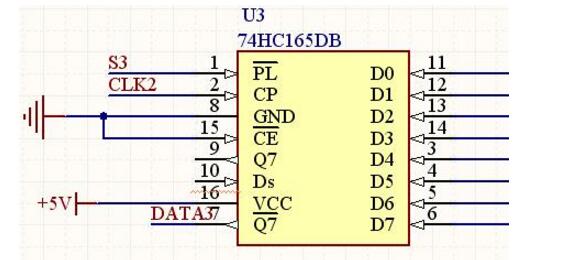

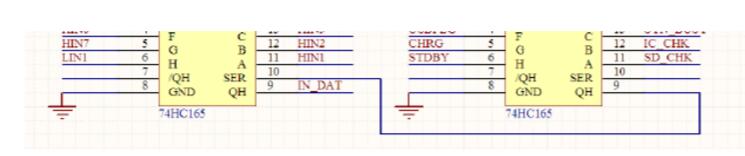

74HC165是8位并行輸入串行輸出移位寄存器,可在末級得到互斥的串行輸出(Q0和Q7),當并行讀取(PL)輸入為低時,從D0到D7口輸入的并行數(shù)據(jù)將被異步地讀取進寄存器內(nèi)。而當PL為高時,數(shù)據(jù)將從DS輸入端串行進入寄存器,在每個時鐘脈沖的上升沿向右移動一位(Q0→Q1→Q2,等等)。利用這種特性,只要把Q7輸出綁定到下一級的DS輸入,即可實現(xiàn)并轉(zhuǎn)串擴展。

74HC165的時鐘輸入是一個“門控或”結(jié)構,允許其中一個輸入端作為低有效時鐘使能(CE)輸入。CP和CE的引腳分配是獨立的并且在必要時,為了布線的方便可以互換。只有在CP為高時,才允許CE由低轉(zhuǎn)高。在PL上升沿來臨之前,CP或者CE應當置高,以防止數(shù)據(jù)在PL的活動狀態(tài)發(fā)生位移。

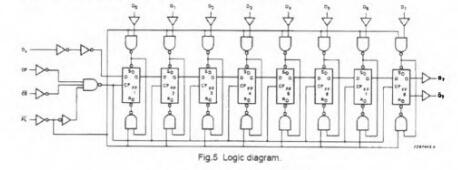

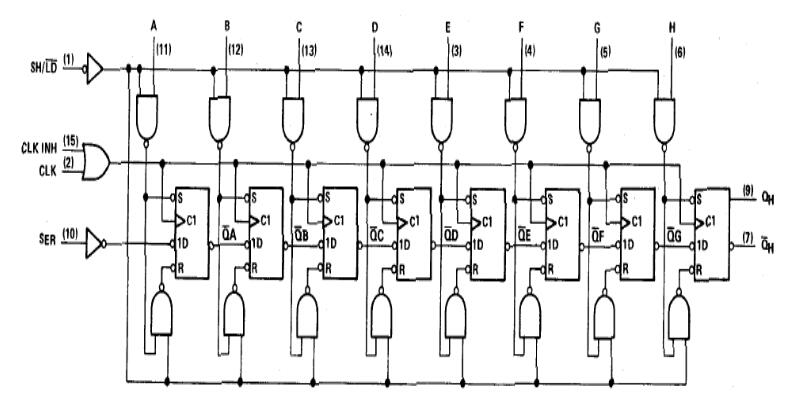

圖174HC165邏輯圖

單片機的開漏口輸出高電平時,需要上拉電阻,否則無法輸出高電平,同時為了提高抗干擾能力還要接一個瓷片電容進行濾波。

1、現(xiàn)象描述

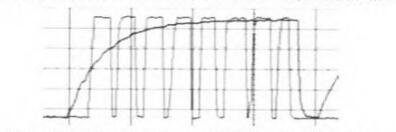

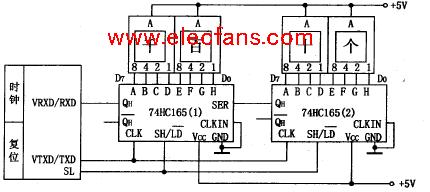

74HC165的數(shù)據(jù)裝載口上拉一個10K歐姆的電阻(R160)到5V,串聯(lián)一個510Ω(R260)的限流電阻和濾波電容102(C69)到單片機開漏口。通過計算RC充電時間,R=R160+R260=10510Ω,C=C69=1000PF,充電電壓為5V,算出充電時間為42.04us。實際測量的充電時間為42us左右,同計算的時間基本一致。(若為推挽輸出口控制PL腳,充電時只通過R260=510Ω和電容C69=1000PF,充電時間約為2.04us)。如圖2,時鐘口波形為脈沖數(shù)較多的,數(shù)據(jù)裝載口為脈沖數(shù)較少的,可知數(shù)據(jù)裝載口還沒有完全達到高電平時,就有了移位脈沖,導致移位失效,數(shù)據(jù)讀取錯誤。

圖2C為102時74HC165數(shù)據(jù)裝載口和時鐘口波形

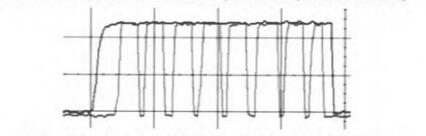

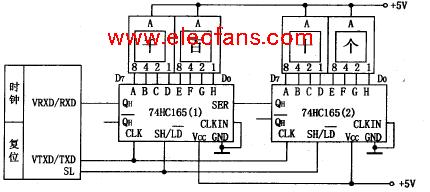

若電容C改為101時,通過計算和實際測量,得到充電時間為4.204us,充電速度快了十倍,如下圖3。數(shù)據(jù)裝載口變?yōu)榭煽康母唠娖胶螅庞幸莆粫r鐘脈沖,移位成功,數(shù)據(jù)讀取成功。

圖3C為101時74HC165數(shù)據(jù)裝載口和時鐘口波形

2、原因分析

74HC165是一個8位移位寄存器(并行輸入、互補串行輸出),當移位/置入控制端PL為低電平時,并行數(shù)據(jù)A-H(D0-D7)被置入寄存器,而與時鐘(CP)及串行數(shù)據(jù)(Ds)均無關。當PL為高電平時,并行置數(shù)功能被禁止。要特別注意,移位時,PL為低電平時,移位無效。PL為高電平時,才能移位。當PL為高電平,而且CE為低電平時,與非門的輸出完全由CP控制。當PL為低電平時,雖然CE為低電平,但是與非門的輸出固定為高電平,不論CP電平如何變化,與非門的輸出始終固定為高電平。所以,顯然只有CE低電平去使能CP脈沖是不夠的,同時PL也為高電平才能使CP脈沖有效。如圖1中的D觸發(fā)器1。

2.1PL為高電平時,由于SD和RD連接的與非門,有一個管腳連接PL的非門,是低電平,故SD(直接置1端)和RD(直接清零端)都是高電平,不影響電路工作。所以每次CP的上升沿,D端數(shù)據(jù)會移動到Q端,并且鎖存起來。

2.2PL為低電平時,由于SD和RD連接的與非門有一個管腳連接PL的非門,是高電平,故SD(直接置1端)和RD(直接清零端)的狀態(tài)都完全根據(jù)D0決定。當D0為1時,SD為0(低電平有效),RD為1,故Q1直接置1。當D0為0時,SD為1,RD為0(低電平有效),故Q1直接清0。這就是數(shù)據(jù)裝載的原理。同時,由于PL為低電平時,CP被與非門無效了,所以每次CP的上升沿,D端數(shù)據(jù)不會移動到Q端。

3、結(jié)論

若PL的高電平不可靠時,會出現(xiàn)移位失敗的問題,從而導致數(shù)據(jù)讀取錯誤。要使CP的移位有效,提前必須使CE為可靠低電平且PL為可靠的高電平。當開漏口控制PL引腳時,務必注意查看由低電平到高電平的波形,是否提前于CP的上升沿。若變?yōu)楦唠娖揭院螅庞蠧P上升沿,則沒有問題;若還沒有完全變?yōu)楦唠娖剑藭rCP上升沿出現(xiàn),則有可能移位不成功。

電子發(fā)燒友App

電子發(fā)燒友App

評論