數字頻率計設計

一、實驗目的?????????????????????????????????????????????????????????????????????

1.熟悉CPLD的開發軟件的基本使用。

2.理解頻率計的測量原理。

3.掌握CPLD邏輯電路設計方法。

4.掌握虛擬數字頻率計的軟件設計。

二、實驗任務和內容

1. 在CPLD中設計一個數字頻率計電路,設計要求為: 測量范圍:1Hz~1MHz, 分辨率<10-4>, 數碼管動態掃描顯示電路的CPLD下載與實現。

2.使用LabVIEW進行虛擬頻率計的軟件設計。要求設計軟件界面,閘門時間為4檔,1s,100ms,10ms,1ms,頻率數字顯示。

3.使用設計虛擬邏輯分析儀軟件和CPLD電路,進行軟硬件調試和測試

三、實驗器材

1. SJ-8002B電子測量實驗箱? 1臺

2.計算機(具有運行windows2000和圖形化控件的能力)? 1臺

3.函數發生器? 1臺

4.SJ-7002 CPLD實驗板 1塊

5.短接線若干

四、實驗原理

4.1.測頻原理

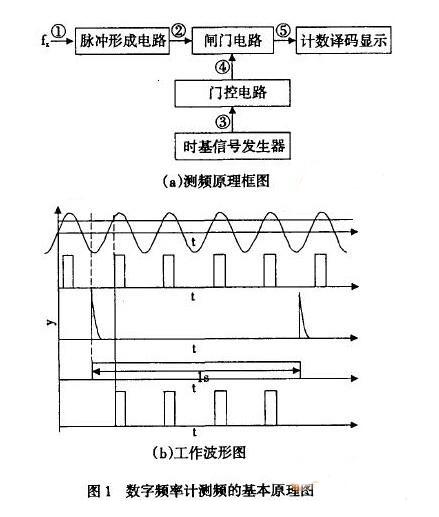

??? 所謂“頻率”,就是周期性信號在單位時間變化的次數。電子計數器是嚴格按照f=N/T的定義進行測頻,其對應的測頻原理方框圖和工作時間波形如圖1 所示。從圖中可以看出測量過程:輸入待測信號經過脈沖形成電路形成計數的窄脈沖,時基信號發生器產生計數閘門信號,待測信號通過閘門進入計數器計數,即可得到其頻率。若閘門開啟時間為T、待測信號頻率為fx,在閘門時間T內計數器計數值為N,則待測頻率為

fx = N/T?? (1)

??? 若假設閘門時間為1s,計數器的值為1000,則待測信號頻率應為1000Hz或1.000kHz,此時,測頻分辨力為1Hz。

??? 本實驗的閘門時間分為為4檔:1s,100ms,10ms,1ms。

?

?????????????????????? ? ? ?? 圖1 測頻原理框圖和時間波形

4.2 數字頻率計組成

??? 本實驗要求的數字頻率計組成如圖2所示,頻率計的硬件電路(圖1所示)在CPLD芯片中實現,測量結果通過實驗箱提供的EPP通信接口送給計算機,頻率計的軟件和人機界面由計算機完成,同時計算機還可輸出清零和閘門選擇的控制信號給電路。

??? 本實驗的任務一是在提供的CPLD實驗板上設計和實現頻率計測量電路,二是在計算機上使用LabVIEW軟件設計頻率計界面和程序。

? ? ? ? ? ? ? ? ? ? ? ? ? ? ?????????? 圖2 數字頻率計組成框圖

4.3 CPLD特點和設計流程

??? CPLD器件是由用戶配置以完成某種邏輯功能的電路,本CPLD實驗電路板選用ALTERA公司的EPM7128SLC84器件,其特點為:84引腳Pin,內部有128個宏單元、2500個等效邏輯門、15ns的速度、PLCC84封裝形式。除電源引腳、地線引腳、全局控制引腳和JTAG引腳外,共提供了64個可用I/O腳,這些引腳可以任意配置為輸入、輸出和雙向方式。

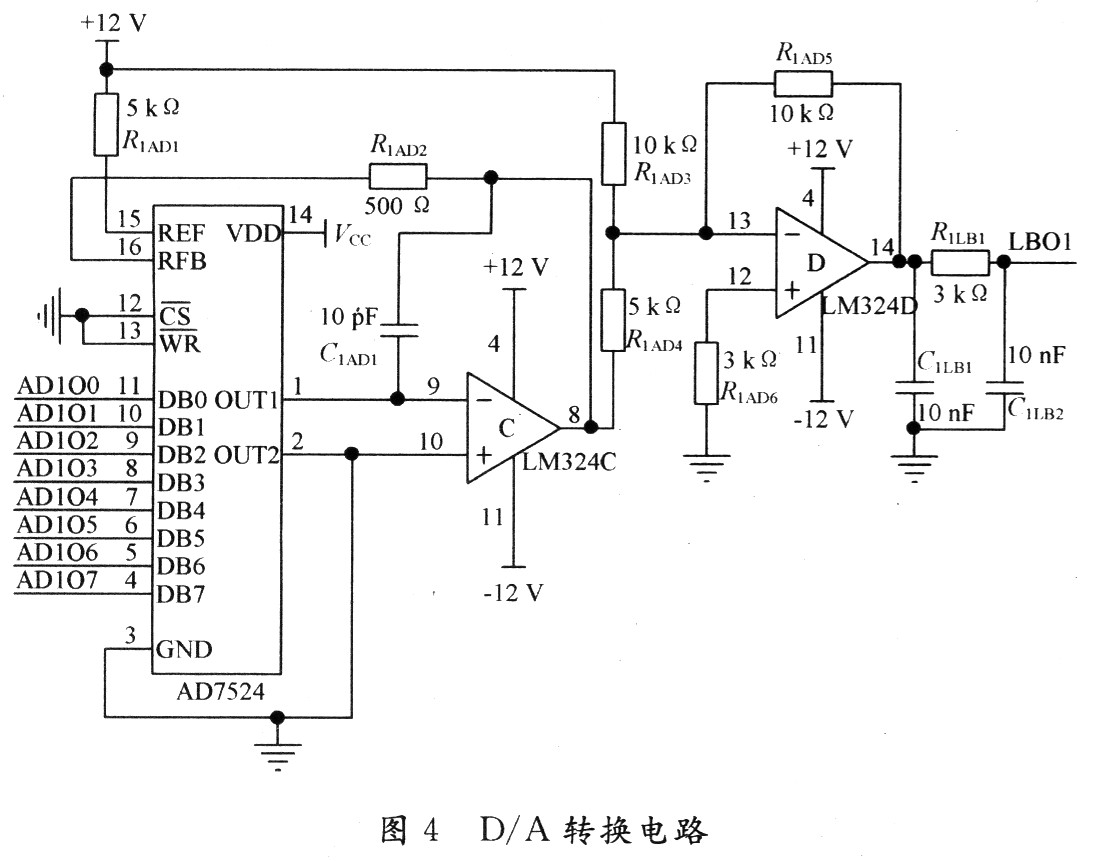

?? CPLD的設計流程如圖3所示,本實驗采用的設計軟件為ALTERA公司的Quartus Ⅱ,下載方式采用的是并口電纜ByteBlaster。下載時的硬件設置操作如圖4所示。

??????  ??

??

? ???????????? 圖3 CPLD設計流程和并行電纜下載示意圖

?

?

?

?

?

?

? ??????? ?? ??????????? 圖4 下載時的硬件設置選ByteBlaster

4.4 CPLD實驗電路板

?? 1)數字信號輸入:8個ON~OFF(K1~K8)開關

?? 2) 數字信號輸出(顯示):8個LED燈(LED1~LED8),低電平點亮

?? 3) 6個LED 7段數碼管,采用動態掃描方式,L1、L2、L3為位選信號,低有效,A、B、……、G為7段碼,DP為小數點,均為低有效。

?? 4) 時鐘晶振:頻率為1MHz,已連接到CPLD的時鐘引腳

?? 注:使用CPLD板的1.000MHz的晶振時鐘,需放置CPLD板上S1短路塊位置在右面。

???????????? ???? ??????

????????????????????? ? ???

?

?

?

?

?

?

??????????????? ??????? 圖5 CPLD實驗板電路板照片和組成框圖

4.5 CPLD實驗電路板原理和與實驗箱62芯插座連接關系

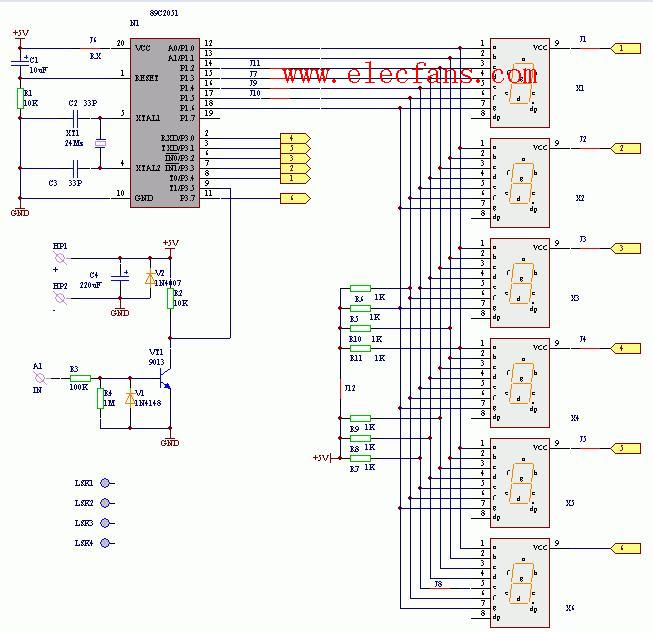

??? 圖6 為CPLD板的詳細電路圖。

?? CPLD可供用戶自定義的引腳見表1,共有25個引腳,均可根據需要定義為輸入或輸出。

?? CPLD與實驗箱62芯插座定義表見表2,可使用3個8位的數字I/O口作為頻率計的輸入計數結果,1個5位的單向數據輸出口為頻率計的控制口。

?????? ?? ???? ??? ??? ???? ???? ? 表1 用戶可用的CPLD自定義I/O引腳

P4 |

P5 |

P6 |

P8 |

P9 |

P10 |

P11 |

P15 |

P16 |

P17 |

P18 |

P20 |

P21 |

|

P22 |

P24 |

P25 |

P27 |

P28 |

P29 |

P30 |

P31 |

P77 |

P79 |

P80 |

P81 |

??? ? ? ? ? ? ?? ?? ?????? ? ? ??? 表2 CPLD和62芯插座連線引腳定義

引腳 名稱 |

CPLD |

62芯插座引腳 |

說明 |

引腳 |

CPLD |

62芯插座引腳 |

說明 | |

|

DO0 |

P40 |

16 |

數字I/O口 |

DO24 |

P63 |

28 |

單向輸出口 | |

|

DO1 |

P36 |

48 |

DO25 |

P76 |

60 | |||

|

DO2 |

P41 |

17 |

DO26 |

P64 |

29 | |||

|

DO3 |

P44 |

49 |

DO27 |

P75 |

61 | |||

|

DO4 |

P45 |

18 |

DO28 |

P68 |

30 | |||

|

DO5 |

P46 |

50 |

VCC |

P3,P13, |

31,62 |

+5V電源 | ||

|

DO6 |

P48 |

19 | ||||||

|

DO7 |

P49 |

51 | ||||||

|

DO8 |

P50 |

20 |

數字I/O口 | |||||

|

DO9 |

P51 |

52 |

GND |

P1,P7, |

13,44 |

電源地 | ||

|

DO10 |

P55 |

21 | ||||||

|

DO11 |

P52 |

53 | ||||||

|

DO12 |

P54 |

22 | ||||||

|

DO13 |

P65 |

54 | ||||||

|

DO14 |

P57 |

23 |

CPLD時鐘源 |

P83 |

45 |

由S1短路 | ||

|

DO15 |

P67 |

55 | ||||||

|

DO16 |

P56 |

24 |

數字I/O口 | |||||

|

DO17 |

P69 |

56 | ||||||

|

DO18 |

P58 |

25 |

outsideclk |

P39 |

15 |

選擇接(P83) | ||

|

DO19 |

P70 |

57 |

allCLR |

P35 |

47 |

系統總清零 | ||

|

DO20 |

P61 |

26 |

outside_tri |

P37 |

14 |

外部觸發 | ||

|

DO21 |

P73 |

58 |

||||||

|

DO22 |

P60 |

27 |

||||||

|

DO23 |

P74 |

59 |

?

? ????????????????????????????? ????????????? ???????? ?????? 圖6 CPLD實驗板電路原理圖

五、設計指導:

??? 分為CPLD硬件電路設計和虛擬頻率計軟件設計兩部分

5.1 CPLD硬件電路設計

??? CPLD設計和調試的過程是:①任務分析,層次分解,得到頂層設計框圖,大致確定每個子模快(子電路)的功能、輸入和輸出;②子模快電路設計和軟件仿真;③完成頂層電路設計,頂層仿真;④分配引腳,下載,連線和調試。

?? 5.1.1設計任務分析和頂層設計

?? 根據設計任務,可分為四大部分:

? (1)閘門時間和測量控制:閘門時間分別為1s,100ms,10ms,1ms,由1MHz的基準時鐘分別產生1Hz,10Hz,100Hz,1kHz的時基信號作為閘門控制信號,同時控制測量結果的鎖存。

?? (2)多位計數器電路:根據閘門時間最長為1秒,被測信號頻率最高為1MHz,所以選用6位十進制計數器,保證測量計數器不溢出。6位十進制的計數器對被測信號的脈沖進行計數,輸出6位十進制計數值,每位都用4位BCD碼表示,共有24根線。每次測量開始前清零計數值。

? (3)計數結果鎖存和實驗箱接口:在每次測量閘門時間到時使用鎖存器鎖存計數值(6位BCD碼),供計算機讀數。

? (4)計數結果6位數碼管動態顯示電路: 設計一個6位BCD選1的多路數據選擇器,輸出的一位BCD碼(4根線)送給BCD-七段譯碼器譯成段信號,從CPLD輸出給數碼管的7段。同時多路數據選擇器的控制選通信號需要3根,必須與6位數碼管的位選信號同步。位選信號來自電路板的時鐘(1MHz)分頻,在用譯碼器譯碼(每次只能選中一個數碼管)。要保證多位顯示均勻和不閃爍,請計算和設計分頻的頻率和電路。

??? 根據CPLD電路的層次化設計功能,設計出如圖7所示的頂層設計框圖。

? ???

? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? 圖7 頻率計頂層設計框圖

5.1.2 部分電路設計提示

??? 電路的設計均有原理圖設計和HDL語言文本設計兩種方法,根據電路的特點和各人的情況,自己選用。

對每個子模快進行軟件仿真,先創建波形文件,設定時間間隔和解釋時間,編輯輸入波形,運行仿真,分析結果是否正確。若不正確,則修改設計,重新編譯后,再仿真,直到正確為止。

?? (1)閘門時間和測量控制: 閘門時間分別為1s,100ms,10ms,1ms,由1MHz的基準時鐘分別產生1Hz,10Hz,100Hz,1kHz的時基信號作為閘門控制信號,使用CPLD實驗板上的1MHz時鐘信號,經過1000分頻得到1kHz信號,在經過10分頻得到100Hz信號,在經過10分頻得到10Hz信號,在經過10分頻得到1Hz信號。設計時,先設計一個10分頻電路,級聯3個,得到1000分頻,級聯一個,得到10分頻。閘門時間選擇共4檔(1s,100ms,10ms,1ms),可采用數據選擇器實現,需要2根從計算機來的控制信號。閘門時間產生電路,設計一個電平有效清零端,作為啟動測量或停止測量,由計算機通過實驗箱來控制。閘門時鐘經過D觸發器2分頻,得到閘門時間內為高電平的信號,作為測量計數結果的鎖存控制信號。閘門時鐘和顯示時鐘產生測量計數器的清零信號。

??? (2)多位十進制的計數器子模塊設計:

??? 沒有現成電路可用,所以必須自己設計。

??? 為什么不選用二進制計數器(從顯示要求、二進制轉換為BCD電路的難易等考慮)

??? 設計方法一:選用6個1位的可逆帶清零十進制計數器級聯得到。注意進位/借位信號的時序。

??? 設計方法二:使用HDL語言編程,注意同時滿足十進制、加、減的進位和借位。

?? (3)計數結果鎖存和實驗箱接口:

??? 在每次測量閘門時間到時使用鎖存器鎖存計數值(6位BCD碼),供計算機讀數。采用3個8位的鎖存器74273,輸入鎖存由閘門時間控制,輸出長選通,連接實驗箱提供的3個數字I/O口,工作在輸入方式。

? (4)計數結果6位數碼管動態顯示電路:

?? 由6位BCD選1電路、BCD-七段譯碼器、位選電路組成,其中為選電路又包括分頻電路、為選控制和為選譯碼電路。

?? ①6位BCD選1的多路數據選擇器設計:

?? 沒有現成電路可用,所以必須自己設計。

?? 可選用多個數據選擇器來組合。要求控制選通信號需要3根,按000-001-010-011-100-101變化,只有6個狀態。

?? ②BCD-七段譯碼器設計:

?? 有現成電路選用,注意共陰和共陽數碼管的區別。

?? ③位選信號產生

? 分頻電路:位選信號來自電路板的時鐘(1MHz)分頻,要保證多位顯示均勻和不閃爍,先計算分頻電路要求的輸出頻率,再設計分頻電路。可使用計數器分頻。也可直接借用閘門時間電路的分頻信號。

? 位選控制:要求為6個狀態,設計電路可采用狀態機的方法,但仔細分析6個狀態之間的關系后,可得出符合_________的計數器。

? 設計方法:語言和圖形均可。

? 位選譯碼:每次選中一個,可選用什么譯碼器?注意位選電平是高電平有效還是低電平有效。

5.1.3 分配引腳和編譯、下載

??? 用戶可用引腳見表2,引腳分配要滿足CPLD電路板上已有的連線情況,考慮芯片引腳和外圍電路的位置,就近分配。如輸入被測信號在右邊,輸出7段碼和位選在左邊。與計算機和實驗箱的連接遵照表2的規定。

每次分配引腳后,需重新編譯后,再下載。

5.2 虛擬頻率計軟件設計

5.2.1虛擬頻率計界面設計

??? 軟件界面上控制型控件有1個數字型旋鈕用于選擇閘門時間,分為1s,100ms,10ms,1ms 4檔,兩個按鍵,1個控制測量的啟動/停止,1個控制整個程序退出。

指示型控件有3組,1個布爾型指示燈顯示采樣狀態,1組顯示測量的頻率數值(十進制)和單位(字符串),單位有Hz和kHz兩種,還有1組顯示讀取的3個字節的計數值(BCD碼),由3個數字型控件組成。

??????????

?????????????????????????????????? ?????????? 圖8 頻率計界面

5.2.2程序流程圖

?????????????????????????

??????????????????????? ??????????? 圖9 程序流程圖

5.2.3 實驗箱EPP接口和編程

SJ8002B實驗箱本實驗使用EPP地址和意義

地 |

址 |

功能和設置 |

本實驗中的設置 |

|

00H |

D7-D0 |

全局清零信號(在讀數、采集、啟動信號源之前都必須)? (00H?00) |

EPP初始化時發清零信號 |

|

01H |

D2-D0 |

小板控制使能(U019,U020,U021片選), |

在本實驗中需使能 |

|

02H |

D2-D0 |

DO0-DO23數據方向控制 |

在本實驗中都設為輸入 |

|

03H |

D7-D0 |

DO7-DO0數據 |

在本實驗中作為計數值低字節 |

|

04H |

D7-D0 |

DO15-DO8數據 |

在本實驗中作為計數值中字節 |

|

05H |

D7-D0 |

DO23-DO16數據 |

在本實驗中作為計數值高字節 |

|

06H |

D4-D0 |

DO28-DO24數據 (只有輸出) |

在本實驗中作為測量控制和閘門選擇 |

? 對EPP接口的操作,調用以下3個子VI來完成:

?(1)EPP初始化: epp_init.vi 調用時無參數。

? (2) EPP寫:epp_read_data.vi 調用是輸入地址和數據,無輸出參數

? (3) EPP讀:epp_read_data.vi ,調用是輸入地址,輸出數據。

5.2.3 數據轉換和顯示

?? 測量計數值=高字節×10000+中字節×100+低字節

?? 測量結果=計數值/閘門時間

?? 編程時考慮不同檔位時的數值、單位和有效位數。

六. 測試和調試

6.1 調試

? (1)實驗硬件連接

?? 根據設計的頻率計電路和分配的引腳連線,被測頻率信號連接到函數發生器的TTL(CMOS)輸出端。計數器的輸出位選分別連接6個數碼管的為選端L1~L6;注意左邊的數碼管為低位,7段信號分別連接。

??????????????

???????? ? ???????? ????????? ??????? ?? 圖10 實驗連線圖

?? (2) 檢查動態掃描電路

??? 數碼管7段信號全部直接接地,位選分別連接CPLD輸出位信號,6個數碼管穩定顯示“888888”。

? (3)軟硬件聯調:

?? 允許虛擬頻率計程序,輸入信號的頻率在10KHz,按下測量鍵,觀察頻率計的顯示結果是否正確,如不正確,則檢查程序,改正錯誤。

?? 改變閘門時間,觀察有效位數的變化,閘門時間為1秒時,有效位數最多。

?? 改變輸入信號的頻率,繼續測量和觀察。

6.2 測試

?(1) 調節函數發生器輸出信號的頻率為200kHz,選擇不同的閘門時間,進行測試,并且把測試結果填入表2。

?????????????? ????????????? ?? 表2 閘門時間不同時頻率測試結果(信號頻率200kHz)

閘門時間信號頻率 |

1ms |

10ms |

100ms |

1s |

|

測試頻率 |

? |

? |

? |

? |

? (2)固定閘門時間1s,輸入不同頻率時,進行測試,把測試結果填入表3,并且計算測試誤差。

???????????????? ??????????? 表3 輸入信號頻率不同時測試結果(閘門時間為1秒)

信號頻率 |

25Hz |

0.25kHz |

2kHz |

20kHz |

200kHz |

900kHz |

|

信號源實際 |

? |

? |

? |

? |

? |

? |

|

測試頻率 |

? |

? |

? |

? |

? |

? |

|

測試誤差 |

? |

? |

? |

? |

? |

電子發燒友App

電子發燒友App

評論