時鐘是SOC或塊級設計最重要的組成部分之一,在設計概念構思/規(guī)劃階段中,需要很好地定義和理解時鐘的架構。單個SOC擁有各類模塊,如內核、閃存、存儲器和外設,這些模塊需要在不同頻率下運行。它們的最大運行速率可能受到所使用的實現(xiàn)技術、實施架構、功率目標、以及IP訪問時間等因素的限制。時鐘分頻器電路是必不可少的,它可以從主鎖相環(huán)(PLL)/振蕩器時鐘,或任何系統(tǒng)時鐘中產(chǎn)生分頻時鐘,并將不同的分頻時鐘饋送到不同的器件模塊。由于時鐘也可以被應用驅動,時鐘分頻器必須是可配置的。需要可配置性的原因有很多,包括:

* 以較低的頻率運行系統(tǒng)時鐘,從而減少動態(tài)功耗。

* 以高于或低于處理器的頻率運行外設的狀態(tài)機。

* 設置發(fā)送/接收外設幀的波特率。

本文闡述了目前SOC中各種可配置時鐘分頻器邏輯的實施方案,強調了各自的問題、優(yōu)勢及局限性。可配置分頻有各種實施方案,但是數(shù)字化設計行業(yè)中最簡單且最經(jīng)常使用的實施方案包括:

* 紋波分頻器

* 具有50%占空比的基于Div解碼的2N倍分頻器

* 不具有50%占空比的基于時鐘門控使能技術的整數(shù)分頻器

* 具有整數(shù)分頻和50%占空比的基于多路選擇器的分頻器。

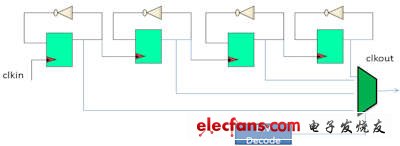

紋波分頻器

圖1:可配置紋波分頻器的電路示意圖。

紋波分頻器是傳統(tǒng)的分頻器,由于它們在安裝和保持時間上有嚴格的要求,目前的SoC設計中通常避免使用這種分頻器。

優(yōu)勢:

* RTL復雜性最小

* 生成的分頻時鐘占空比為50%。

局限性:

* 時鐘時延隨著更高版本分頻時鐘的應用而增加(時鐘上升沿的延遲大小排列為DIV16》 DIV8》 DIV4》 DIV2》 DIV1。)

如果啟動時鐘和捕獲時鐘從帶不同分頻因子的不同分頻器產(chǎn)生,這個缺陷可能導致更大的路徑不一致。

例如,設想一個帶兩個紋波分頻器的簡單時鐘架構(見下圖),其中一個用于為內核提供時鐘,另一個用于為閃存提供時鐘。兩個時鐘之間的比例必須是4:1。這會導致設計本身有意想不到的偏差。

圖2:可配置時鐘示例。

閃存時延–平臺時延= 2個觸發(fā)器的CK-Q延遲

* 即使有時鐘樹平衡,也要確保強大的時序簽收功能,這對于設計進入投產(chǎn)階段非常重要。STA工程師需要在四個不同觸發(fā)器的輸出上定義時鐘,因為每個觸發(fā)器都在生成具有不同時延的時鐘。這增加了人工工作,需要在設計中人工定義并檢查所有可能生成的時鐘。

基本RTL如下所示:

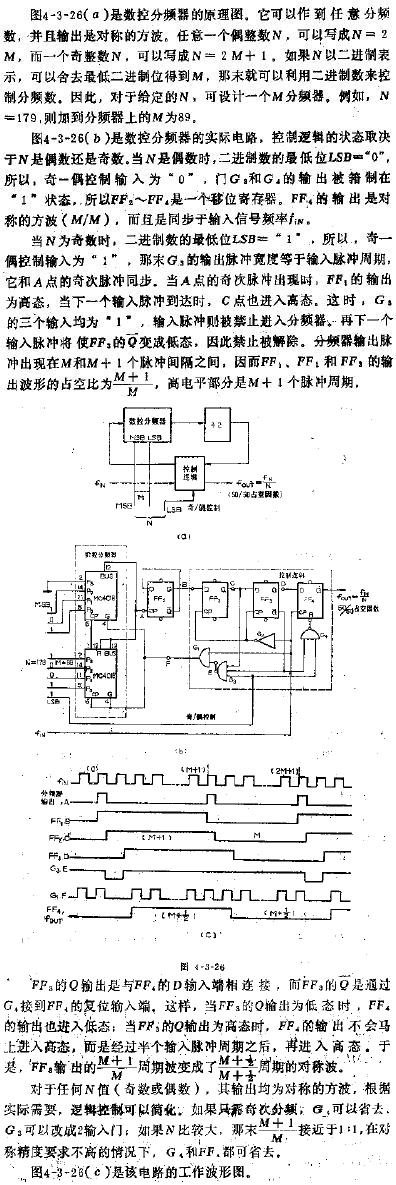

圖3:Div解碼分頻器實施。

在需要分頻的輸入時鐘的每個上升沿上都更新一次postscale_count寄存器的值。分頻時鐘可以從postscale_count寄存器的MSB中產(chǎn)生。下一個計數(shù)寄存器的值取決于分頻因子。

優(yōu)勢:

* 這類分頻器擁有最簡單的RTL。

* 它們產(chǎn)生的輸出時鐘占空比為50%,且不會像紋波分頻器一樣導致固有偏移,因為分頻時鐘總產(chǎn)生于一個點。

局限性:

* 這類分頻器僅限于2N倍分頻。

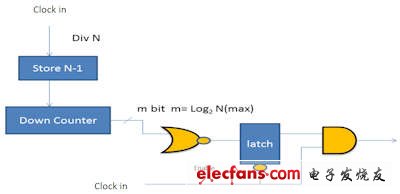

基于時鐘門控使能的整數(shù)分頻器或穿通分頻器

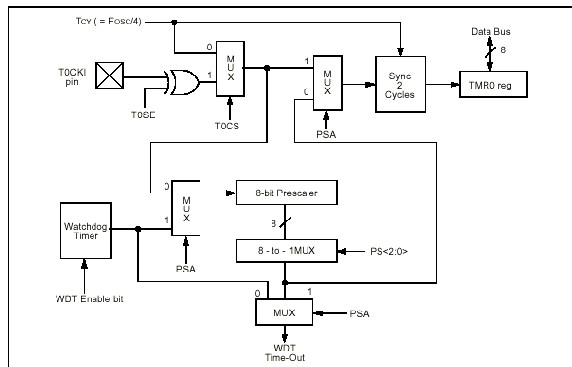

圖4顯示了一個簡單的穿通時鐘分頻器實施過程。

圖4:基于時鐘門控的分頻器。

圖5顯示了3分頻時鐘生成的波形圖。

M bit m=log2N(max): M bit m=log2N(max)

圖5:3分頻時鐘生成的波形圖。

一旦存儲(N-1)寄存器值達到零,倒數(shù)計數(shù)器將被初始化。電路中的鎖存器確保“NOR”門輸出產(chǎn)生的使能只有在時鐘為低時被傳播到AND門。如果沒有鎖存器,輸出時鐘可能產(chǎn)生故障。

優(yōu)勢:

* 對于基于時鐘門控的分頻器,RTL是相當簡單的,另外,穿通時鐘方案顯著減少了高速時鐘DFT復雜性。

局限性:

* 某些IP,如DDR,要求占空比為50%,這對于穿通時鐘是不可能實現(xiàn)的。

* 從時鐘上升沿開始到時鐘下降沿結束的時序路徑必須在1/2的時鐘頻率處相遇,也就是說,STA團隊必須在時鐘架構確定前,檢查設計中這些關鍵時序路徑。

基于多路選擇器的分頻器

基于多路選擇器的分頻器的實現(xiàn)如下所示,隨附進行三分頻時的波形樣本。基于多路選擇器的分頻器讓時鐘流經(jīng)2:1多路選擇器的選擇引腳。多路選擇器數(shù)據(jù)引腳的使能值隨著輸入時鐘切換,使得多路選擇器輸出產(chǎn)生的邏輯正是所需的時鐘輸出。這類實施需要一個重要的條件。在多路選擇器的數(shù)據(jù)輸入端,需要添加額外的時鐘門控檢查,確保時鐘分頻器電路正常工作。下面的波形中顯示了時序檢查。

圖6:基于多路選擇器的分頻器。

以下波形在對輸入時鐘進行三分頻時生成。

圖7:3分頻波形。

圖8:時序檢查。

時序檢查1是從時鐘上升沿到時鐘下降沿的半周期設置檢查,因此如果輸入時鐘被鎖定在極高的頻率,這項檢查將至關重要(例如為最大程度地減少抖動,將鎖相環(huán)輸出鎖定在極高的頻率。)

RTL復雜性低,通常由設計人員選擇是否采用50%占空比的時鐘分頻器。

優(yōu)勢:

* 50%占空比的整數(shù)分頻和不具有50%占空比的分數(shù)分頻

* 所有生成的時鐘采用單源引腳(多路選擇器輸出)。

局限性:

* 需要部署額外的時鐘門控檢查,時序變得至關重要。

可配置的基于多路選擇器的分頻器作為分數(shù)時鐘分頻器使用

可配置的分數(shù)時鐘分頻器或FCD是基于多路選擇器的分頻器中一個重要類別。分數(shù)時鐘分頻器的重要特征包括:

* 這些分頻器是異步分頻器,分頻器的時鐘輸出與設計中生成的其他時鐘異步。

* 這些分頻器不具有50%的占空比。

* 輸出時鐘的最大頻率(fmax)(f /分頻系數(shù))四舍五入到.5或0

* 輸出時鐘的最小頻率(fmin)(f/分頻系數(shù))四舍五入到.5或0

所需的輸出頻率實際上是許多輸入時鐘周期中輸出時鐘的平均頻率。

FCD的概念

舉一個分數(shù)時鐘分頻的例子,就可以理解FCD的概念。

假設時鐘分頻為1.3 - 這樣時鐘的最小頻率fmin= 1.5,最大頻率fmax= 1

也就是說:輸出時鐘的10個周期=輸入時鐘的13個周期

設最小頻率的輸出時鐘周期數(shù)為X

設最大頻率的輸出時鐘周期數(shù)為Y

因此

x + y = 10

1.5 x + Y = 13

由此我們解出

x = 6 y =4

這樣,6×1.5=9個輸入時鐘周期,將除以1.5, 4個輸入時鐘周期將除以1。 1.3分頻的波形圖如下所示。這些分頻器常常用于逐級時鐘頻率切換,防止在瞬間出現(xiàn)高電流消耗(這可能導致晶體管的Vdd口出現(xiàn)異常電壓下降或上升,破壞設計,并可能引起芯片復位)。時鐘頻率的步長隨著設計中每單位時間允許的最大頻率增加或減少。

圖9:分數(shù)時鐘分頻。

本文結論

本文向人們展示了目前大多數(shù)設計中都使用的基本可配置時鐘分頻器。盡管實施方案可能會有所不同,但是可配置分頻器的基本思路是一致的。由于每種時鐘分頻器各有優(yōu)點和局限性,設計人員在選擇時鐘分頻器類型時需要格外注意。雖然穿通時鐘方案使DFT時鐘更加簡單,其占空比局限性給時序團隊在分頻時鐘域關閉關鍵的半周期路徑時留下了繁瑣的工作。基于多路選擇器的分頻器提供50%占空比的輸出時鐘,但可能使DFT時鐘變得復雜。因此,如果在設計早期,從功能,DFT和時序方面詳細了解和分析時鐘的關鍵性因素,避免時鐘架構變化,可能會在之后的時序收斂階段帶來意想不到的驚喜。

電子發(fā)燒友App

電子發(fā)燒友App

評論