電路功能與優勢

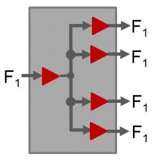

許多系統都要求具有多個低抖動系統時鐘,以便實現混合 信號處理和定時。圖1所示電路將 ADF4351集成鎖相環(PLL)和壓控振蕩器(VCO)與 ADCLK948接口,后者可通過 ADF4351的一路差分輸出提供多達八路差分、低電壓正射極耦合邏輯(LVPECL)輸出。

圖1. 連接至ADCLK948扇出緩沖器的ADF4351 PLL(原理示意圖:未顯示所有連接和去耦)

現代數字系統經常要求使用許多邏輯電平不同于時鐘源的 高質量時鐘。為了確保在不喪失完整性的情況下準確地向 其它電路元件配電,可能需要額外的緩沖。此處介紹 ADF4351 集成鎖相環(PLL)和壓控振蕩器(VCO)與 ADCLK948接口,后者可通過的一路差分輸出提供多達八路差分、低電壓正射 極耦合邏輯(LVPECL)輸出。

現代數字系統經常要求使用許多邏輯電平不同于時鐘源的高質量時鐘。為了確保在不喪失完整性的情況下準確地向其它電路元件配電,可能需要額外的緩沖。此處介紹ADF4351時鐘源和ADCLK948時鐘扇出緩沖器之間的接口,并且測量結果表明與時鐘扇出緩沖器相關的加性抖動為75 fs rms。

電路描述

ADF4351 是一款寬帶PLL和VCO,由三個獨立的多頻段 VCO組成。每個VCO涵蓋約700 MHz的范圍(VCO頻率之間 有部分重疊)。這樣可提供2.2 GHz至4.4 GHz的基本VCO頻 率范圍。低于2.2 GHz的頻率可使用 ADF4351的內部分頻器 生成。

要完成時鐘生成,必須使能 ADF4351 PLL和VCO,且必須設 置所需的輸出頻率。ADF4351的輸出頻率通過RFOUT引腳處 的開集輸出端提供,該引腳處需要一個并聯電感(或電阻) 和一個隔直電容。

ADCLK948 是一款SiGe低抖動時鐘扇出緩沖器,非常適合與 ADF4351配合使用,因為其最大輸入頻率(4.5 GHz)剛好高 于 ADF4351(4.4 GHz)。寬帶均方根加性抖動為75 fs。

為了模擬LVPECL邏輯電平,需要向 ADCLK948 的CLK輸入 端增加1.65 V的直流共模偏置電平。這可以通過使用電阻偏 置網絡來實現。缺少直流偏置電路會導致ADCLK948輸出 端的信號完整性降低。

常見變化

也可以使用 ADF4350小數N分頻(137 MHz至4400 MHz)和 ADF4360整數N分頻系列等其它集成VCO的頻率合成器。

與 ADCLK948 同一系列的其它可用時鐘扇出緩沖器有 ADCLK946(6路LVPECL輸出)、 ADCLK950ADCLK950(10路LVPECL輸 出)及 ADCLK954(12路LVPECL輸出)。

電路評估與測試

評估本電路時,利用 EVAL-ADF4351EB1Z 板作為時鐘源, 并略作修改。EVAL-ADF4351EB1Z板使用標準ADF4351編 程軟件,該軟件包含在評估板附帶的光盤上。此外還需要 ADCLK948/PCBZ,并且無需修改便可以直接使用。

設備要求

需要以下設備:

EVAL-ADF4351EB1Z 評估板套件,含編程軟件

ADCLK948PCBZ評估板

3.3 V電源

用于連接3.3 V電源和 ADCLK948PCBZ的兩條電纜

兩條長度相等且較短的SMA同軸電纜

高速示波器(2 GHz 帶寬)或等效器件

R&S FSUP26頻譜分析儀或等效器件

裝有Windows? XP、Windows Vista(32位)或Windows 7(32位)的PC

需要使用SMA同軸電纜,以便將EVAL-ADF4351EB1Z的OUTA+ 的 RFOUTA? pins 和EVAL-ADF4351EB1Z A?引腳與ADCLK948PCBZ的CLK0和CLK0 引腳相連。

功能框圖

本實驗中使用 ADCLK948PCBZ 和 EVAL-ADF4351EB1Z。這 些電路板通過一條SMA電纜連接至 ADCLK948PCBZ,如圖 1所示。

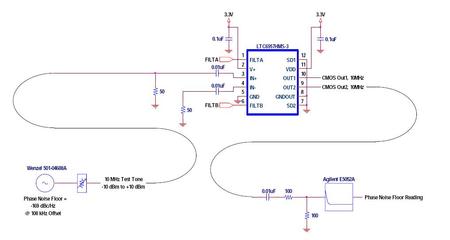

圖2. ADF4351邏輯電平測量配置

開始使用

UG-435用戶指南詳細說明了 EVAL-ADF4351EB1Z 評估軟件 的安裝和使用。 UG-435 還包含電路板設置說明以及電路板 原理圖、布局和物料清單。電路板上必要的修改是在隔直 電容之后插入100Ω電阻。這些電阻與3.3 V電源相連并接 地。對 RFOUTA+和RFOUTA?引腳都應該執行此操作,以提供1.65 V的共模電壓(高于所需的最低值1.5 V)。這樣可能就需 要去除這些傳輸線附近的阻焊膜。

UG-068 用戶指南包含關于 ADCLK948/PCBZ 評估板操作的類似信息。

邏輯電平測量

本例中,為準確測量高速邏輯電平,將Rohde & Schwarz RTO1024示波器與兩個RT-ZS30有源探頭配合使用。

在PC上安裝ADF435x軟件,具體做法說明如下:

根據UG-435中的硬件驅動程序說明將EVAL-ADF4351EB1Z連接至PC。

根據ADF435x軟件的屏幕截圖(見圖3)對ADF4351 PLL進 行編程。本例中選擇了1 GHz的RF頻率。

用兩條長度相等且較短的SMA電纜將EVALADF4351EB1Z 板的RFOUTA+ 和 RFOUTA?SMA 連接器與 ADCLK948/PCBZ板的CLK0CLK0/CLK0 SMA 連接器相連。

將ADCLK948/PCBZ的差分輸出OUT2/OUT2 與高速示波 器相連。有關1 GHz輸出的典型波形,請參見圖4。

圖3. ADF4351軟件設置

圖4. 1 GHz邏輯信號的ADCLK948示波器輸出,水平軸:200 ps/DIV,垂直軸:200 mV/DIV

相位噪聲和抖動測量

重復“邏輯電平測量”部分的第1至第4步。

將CLK2 未使用的CLK2輸出端與50Ω 負載相連(見圖5)。

通過一條SMA電纜將CLK2輸出端與信號源分析儀相連 (見圖5)。

測量信號的抖動性能。

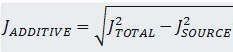

圖6顯示了ADF4351輸出端的相位噪聲,均方根抖動為 325.7 fs。圖7顯示了ADCLK948輸出端的相位噪聲。均方根 抖動為330.4 fs。

ADCLK948的加性抖動計算如下:√(330.4(sup)2(/sup) ? 325.7(sup)2(sup)) = 55.5 fs rms。ADCLK948數據手冊中的額定值 為75 fs rms。

圖5. ADF4351相位噪聲和抖動測量設置

圖6. 顯示了325.7 fs rms抖動的ADF4351輸出相位噪聲測量

圖7. 顯示了330.4 fs rms抖動的ADCLK948輸出相位噪聲測量

電子發燒友App

電子發燒友App

評論