除法運算。很多人覺得不就是除法嘛,直接打上/即可,但是,FPGA是不能正確綜合這個除法器的,綜合的結果只是一個固定數值,而不像其他微處理器。可以這么說,用FPGA實現除法運算是比較麻煩的。

2020-06-17 10:17:27 6533

6533

減法電路是基本集成運放電路的一種,算術運算電路主要包括數字**加法器電路、數字減法器電路、數字乘法器電路和數字除法器電路。

2024-02-19 10:00:17 310

310

CMOS是一個簡單的前道工藝,大家能說說具體process嗎

2024-01-12 14:55:10

問題。這種趨勢已經迫使大部分模擬基本組成部件重新設計,試圖保證它們的整體性能。在這些設計約束下。軌到軌操作在低壓設計中成為強制性的,目的是為了增大信噪比。在這篇文章里,我介紹了一種能達到AB類特性軌到軌CMOS模擬緩沖器的電路技巧,產生了具有低功耗和高的驅動能力的方法。

2019-07-19 06:24:12

設計一種成本較低,能夠代替實際光伏電池陣列來進行各種光伏實驗的太陽能電池模擬器。本文所設計的太陽能電池模擬器以BUCK電路為基礎,采用ARM控制,并加入了電流PI控制方式來改善系統動態性能和穩態精度。此外,本文還采用四折線法來對光伏電池陣列的特性曲線進行分段擬合,并進行了仿真驗證。

2019-07-16 07:17:49

一種倍頻控制單元,通過編程鎖頻倍數和壓控振蕩器延遲單元的跨導,有效擴展了鎖相環的鎖頻范圍。該電路基于Dongbu HiTek 0.18μm CMOS工藝設計,仿真結果表明,在1.8 V的工作電壓

2019-07-08 07:37:37

一種新型單相脈沖整流器的MATLAB仿真研究摘要:給出了一種新型的脈沖整流器,詳細地介紹了其工作原理和控制方案,并對該整流器及其控制系統建立了MATLAB仿真模型,仿真結果驗證了該方案的優越性

2021-07-06 07:45:56

一種新型過流保護電路的設計研究摘要:本文提出的過流保護電路利用運算放大器虛短虛斷的原理大大提高了對輸出電流的采樣精度,從而提高了電路的可靠性;并通過增加的折回電路,有效降低了LDO

2009-12-02 17:11:12

4.3 實例九 除法器設計4.3.1. 本章導讀要求掌握除法器原理,并根據原理設計除法器模塊以及設計對應的測試模塊,最后在 Robei可視化仿真軟件經行功能實現和仿真驗證。設計原理這個除法器的設計為

2021-11-12 07:03:52

使用AD633與AD711按照官方提供的電路搭建了一個除法器,在使用中發現與實際不符,求解答 一. 這是輸入的兩個信號,最上面一個作為被除信號,下面一個作為除信號。 這是通過除法器后的信號,其中最上一

2019-02-12 14:10:52

本帖最后由 gk320830 于 2015-3-5 13:40 編輯

手冊上說可以接成除法器,但沒有給出實際電路,望高手指點。。。

2012-03-25 14:20:07

請問一下大家有沒有用Xilinx的除法器IP核的,版本是V3.0的!我們在做有符號數除法的過程中運算結果經常出錯!原先做的產品,Divider的工作頻率是40M,后來工作頻率變為62M時就經常出錯

2015-03-06 19:42:16

我們通常分為仿真驗證和板級驗證,在設計初步完成功能甚至即將上板調試前,通過EDA仿真工具模擬實際應用進行驗證是非常有效可行的手段,它能夠盡早的發現設計中存在的各種大小bug,避免設計到了最后一步才返工

2019-04-10 06:35:34

這里的被除數與除數可以是量化完之后的結果,但是量化要注意被除數與除數乘以相同的數。 第二個注意事項 除法器的下面的選項是控制除法器每隔多少個時鐘有一個有效的輸出: 第三個注意事項

2021-01-08 17:00:55

`大蝦們,小女子最近調程序的時候用到了ise ip core的除法器,但是調用modelsim仿真的時候發現木有進行除法啊,單獨寫了個除法器也還是用不了,這是什么情況呢?(vhdl寫的程序哈)`

2013-06-15 11:52:45

一個變量除以一個常數81,怎么寫啊 。想直接調用IP核,可是還沒法控制什么時候進行除法運算。又不想自己寫除法器求指點啊!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!

2013-04-16 15:08:35

目前最先進的模擬和射頻電路,正廣泛應用于消費電子產品、無線通訊設備、計算機和網絡設備的SoC中。它們帶來了一系列驗證方面的挑戰,而這些挑戰往往是傳統SPICE、FastSPICE和射頻仿真軟件無法

2019-10-11 06:39:24

隨著射頻無線通信事業的發展和移動通訊技術的進步,射頻微波器件的性能與速度成為人們關注的重點,市場對其的需求也日益增多。目前,CMOS工藝是數字集成電路設計的主要工藝選擇,對于模擬與射頻集成電路來說,有哪些選擇途徑?為什么要選擇標準CMOS工藝集成肖特基二極管?

2019-08-01 08:18:10

介紹一種全局快門CMOS成像傳感器

2021-05-28 06:12:14

本設計實例介紹的是一種簡單的雙芯片CMOS電路。

2021-05-10 06:48:22

想問一下大家 單片機使用硬件除法器求出的商和余數數據怎么處理呢

2023-10-30 08:28:51

哪位有模擬除法器的電路仿真,我需要一個簡單的除法運算電路。MULTISIM10上面的除法器只是個代號沒有實際的型號,我用AD532來做結果不行。

2013-12-16 11:10:24

得到銳利的圖像。 3 結 語 為了提高CMOS圖像傳感器的圖像質量,通過對圖像主要的噪聲源以及圖像失真的分析,本文提出了一種新型的CMOS有源像素圖像傳感器。該CMOS圖像傳感器使用4T有源像素,大大提高了圖像傳感器的靈敏度。通過在傳感器中集成圖像預處理功能,對改善圖像的質量起到了很好的效果。:

2018-11-14 15:24:59

基于Cadence virtuoso與Mentor Calibre的CMOS模擬集成電路版圖該如何去設計?怎樣去驗證一種基于Cadence virtuoso與Mentor Calibre的CMOS模擬集成電路版圖?

2021-06-22 06:12:49

定點除法器的輸出是商和余數的形式,但是我想讓他表示成小數的形式(因為最后要送到數碼管顯示),該怎么裝換?求大神,給點思路也可以!總共是8位顯示,而整數部分和小數部分的位數不定?怎么設計

2014-05-15 20:01:12

提出一種基于乘法器的模擬電路參數測量方法,闡述了該方法的基本原理,并進行理論分析和數學推導.利用LabVIEW軟件對該方法建模仿真.實驗結果表明,運用基于乘法器的模擬電路參數測量方法實現模擬電路參數

2010-06-02 10:07:53

如何利用0.18μm CMOS工藝去設計16:1復用器?以及怎樣去驗證這種復用器?

2021-04-09 06:39:47

如何利用單片機設計一種模擬電磁曲射炮?

2021-11-11 07:17:58

什么是硅基CMOS技術?如何去實現一種石墨烯CMOS技術?

2021-06-17 07:05:17

如何去設計軌到軌CMOS模擬緩沖器?怎樣對軌到軌CMOS模擬緩沖器進行仿真?

2021-04-23 06:35:57

怎么在O.5μm CMOS工藝條件下設計一種采用電流反饋實現遲滯功能的旁路電壓控制電路?

2021-04-14 06:53:08

本文設計了一種低插入損耗、高隔離度的全集成超寬帶CMOS射頻收發開關芯片。

2021-05-24 06:58:23

本文設計了一種用于耳機驅動的CMOS功率放大器,該放大器采用0.35μm雙層多晶硅工藝實現,驅動32Ω的電阻負載。該設計采用三級放大兩級密勒補償的電路結構,通過提高增益帶寬來提高音頻放大器的性能。

2021-04-23 06:31:27

本文采用0.18 μm CMOS工藝設計了一種適用于TI-ADC的高速、低功耗開環T&H電路。

2021-04-20 06:58:59

本文提出了一種基于FPGA的NoC驗證平臺。詳細討論了該驗證平臺中FPGA硬件平臺和NoC軟件的基本功能,并闡述了TG/R,MPU,MPI以及NoC軟件的可重用性等特點。通過一個實例仿真驗證的結果說明了該驗證平臺的基本功能和優越性。

2021-05-06 07:20:48

文章主要在文獻基礎上設計了一種新型的CMOS電流反饋運算放大器,使用0.5μmCMOS工藝參數(閾值電壓為0.7V),模擬結果獲得了與增益無關的帶寬、極大的轉換速率。電路參數為:81db的開環增益、87度的相位裕度、123db共模抑制比,以及在1.5V電源電壓下產生了約6.2mW的功耗。

2021-06-04 06:21:47

根據電壓控制增益電路理論及放大器設計原理,設計制作了一種基于GaAs工藝的可變增益功率放大器單片微波集成電路( MMIC)。采用電路仿真ADS軟件進行了原理圖及版圖仿真,研究了增益控制電路在放大器中的位置對性能的影響。

2021-04-06 08:32:23

課程名稱:CMOS模擬集成電路設計課程簡介:該課程主要是版圖類課程的后續,主要集中講解了CMOS模擬集成電路設計,內容包括CMOS工藝基礎,MOS器件物理與模型,單級放大器,差分放大器,電流鏡電路

2021-11-10 07:26:01

反相器的速度與哪些因素有關?什么是轉換時間和傳播延遲呢?怎樣去設計一種CMOS三態緩沖器的電路呢?

2021-10-20 06:24:39

怎樣去設計一種基于stm32f103r6的模擬交通燈呢?如何對基于stm32f103r6的模擬交通燈進行proteus仿真呢?

2021-11-10 06:30:26

,集成度、功耗、芯片的成本以及研發周期是決定一個公司選擇工藝的重要方面,下面從這幾個方面來闡述標準CMOS工藝在高速模擬、混合信號處理領域的發展潛力。 2 標準CMOS工藝在高速模擬、混合信號處理領域

2018-11-26 16:45:00

求一種低壓低功耗CMOS電流反饋運算放大器設計方案

2021-04-25 08:27:09

請求大神分享一種改進的Wallace樹型乘法器的設計

2021-04-14 06:41:13

固網短信電話專用SoC芯片介紹一種數模混合SoC設計協同仿真的驗證方法

2021-04-23 06:06:39

求一種端到端的定制IC模擬與驗證解決方案如何對存儲器和混合信號設計進行仿真?

2021-06-22 07:58:50

求大神分享一種基于Verilog計算精度可調的整數除法器的設計

2021-04-29 06:30:43

有哪位親知道除法器選用哪種型號的比較好?是用作PSD位置傳感器的外圍電路,我在網上找到的最便宜的一種是一百多,不知道可不可靠。。另外,用運放實現電流到電壓的轉換 電阻和相位補償的電容取多少合適呢?我看到上面有寫電阻不宜過大 易產生自激,但所給原理圖上用了1M。。求各路大神指點

2014-08-18 23:35:53

的匹配有嚴格要求,否則線性度很難保證,這樣也就對制造工藝提出了較高的要求。針對這一缺點,本文提出了一種新型模擬乘法器結構,它采用減法電路來提高電路的線性度。

2019-07-16 07:40:41

)。一般來說,面對一個仿真問題最好是首先試試ode45。ode23:二/三階龍格-庫塔法,它在誤差限要求不高和求解的問題不太難的情況下,可能會比ode45更有效。也是一個單步解法器。ode113:是一種階

2011-07-13 14:18:18

本文提出了一種CMOS圖像傳感器大動態范圍自適應曝光的設計。

2021-06-04 06:57:44

模擬直流調速系統的組成和工作原理是什么?怎樣去設計一種模擬直流調速系統?

2021-04-30 06:18:57

這是一個高速硬件除法器,要求畫出此硬件的除法器的工作流程圖。說明其工作原理特別是高速原理。要求有仿真時序波形圖并說出說明在fpga上驗證器硬件功能。

2020-12-17 09:10:03

數模混合信號仿真已經成為SoC芯片驗證的重要環節。文章以一款固網短信電話專用SoC芯片為例,介紹一種使用Synopsys公司的NanoSim-VCS協同仿真環境進行仿真的驗證方法,并給出驗證結

2009-05-15 15:41:26 19

19 數模混合信號仿真已經成為SoC芯片驗證的重要環節。文章以一款固網短信電話專用SoC芯片為例,介紹一種使用Synopsys公司的NanoSim-VCS協同仿真環境進行仿真的驗證方法,并給出驗證結

2009-05-15 15:41:26 5

5 TI推出的CDC706是目前市場上體積最小且功能強大的PLL合成器/乘法器/除法器之一。盡管其物理外形非常小巧,但卻極為靈活。該器件能夠在特定輸入頻率下生成幾乎獨立的輸出頻率。

2009-11-26 14:35:47 21

21 AD534是一款單芯片激光調整四象限乘法器除法器,其精度規格以前只有昂貴的混合或模塊化產品才有。無需任何外部調整,AD534L的最大乘法誤差保證為0.25%。出色的電源抑制性能、低溫度系數以及片內

2023-08-09 16:52:53

為了實現變頻控制,產生一個與輸入信號同頻同相的電壓信號,使輸入電流跟隨輸入電壓,設計了一種基于BCD工藝的模擬乘法器,并闡述了該電路設計的工作原理和結

2010-07-10 16:35:56 20

20 描述AD534是一款單芯片激光調整四象限乘法器/除法器,可提供以前只有昂貴的混合式或模塊式產品才具有的精度規格。無需外部調整便可保證±0.25%的最大乘法誤差。該器件具有出色的電源抑制、低溫度系數

2024-01-11 15:27:16

模擬乘法器在運算電路中的應用

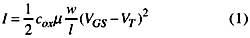

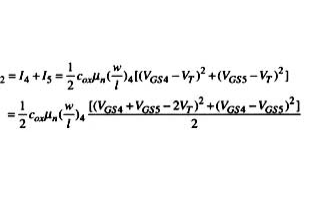

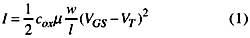

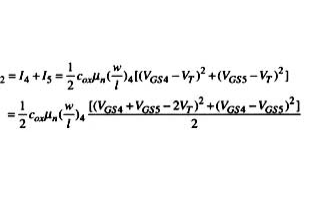

8.6.1 乘法運算電路

8.6.2 除法運算電路

8.6.3 開方運算電路

2010-09-25 16:28:45 145

145 AD532是首款預調整的單芯片乘法器/除法器;無需任何外部調整電阻或輸出運算放大器,即可保證±1.0%的最大乘法誤差和±10 V的輸出電壓范圍。AD532經過內部調整,易于使用,為設計

2010-10-02 09:37:50 132

132 并行除法器 ,并行除法器結構原理是什么?

1.可控加法/減法(CAS)單元 和陣列乘法器非常相似,陣列式除法器也是一種并行運算部件,采用大規模集成

2010-04-13 10:46:30 14666

14666 除法器對數運算電路的應用

由對數電路實現除法運算的數學原理是:

2010-04-24 16:07:27 2520

2520

這個模擬乘法器原理圖可作為分壓器和乘數。該電路是由四個部分組成。晶體管匹配確定乘法電路的精確度。

2012-03-13 16:58:36 22787

22787

除法器是電子技術領域的基礎模塊,在電子電路設計中得到廣泛應用。目前,實現除法器的方法有硬件實現和軟件實現兩種方法。硬件實現的方法主要是以硬件的消耗為代價,從而有實

2012-05-24 09:41:04 1808

1808

主要內容為基于 Multisim 的模擬乘法器應用設計與仿真。闡述了雙邊帶調幅

及普通調幅、同步檢波、混頻、乘積型鑒相電路的原理,并在電路設計與仿真平

臺 Multisim11 仿真環境中創建

2017-02-07 21:04:01 25

25 本文為大家介紹五款乘法器電路設計方案,包括五款模擬電路設計原理及仿真程序分享,以供參考。

2018-01-17 18:03:30 53772

53772

在集成電路系統中,模擬乘法器在信號調制解調、鑒相、頻率轉換、自動增益控制和功率因數校正控制等許多方面有著非常廣泛的應用。實現模擬乘法器的方法有很多,按采用的工藝不同,可以分為三極管乘法器和CMOS乘法器。

2019-05-31 08:20:00 2618

2618

CMOS 模擬集成電路設計與傳統分立元件模擬電路設計最大的不同在于,所有的有源和無源器件都制作在同一襯底上,尺寸極其微小,無法再用電路板進行設計驗證。因此,設計者必須采用計算機仿真和模擬的方法來驗證電路性能。模擬集成電路設計包括若干階段,圖一表示的是 CMOS 模擬集成電路設計的一般流程。

2020-12-16 22:22:00 22

22 乘法器(multiplier)是一種完成兩個互不相關的模擬信號相乘作用的電子器件。它可以將兩個二進制數相乘,它是由更基本的加法器組成的。乘法器可以通過使用一系列計算機算數技術來實現。乘法器不僅作為

2021-02-18 15:08:01 24395

24395

在集成電路系統中,模擬乘法器在信號調制解調、鑒相、頻率轉換、自動增益控制和功率因數校正控制等許多方面有著非常廣泛的應用。實現模擬乘法器的方法有很多,按采用的工藝不同,可以分為三極管乘法器和CMOS乘法器。

2021-03-23 09:40:19 3930

3930

AD533:低成本乘法器、除法器、平方器、平方器、根過時數據表

2021-04-30 21:05:33 3

3 AD533:低成本乘法器、除法器、平方器、平方根過時數據表

2021-05-07 10:50:33 20

20 AD734:10 MHz四象限乘法器/除法器數據表

2021-05-15 10:18:05 12

12 簡化合成器的有源乘法器和除法器

2021-05-16 17:15:02 9

9 CMOS模擬集成電路設計與仿真(基本版)教材免費下載。

2021-05-31 10:55:38 0

0 4.3 實例九 除法器設計4.3.1. 本章導讀要求掌握除法器原理,并根據原理設計除法器模塊以及設計對應的測試模塊,最后在 Robei可視化仿真軟件經行功能實現和仿真驗證。設計原理這個除法器

2021-11-07 10:51:04 18

18 14 級紋波進位二進制計數器/除法器和振蕩器-HEF4060B_Q100

2023-02-15 18:53:56 0

0 14 級紋波進位二進制計數器/除法器和振蕩器-HEF4060B

2023-02-15 18:54:07 1

1 本文是本系列的第四篇,本文主要介紹FPGA常用運算模塊-除法器,xilinx提供了相關的IP以便于用戶進行開發使用。

2023-05-22 16:20:45 1840

1840

使用IAR IDE仿真RL78內置硬件乘法器和除法器注意事項

2023-10-30 17:04:14 468

468

電子發燒友App

電子發燒友App

評論