模擬數(shù)字轉(zhuǎn)換器(ADC)與數(shù)字模擬轉(zhuǎn)換器(DAC)自數(shù)字時(shí)代之初就存在,自70年代末期、80年代初期,德州儀器(TI)率先推出單芯片數(shù)字信號(hào)處理器(DSP),提供工程師設(shè)計(jì)系統(tǒng)所需工具,輕易超越模擬組件的效能。

?

早期數(shù)據(jù)轉(zhuǎn)換器速率相對(duì)緩慢,并使用并聯(lián)接口連接DSP或處理器,隨著制程技術(shù)進(jìn)步,數(shù)據(jù)轉(zhuǎn)換器的速度及動(dòng)態(tài)范圍(位數(shù))也一并改善,因此需要更快、更寬的總線。

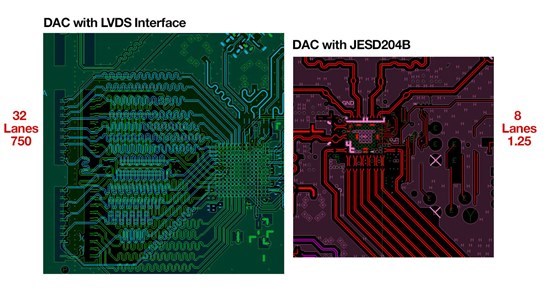

今日現(xiàn)代數(shù)據(jù)轉(zhuǎn)換器中,十億取樣(Gigasample)的每秒轉(zhuǎn)換率都遠(yuǎn)高于12位,換算成總線傳輸速率,則超過每秒15億字節(jié),故工程師使用印刷電路板連接DSP、處理器或現(xiàn)場(chǎng)可編程門陣列(FPGA)時(shí),都會(huì)面臨挑戰(zhàn)。系統(tǒng)內(nèi)若有多個(gè)ADC或DAC,且模擬輸入或輸出必須相位一致,則情況會(huì)更加復(fù)雜,并聯(lián)總線必須與電子長(zhǎng)度及確定性延遲相符,對(duì)配置更是場(chǎng)夢(mèng)魘。

早在超高速數(shù)據(jù)轉(zhuǎn)換器問世之前,業(yè)界便已意識(shí)到這項(xiàng)問題存在,因此推出串行化低電壓差分訊號(hào)(LVDS)接口以降低互連數(shù),這項(xiàng)接口排列并聯(lián)總線后,提供LVDS位頻率找回?cái)?shù)據(jù),但因?yàn)轭l率與數(shù)據(jù)路徑的關(guān)系,路由仍是項(xiàng)問題。

延續(xù)串行化概念 標(biāo)準(zhǔn)規(guī)范持續(xù)修正

不過在此方案下,單一封裝與單一頻率內(nèi)可包括多個(gè)數(shù)據(jù)轉(zhuǎn)換器,至今仍有些應(yīng)用藉由這種方式減少針腳數(shù),例如德儀的ADC3445在單一48針腳、8平方厘米的封裝內(nèi),包含四個(gè)125-Msample/s、14位ADC。

到了21世紀(jì)初,數(shù)據(jù)轉(zhuǎn)換器速率的提升明顯造成路由問題,美國(guó)電子工程設(shè)計(jì)發(fā)展聯(lián)合協(xié)會(huì)(JEDEC)因此在2006年推出JESD204標(biāo)準(zhǔn),延續(xù)串行化接口概念,使用3.125Gb/s聯(lián)機(jī)速率,并實(shí)行編碼及框架處理,免除額外數(shù)據(jù)頻率需求。原始標(biāo)準(zhǔn)僅提供單一通道,且欠缺校準(zhǔn)方法,為了確保多部數(shù)據(jù)轉(zhuǎn)換器的相位一致,需要共同的框架頻率。

2008年4月,JEDEC推出A修正版,為高吞吐量增加通道,但仍需共同框架頻率才能同步;2011年7月推出B修正版,提高線路速率至12.5Gb/s,并支持確定性延遲(對(duì)相位一致非常重要),以及數(shù)據(jù)轉(zhuǎn)換器同步的內(nèi)部方式。

定義實(shí)體接口 提供更大信道

JESD204B接口包含一項(xiàng)或多項(xiàng)高速、單向、電流模式邏輯(CML)差分對(duì),載運(yùn)數(shù)據(jù)轉(zhuǎn)換器的數(shù)據(jù)稱為「信道」。信道數(shù)量與串行化LVDS接口不同,無須與轉(zhuǎn)換器數(shù)量相當(dāng),但與PCI Express同樣為接口提供更大信道,這是一般改用JESD204B時(shí)常出現(xiàn)的誤解。

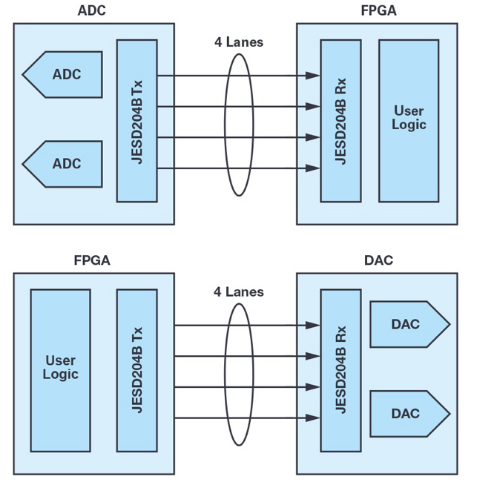

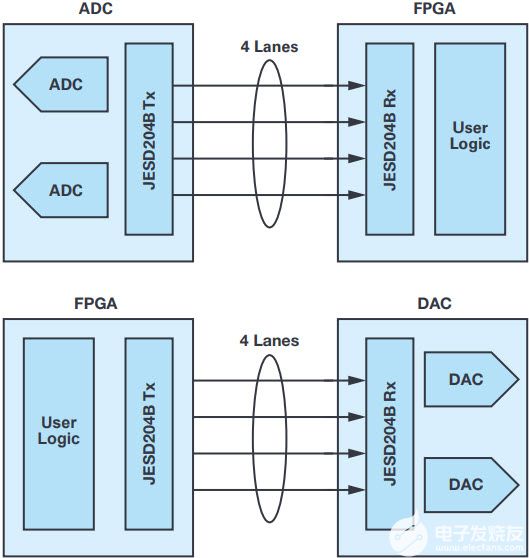

其他三種針腳也很重要:裝置頻率(DEVCLK)在早期修正版本稱為「框架頻率」、系統(tǒng)參考訊號(hào)(SYSREF)、主動(dòng)低同步針腳(/SYNC),依據(jù)裝置模式不同,這些額外針腳可記錄各項(xiàng)時(shí)間,如模擬轉(zhuǎn)換,以及數(shù)據(jù)在數(shù)據(jù)轉(zhuǎn)換器與處理組件之間的移動(dòng)(圖1)。

圖1 多項(xiàng)JESD204B接口連接范例

數(shù)據(jù)轉(zhuǎn)換器運(yùn)用DEVCLK取得多項(xiàng)內(nèi)部頻率訊號(hào),例如「內(nèi)部框架頻率」傳輸數(shù)據(jù)、「取樣頻率」記錄轉(zhuǎn)換時(shí)間、「地方多重框架頻率」(LMFC)建立確定性延遲。SYSREF為相位參考訊號(hào),在子類別內(nèi)汲取LMFC(在子類別零或子類別二不使用);/SYNC訊號(hào)可用于各子類別數(shù)據(jù)傳輸同步,以及子類別二的LMFC相位參考。

確立數(shù)據(jù)格式 傳輸更穩(wěn)定

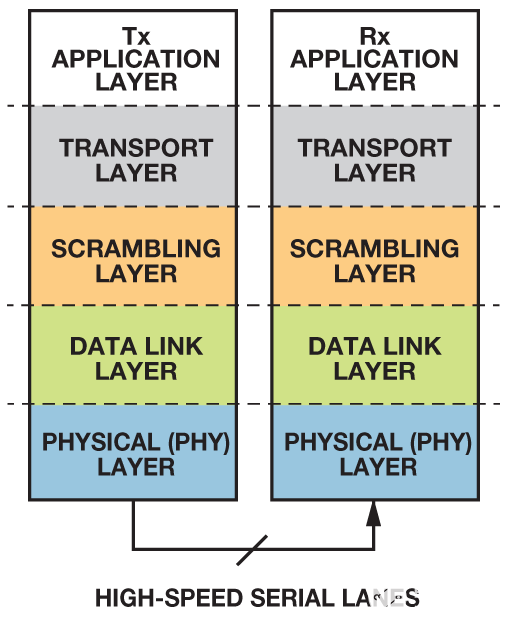

相較于簡(jiǎn)易串行化LVDS接口,JESD204B使用的模型近似于網(wǎng)絡(luò)協(xié)議或開放系統(tǒng)接口(OSI),其中每一層各有不同功能,編碼端先后執(zhí)行每一層的功能,接收端執(zhí)行順序則相反,以重建數(shù)據(jù)。

每一層發(fā)揮不同功能,讓傳輸器與接收器數(shù)據(jù)通過更穩(wěn)定,JESD204B標(biāo)準(zhǔn)共有傳輸、擾頻(非必要,但建議使用)、數(shù)據(jù)鏈路、實(shí)體等四層。

傳輸層功能較復(fù)雜,將數(shù)據(jù)以8位為單位分組,在傳輸側(cè)每個(gè)訊框內(nèi)包含多個(gè)8位,而接收側(cè)順序則相反。對(duì)8位數(shù)據(jù)轉(zhuǎn)換器相當(dāng)簡(jiǎn)單,但對(duì)于11位數(shù)據(jù)轉(zhuǎn)換器等其他組件則較為復(fù)雜,也會(huì)在串流內(nèi)加入控制位,向接收器溝通狀態(tài)信息(圖2)。

圖2 在此案例中,傳輸層可連結(jié)各層對(duì)抗應(yīng),在串流內(nèi)植入控制位,向接收器溝通狀態(tài)信息。

非必要的擾頻層可建立隨機(jī)數(shù)據(jù)模式,將系統(tǒng)內(nèi)噪聲與相關(guān)聯(lián)訊號(hào)降至最低,藉由固定多項(xiàng)式1 + X^14 + X^15,使用序列反饋移位寄存器及OR互斥閘,在編碼與譯碼對(duì)稱。這項(xiàng)簡(jiǎn)易的訊號(hào)頻譜展開方式之下,只要自連結(jié)層接收兩個(gè)8字節(jié)后,接收器的去擾頻器就會(huì)鎖住,雖然這項(xiàng)功能并非必要,但相當(dāng)有助于頻譜純凈度。

數(shù)據(jù)鏈路層負(fù)責(zé)8b/10b編碼,讓8字節(jié)與10位標(biāo)準(zhǔn)符號(hào)之間轉(zhuǎn)換,本層亦負(fù)責(zé)建立工作連結(jié),包括訊框與通道校準(zhǔn),數(shù)項(xiàng)標(biāo)準(zhǔn)8b/10b符號(hào)為此預(yù)留,并監(jiān)控連結(jié)體質(zhì)。編碼亦包括20%的開銷懲罰,未來版本可能移往64/66b等更高階的編碼,以重拾接口內(nèi)流失的帶寬。

物理層純粹為驅(qū)動(dòng)器與接收器,移動(dòng)位與頻率數(shù)據(jù)復(fù)原(CDR)線路,實(shí)體接口運(yùn)用交流電(AC)耦合CML驅(qū)動(dòng)器與接收器,8b/10b編碼提供直流電(DC)平均,并避免AC耦合時(shí)發(fā)生基線飄移;編碼也為CDR提供足夠的邊緣過渡,在建立鏈接時(shí)迅速鎖住數(shù)據(jù)。

總而言之,數(shù)據(jù)轉(zhuǎn)換器與處理組件建立鏈接時(shí),會(huì)使用這四層,并且穩(wěn)定地從發(fā)送器傳輸數(shù)據(jù)控制器數(shù)據(jù)及控制信息至接收器。

為達(dá)到向后兼容,JEDEC建立「子類別」概念,讓界面可應(yīng)用于各種運(yùn)作模式,子類別零是與A修正版兼容的模式,但亦支持12.5Gb/s信道速率,這項(xiàng)模式與A修正版相同,支持多種同步數(shù)據(jù)轉(zhuǎn)換器,但并不支持確定性延遲。

建立子類別 達(dá)到向后兼容

數(shù)據(jù)轉(zhuǎn)換器之間的延遲或許固定,但啟動(dòng)時(shí)仍會(huì)變化,所以系統(tǒng)設(shè)計(jì)人員必須提供解決方案,判斷個(gè)別數(shù)據(jù)轉(zhuǎn)換器的數(shù)據(jù)何時(shí)會(huì)抵達(dá)FPGA或處理器,而且此模式并未使用SYSREF。子類別一提供確定性延遲,以及內(nèi)部多重裝置同步,同時(shí)使用內(nèi)部訊框、地方多重框架頻率及SYSREF頻率訊號(hào)。數(shù)據(jù)轉(zhuǎn)換器與處理組件的符號(hào)串行傳輸時(shí),使用內(nèi)部框架頻率,而LMFC提供已知延遲的參考。

DEVCLK加上SYSREF訊號(hào)的相位決定內(nèi)部框架頻率與LMFC,由于在此模式中,DEVCLK與SYSREF關(guān)系密切,SYSREF必須與裝置頻率同步,進(jìn)而限制配置,讓兩項(xiàng)訊號(hào)能夠相符,不過因?yàn)樽宇悇e零之中的SYNC訊號(hào),所以數(shù)據(jù)信道無須相符。

在子類別二之中,每項(xiàng)裝置的內(nèi)部框架頻率與LMFC相同,與子類別一無異,但此時(shí)需要SYNC訊號(hào)達(dá)到同步與確定性延遲,在本模式中,SYNC訊號(hào)的相位可校準(zhǔn)內(nèi)部框架頻率與LMFC,且必須與DEVCLK達(dá)到源同步。由于DEVCLK及/SYNC的時(shí)間需求嚴(yán)格,這項(xiàng)模式并不推薦用于極高采樣率。

介紹完基本知識(shí)后,接著說明如何相連,讓模擬訊號(hào)抵達(dá)或離開處理組件。數(shù)據(jù)轉(zhuǎn)換開始前,必須先建立多項(xiàng)速率,許多工程師也在此遲疑,因?yàn)檫@項(xiàng)接口的組成選項(xiàng)眾多,使用FPGA建立JESD204B接口也相當(dāng)復(fù)雜。

建立連接以控制模擬訊號(hào)

首先得建立數(shù)據(jù)轉(zhuǎn)換器與處理組件的鏈接,必須確立低態(tài)有效訊號(hào)/SYNC(輸入至發(fā)送器側(cè)),發(fā)送器接口即可開始傳送K28.5 comma符號(hào),讓接收器CDR可相位鎖定比特流,并找到數(shù)據(jù)流的字符邊界。若鏈接包括多條通道,并在子類別零之中運(yùn)作,/SYNC訊號(hào)必須混合后,同時(shí)送至發(fā)送器,子類別一與子類別二則無此要求。

達(dá)成代碼組同步(CGS)后,/SYNC即可停止啟動(dòng),在下一項(xiàng)非K28.5符號(hào)中,接收器就會(huì)校準(zhǔn)訊框邊界,也啟動(dòng)初始通道同步(ILA)序列,校準(zhǔn)多條通道。即便具備擾頻功能,這項(xiàng)序列也不受影響。ILA在傳輸器側(cè)傳輸數(shù)據(jù),長(zhǎng)度為四項(xiàng)多重訊框,多重訊框以K28.0符號(hào)為起點(diǎn)(子序列起點(diǎn)),并以K28.3符號(hào)為終點(diǎn)(信道校準(zhǔn)子元)(圖3)。

圖3 接收器訊框邊界校準(zhǔn)完成后,會(huì)觸發(fā)JESD204B最初通道同步。

四項(xiàng)多重訊框傳輸完成后,就會(huì)啟動(dòng)擾頻,將用戶數(shù)據(jù)傳輸至接收器,建議可善用許多信息轉(zhuǎn)換器或FPGA JESD204B IP區(qū)塊內(nèi)建的診斷功能,許多都包含既有模式的傳輸選項(xiàng),如斜波、正弦波等,此模式常使用數(shù)據(jù)轉(zhuǎn)換器的完整動(dòng)態(tài)范圍,以仿真實(shí)際轉(zhuǎn)換后的數(shù)據(jù)。

也可以在傳輸層的數(shù)據(jù)轉(zhuǎn)換器測(cè)試模式中,植入預(yù)決定的8字節(jié)模式,比除錯(cuò)測(cè)試模式簡(jiǎn)單。開機(jī)時(shí),若使用邏輯分析工具或FPGA編碼監(jiān)控信道流量,記得關(guān)閉擾頻,讓模式更容易顯現(xiàn)。

JESD204B標(biāo)準(zhǔn)遠(yuǎn)比本文介紹內(nèi)容復(fù)雜許多,若不熟悉如何運(yùn)作,本文或能提供接口建置部分見解,隨著數(shù)據(jù)轉(zhuǎn)換器速度提升,這項(xiàng)標(biāo)準(zhǔn)必將持續(xù)拓展,也增加吞吐量,滿足使用這項(xiàng)接口的數(shù)據(jù)轉(zhuǎn)換器復(fù)雜度及控制需求。

電子發(fā)燒友App

電子發(fā)燒友App

評(píng)論