在現代電子系統的核心組件中,內存的性能與穩定性至關重要。高密度DDR4芯片作為當前內存技術的杰出代表,不僅憑借其卓越的性能表現和微型化技術贏得了廣泛認可,還在多個方面展現出了獨特的優勢。

2024-03-22 14:47:42 62

62

Xilinx FPGA芯片擁有多個系列和型號,以滿足不同應用領域的需求。以下是一些主要的Xilinx FPGA芯片系列及其特點。

2024-03-14 16:24:41 213

213 電子發燒友網站提供《完整的DDR2、DDR3和DDR3L內存電源解決方案同步降壓控制器TPS51216數據表.pdf》資料免費下載

2024-03-13 13:58:12 0

0 電子發燒友網站提供《適用于DDR2、DDR3、DDR3L和DDR4且具有VTTREF緩沖基準的TPS51206 2A峰值灌電流/拉電流DDR終端穩壓器數據表.pdf》資料免費下載

2024-03-13 13:53:03 0

0 該內存速度高達5600MT/s,并可同時兼容5200和4800 MT/s。據詳情頁介紹,其工作電壓僅為1.1V,相較于DDR4 3200內存,性能提升幅度為1.5倍,且將于本月底開始出貨。

2024-03-13 11:43:05 91

91 電子發燒友網站提供《具有同步降壓控制器、2A LDO和緩沖基準的TPS51916完整DDR2、DDR3、DDR3L和DDR4存儲器電源解決方案數據表.pdf》資料免費下載

2024-03-13 11:24:34 0

0 電子發燒友網站提供《具有同步降壓控制器、2A LDO和緩沖基準的TPS51716完整DDR2、DDR3、DDR3L、LPDDR3和DDR4內存電源解決方案數據表.pdf》資料免費下載

2024-03-13 11:13:44 0

0 電子發燒友網站提供《完整的DDR、DDR2和DDR3內存電源解決方案同步降壓控制器數據表.pdf》資料免費下載

2024-03-13 10:16:45 0

0 DDR5內存相對于DDR4有更高的內部時鐘速度和數據傳輸速率,從而提供更高的帶寬。DDR5的傳輸速率可以達到6400MT/s以上,比DDR4的最高傳輸速率提高了一倍以上。

2024-03-12 11:23:34 118

118 電子發燒友網站提供《TPS65295完整 DDR4 存儲器電源解決方案數據表.pdf》資料免費下載

2024-03-06 10:17:54 0

0 Intel Enpirion?電源解決方案Intel? Enpirion?電源解決方案是高頻、高效電源管理器件,用于FPGA(現場可編程門陣列)、SoC(片上系統)、 CPU(中央處理單元

2024-02-27 11:50:19

DDR6和DDR5內存的區別有多大?怎么選擇更好? DDR6和DDR5是兩種不同的內存技術,它們各自在性能、功耗、帶寬等方面都有不同的特點。下面將詳細比較這兩種內存技術,以幫助你選擇更適合

2024-01-12 16:43:05 2854

2854 硬件世界拉斯維加斯現場報道:CES 2024大展期間,雷克沙帶來了豐富的存儲方案,涵蓋SSD、內存、存儲卡等,包括頂級的PCIe 5.0 SSD、DDR5高頻內存。

2024-01-12 10:32:27 282

282

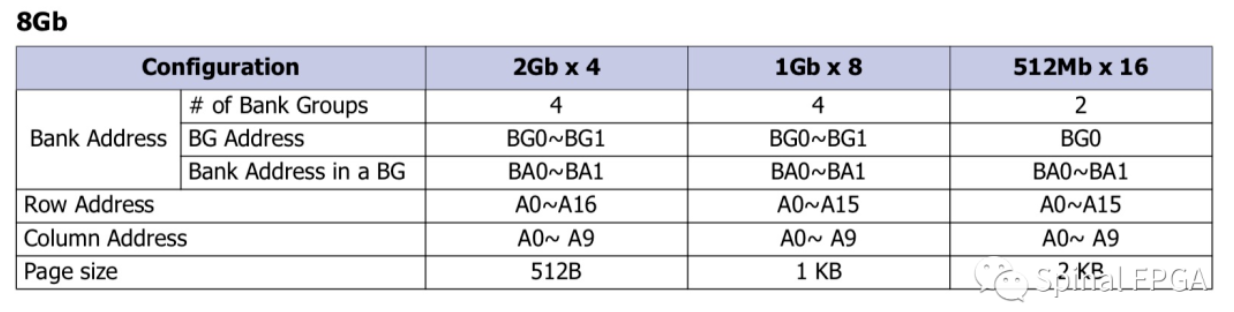

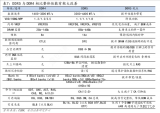

DDR5已經開始商用,但是有的產品還才開始使用DDR4。本文分享一些DDR4的測試內容。DDR4 和前代的 DDR3 相比, 它的速度大幅提升,最高可以達到 3200Mb/s,這樣高速的信號,對信號完整性的要求就更加嚴格,JESD79‐4 規范也對 DDR4 信號的測量提出了一些要求。

2024-01-08 09:18:24 463

463

國產高性能、低功耗通用計算微處理器的設計研發和產業化推廣。飛騰派是一款面向行業工程師、學生和愛好者的開源硬件,采用飛騰嵌入式四核處理器,兼容ARM V8架構,板載64位 DDR4內存,分為2G和4G兩個版本

2024-01-02 22:43:09

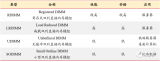

由于內存接口芯片的大規模商用要經過下游廠商的多重認證,還要攻克低功耗內存接口芯片的核心技術難關,從 DDR4 世代開始,全球內存接口芯片廠商僅剩 Rambus、瀾起科技和瑞薩(原 IDT)三家廠商。

2024-01-02 10:36:52 194

194

在DDR4年代,芝奇與阿斯加特成功完成逆襲,從原先的落落無名轉變為如今受到廣大DIY玩家追捧的內存廠商。

2023-12-29 10:41:00 247

247

)

DDR3內存條,240引腳(120針對每側)

DDR4內存條,288引腳(144針對每側)

DDR5內存條,288引腳(144針對每側)

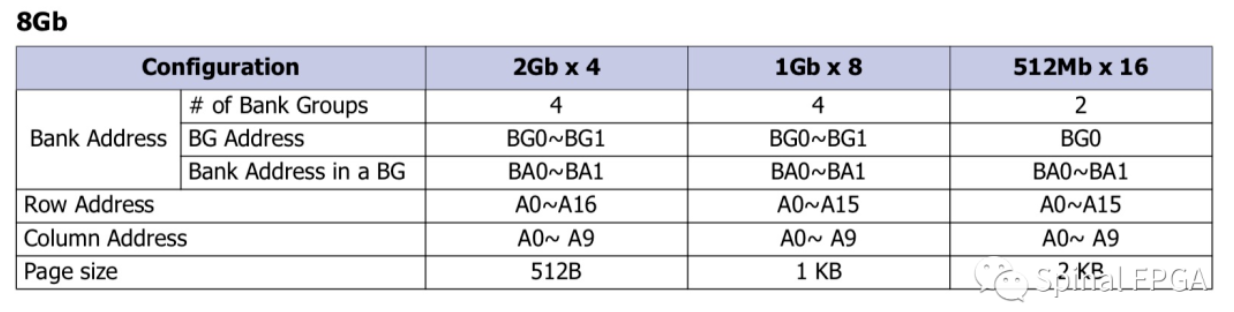

DDR芯片引腳功能如下圖所示:

DDR數據線的分組

2023-12-25 14:02:58

)

DDR3內存條,240引腳(120針對每側)

DDR4內存條,288引腳(144針對每側)

DDR5內存條,288引腳(144針對每側)

DDR芯片引腳功能如下圖所示:

DDR數據線的分組

2023-12-25 13:58:55

內存溢出與內存泄漏:定義、區別與解決方案? 內存溢出和內存泄漏是計算機科學中常見的問題,在開發和調試過程中經常會遇到。本文將詳細介紹內存溢出和內存泄漏的定義、區別以及解決方案。 一、內存溢出的定義

2023-12-19 14:10:12 883

883 我們需要 XILINX FPGA 給 AD9240 提供 8MHz CLK,AD9240 給 FPGA 提供采樣數據和溢出標志,但 FPGA 提供的 CLK 最高 3.3V,請問如何輸入給 AD9240 呢?

2023-12-08 06:54:46

PCB的DDR4布線指南和PCB的架構改進

2023-12-07 15:15:58 755

755 追風A60采用新一代DDR5內存規格,相較DDR4,性能提升接近1倍。高配6000MHz頻率實現DDR4 3200MHz的1.6倍傳輸速度和1.9倍傳輸帶寬,讓用戶在使用臺電內存條時獲得更快速、更流暢的電腦體驗。

2023-12-05 15:52:49 411

411

為滿足對高效內存性能日益增長的需求,DDR5相比其前身DDR4實現了性能的大幅提升,具體為傳輸速度更快、能耗更低、穩定性提高、內存密度更大和存取效率提高等。

2023-12-05 10:50:40 214

214

電子發燒友網站提供《集成電源解決方案-Altera FPGA應用介紹.pdf》資料免費下載

2023-11-28 09:21:50 0

0 電子發燒友網站提供《FPGA的電源管理解決方案.pdf》資料免費下載

2023-11-24 14:42:33 0

0 對于ddr5市場的發展,威剛表示,現階段觀察到需求端春燕來臨,主要來自pc,隨著顧客需求的明顯好轉和pc內存內容的提高,明年上半年ddr5將超過ddr4,形成黃金交叉。目前在現貨市場上,ddr5的單價比ddr4高4-50%,從威強的情況來看,ddr5比重的上升有助于總利潤率。

2023-11-24 10:38:38 217

217 電子發燒友網站提供《實用RTD接口解決方案.pdf》資料免費下載

2023-11-16 16:05:29 0

0 Xilinx Block Memory Generator(BMG)是一個先進的內存構造器,它使用Xilinx fpga中的嵌入式塊RAM資源生成面積和 性能優化的內存。

2023-11-14 17:49:43 736

736

羅徹斯特電子攜手AMD/Xilinx,為Xilinx傳統FPGA和相關配置PROM產品提供供貨支持。

2023-11-07 09:04:42 250

250 DDR4和DDR3內存都有哪些區別? 隨著計算機的日益發展,內存也越來越重要。DDR3和DDR4是兩種用于計算機內存的標準。隨著DDR4內存的逐漸普及,更多的人開始對兩者有了更多的關注。 DDR

2023-10-30 09:22:00 3886

3886 在集中削減DDR4產量的同時,主要DRAM芯片制造商正在迅速轉向利潤更高的DDR5生產。預計到2023年底,他們的DDR5內存bit銷售額合計將占bit銷售額總額的30-40%。

2023-10-29 15:59:48 603

603

飛騰派是由飛騰攜手中電港螢火工場研發的一款面向行業工程師、學生和愛好者的開源硬件,采用飛騰嵌入式四核處理器,兼容ARM V8架構,板載64位 DDR4內存,分為2G和4G兩個版本。主板板載WiFi

2023-10-25 11:44:22

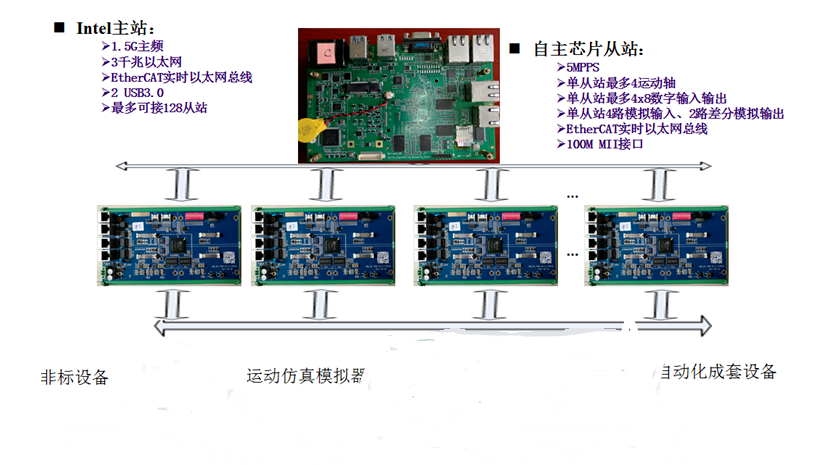

本應用筆記專為使用AT32F437微控制器的開發人員編寫。它提供了如何使用AT32F437以太網通信接口實現在應用中編程(IAP)的解決方案。有兩種基于LwIP TCP/IP協議棧的解決方案:? 使用TFTP(簡單文件傳輸協議)的IAP? 使用HTTP(超文本傳輸協議)的IAP

2023-10-25 07:41:41

的24個GTY,LVDS信號,DSP的1路以太網

三、軟件系統

?提供FPGA的接口測試程序,包括 DDR4、光纖、RapidIO、FMC等接口

?提供DSP接口測試程序,包括DDR3、Flash

2023-10-16 11:12:06

遇到一個比較有意思的問題。一個朋友問我說:他的電腦內存壞了,想換一條新的內存,換DDR5內存條是不是更好?看了他的配置之后,電腦使用的是DDR4的條子。顯然這是不能換的。

2023-10-10 11:18:13 606

606

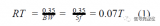

做高速鏈路的小伙伴都知道,Stub總是會帶來各種影響,或者導致阻抗突變,或者導致插入損耗曲線上存在諧振,等等。本文介紹了Via stub在DDR4并行鏈路上的表現。下面是論文的全文。

2023-10-09 10:35:30 321

321

摘要:本文將對DDR3和DDR4兩種內存技術進行詳細的比較,分析它們的技術特性、性能差異以及適用場景。通過對比這兩種內存技術,為讀者在購買和使用內存產品時提供參考依據。

2023-09-27 17:42:10 1088

1088 DDR4 3200和3600是內存模塊的頻率標準,表示其頻率值,具有以下差異

2023-09-26 15:24:18 8981

8981 以下主題概述了Altera的外部內存接口解決方案。

Altera提供最快、最高效、延遲最低的內存接口IP核。Altera的外部存儲器接口IP設計用于方便地與當今更高速的存儲器設備接口。

Altera

2023-09-26 07:38:12

相對于DDR3, DDR4首先在外表上就有一些變化,比如DDR4將內存下部設計為中間稍微突出,邊緣變矮的形狀,在中央的高點和兩端的低點以平滑曲線過渡,這樣的設計可以保證金手指和內存插槽有足夠的接觸面

2023-09-19 14:49:44 1484

1484

DDR4 內存。

3. Kria SOM還支持PYNQ,為嵌入式平臺帶來了Python生產力-MICRO-PYTHON

4. __除了支持PetaLinux和Yocto之外,Kria KV260

2023-09-18 14:56:59

三星公司計劃在下半年再次削減DRAM制程的產能,而今年以來這一減產主要針對DDR4。業界普遍預期,三星的目標是在今年年底之前將庫存水平降至合理水平。這一減產舉措可能會導致DDR4市場價格上漲,而目前

2023-09-15 17:42:08 996

996 隨著英特爾和amd將新的pc/筆記本電腦和服務器平臺更換為ddr4, ddr4的需求開始減少。因此,三星大幅減少ddr4的生產,轉向ddr5,試圖鞏固業界第一的位置。

2023-09-15 11:40:33 555

555 在全默認設置的情況下,影馳HOF OC Lab幻跡S DDR5 8000內存的工作速率為DDR5 4800,延遲設定為40-40-40-76,因此在這個設置下它的內存性能并不突出,與普通的DDR5 4800內存相當。

2023-09-15 10:40:42 750

750

本文主要介紹Xilinx FPGA的GTx的參考時鐘。下面就從參考時鐘的模式、參考時鐘的選擇等方面進行介紹。

2023-09-15 09:14:26 1952

1952

電子發燒友網站提供《Xilinx器件設計散熱器和散熱解決方案.pdf》資料免費下載

2023-09-14 10:59:41 3

3 電子發燒友網站提供《面向Xilinx FPGA和SoC的超快設計方法指南.pdf》資料免費下載

2023-09-14 10:02:31 1

1 電子發燒友網站提供《Teledyne e2v的宇航級DDR4的硬件設計指南.pdf》資料免費下載

2023-09-13 17:14:55 1

1 電子發燒友網站提供《使用FPGA的下一代生物識別匹配引擎解決方案.pdf》資料免費下載

2023-09-13 11:10:15 0

0 電子發燒友網站提供《Rapanda流加速器-實時流式FPGA加速器解決方案.pdf》資料免費下載

2023-09-13 10:17:12 0

0 電子發燒友網站提供《基于PDN共振峰的最壞情況數據模式分析電源完整性對FPGA DDR4存儲器接口中的信號完整性的影響.pdf》資料免費下載

2023-09-13 09:56:49 0

0 意法半導體的ST4SIM SIM和eSIM產品組基于基本型、加密型和GSMA SGP.02配置。我們的解決方案允許設備隨時隨地聯網,同時確保資產安全。得益于合作伙伴提供的連接解決方案,全球覆蓋和互

2023-09-08 06:14:44

瀾起科技還介紹說,根據存儲接口芯片的價格規律,一般來說,新一代產品由于技術和性能升級,其起銷價格會比上一代有所提高,上一代產品的售價會逐漸降低。為了保持存儲接口芯片產品的平均售價,使用了持續的重復世代。與ddr4代相比,ddr5內存接口芯片的初期銷售價格大幅上漲。

2023-09-07 14:43:34 705

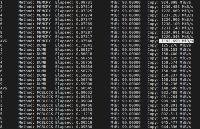

705 科技QA200A2 開發套件 的pcie插槽設計為PCIEx2,Xilinx -FPGA 開發板VC709 PCIE測試數據如下:

圖3-1全愛科技開發套件PCIE讀寫測試截圖

4 評估套件接口圖示

2023-09-05 14:39:57

本文介紹一個FPGA開源項目:DDR3讀寫。該工程基于MIG控制器IP核對FPGA DDR3實現讀寫操作。

2023-09-01 16:23:19 743

743

本文開源一個FPGA項目:基于AXI總線的DDR3讀寫。之前的一篇文章介紹了DDR3簡單用戶接口的讀寫方式:《DDR3讀寫測試》,如果在某些項目中,我們需要把DDR掛載到AXI總線上,那就要通過MIG IP核提供的AXI接口來讀寫DDR。

2023-09-01 16:20:37 1888

1888

本文介紹一個FPGA 開源項目:PCIE I/O控制卡。上一篇文章《FPGA優質開源項目– PCIE通信》開源了基于FPGA的PCIE通信Vivado工程,用于實現上位機通過PCIE接口訪問FPGA的DDR3以及RAM內存數據。PCIE I/O控制卡工程是在上一個工程的基礎上進行了部分模塊和參數的修改。

2023-09-01 16:18:36 1295

1295

,以滿足各種設計需求,并提供時鐘驅動邏輯資源的靈活性和可擴展性。那今天我們一起解剖Xilinx 7系列FPGA的時鐘結構,看看它到底如何實現如此豐富的時鐘資源并能夠做到完美平衡。

2023-08-31 10:44:31 1032

1032

/ O 端口和DDR4 內存,適用于

各種不同的可編程應用,帶有ZU27DR FPGA 的ZXB-RFSOC-2T2R 由 4 路12 位,采樣率

4.0GSPS ADC 和 4 路14 位,采樣率

2023-08-25 15:11:55

DDR4 3200和DDR4 3600是兩種常見的內存頻率規格,它們在性能上會有一定的差別,但差別大小取決于具體的應用場景和系統配置。

2023-08-22 14:45:05 28274

28274 PH1A100是否支持DDR3,DDR4

2023-08-11 06:47:32

,不知道出現啥問題?求助解決方案,同時有個疑問DDR4是否可以使用,論壇中都是使用DDR3的教程。

log如下

2023-08-11 06:17:58

DDR5的主板不支持使用DDR4內存。DDR5(第五代雙倍數據率)和DDR4(第四代雙倍數據率)是兩種不同規格的內存技術,它們在電氣特性和引腳布局上存在明顯差異。因此,DDR5內存模塊無法插入DDR4主板插槽中,也不兼容DDR4內存控制器。

2023-08-09 15:36:25 12804

12804 xilinx平臺DDR3設計教程之設計篇_中文版教程3

2023-08-05 18:39:58

以下內存設備:

?雙倍數據速率3(DDR3)SDRAM。

?低壓DDR3 SDRAM。

?雙倍數據速率4(DDR4)SDRAM。

2023-08-02 11:55:49

DDR是運行內存芯片,其運行頻率主要有100MHz、133MHz、166MHz三種,由于DDR內存具有雙倍速率傳輸數據的特性,因此在DDR內存的標識上采用了工作頻率×2的方法。 ? DDR芯片

2023-07-28 13:12:06 1883

1883

電子發燒友網站提供《PI2DDR3212和PI3DDR4212在DDR3/DDR4中應用.pdf》資料免費下載

2023-07-24 09:50:47 0

0 DDR是Double Data Rate的縮寫,即“雙倍速率同步動態隨機存儲器”。DDR是一種技術,中國大陸工程師習慣用DDR稱呼用了DDR技術的SDRAM,而在中國臺灣以及歐美,工程師習慣用DRAM來稱呼。

2023-07-16 15:27:10 3365

3365

對于DDR的理解,最初簡單的以為無非一個大的數組,我會接口使用就OK了。

2023-06-28 15:36:06 406

406

鎖相環基本上是每一個fpga工程必不可少的模塊,之前文檔xilinx 7 系列FPGA時鐘資源對xilinx fpga的底層時鐘資源做過說明,但是對于fpga的應用來說,使用Clocking Wizard IP時十分方便的。

2023-06-12 17:42:03 2883

2883

和筆記本。內存模組的類型決定了所需的內存接口芯片和內存模組配套芯片。 ? ? ? 內存進入 DDR5 新世代,標準升級拉動相關芯片需求。與 DDR4 相比, DDR5 的優勢可簡單地概括為: ( 1)速度

2023-05-29 14:07:38 1359

1359

Xilinx FPGA pcb設計

2023-05-29 09:11:36 0

0 我有一塊自制的imx8mp主板,使用DDR4的型號是:K4ABG165WA-MCWE,單片容量32Gb,主頻3200Mhz,我的主板使用了兩顆芯片,但是使用MX8M_Plus_DDR4_RPA_v9.xlsx無法完成配置

2023-05-17 06:12:25

Xilinx 7系列FPGA IO Bank分為HP Bank和HR Bank,HP IO接口電壓范圍為1.2V~1.8V,可以實現高性能,HR IO接口電壓范圍為1.2V~3.3V。

2023-05-15 09:27:58 2114

2114

FPGA 為系統設計提供了極其靈活的可編程平臺。包含 IP 內核、硬件平臺、演示設計、驅動程序和軟件的綜合解決方案包使設計人員能夠縮短開發周期,同時降低設計的復雜性。

2023-05-08 11:35:11 246

246

DDR4內存模塊支持單個64位通道(如果考慮ECC,則為72位通道)。相比之下,DDR5內存模塊配備了兩個獨立的32位通道(40位ECC)。

2023-05-08 10:27:44 1331

1331 PLC的主機部分由中央處理器、輸入/輸出接口(I/0接口)通信、擴展接口、儲存器、設備接口和電源等部分構成。其中,基于京微齊力FPGA HME-M7和舜銘存儲鐵電存儲器PB85RS2MC的PLC系統已成為最佳解決方案。

2023-05-06 14:32:44 893

893

我們有一個帶有連接到 LS1046A 的 DDR4 內存 (DDR4T04G72) 的定制板,目前正在為 DDR 控制器進行配置。目前我們對為什么我們甚至沒有啟動和運行 DDR 時鐘 (MCK0

2023-05-06 08:20:49

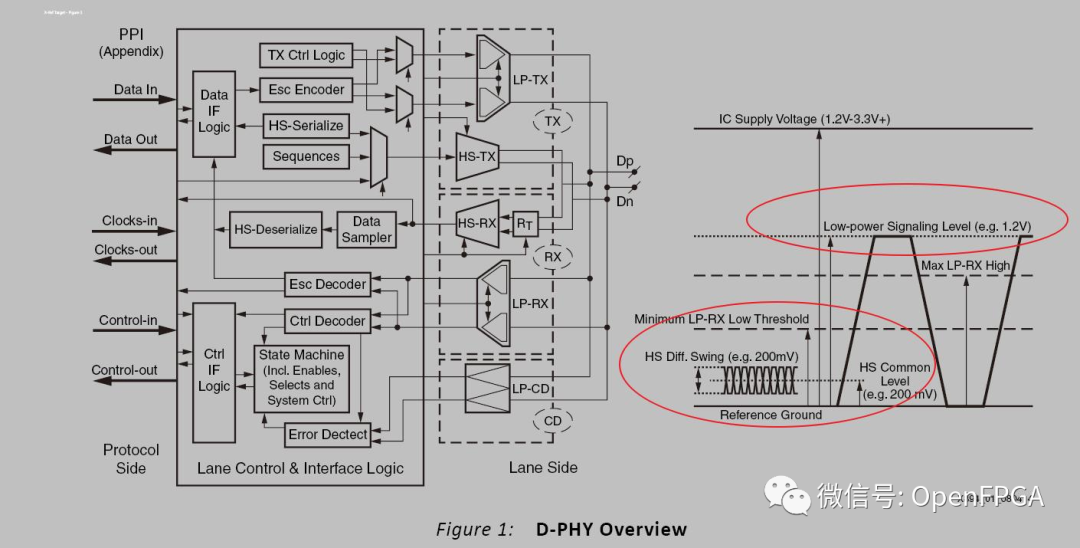

MIPI 接口現在非常流行,國產FPGA目前基本都帶MIPI接口,而AMD-Xilinx是從U+系列開始支持MIPI電平,從國內使用情況來看,7系列FPGA是使用最廣的器件,所以這次使用的FPGA是7系列FPGA使用電阻網絡實現MIPI電平的例子。

2023-04-24 09:30:06 3710

3710

我有 LS1046AFRWY 板的克隆。高速公路板使用 MT40A512M16JY-083E:B(商業級DDR4)。我的克隆使用 MT40A512M16JY-083E IT:B(工業級 DDR4

2023-04-24 08:08:20

將 DDR4 內存添加到 imx8mp

2023-04-20 10:59:17

NXP IMX8M Mini DDR4 校準

2023-04-20 07:36:55

講一講Xilinx家的MIPI方案。 這里以普通7系列作為討論的對象, X家高端的KU+/MPSOC+有已經可以直接支持MIPI接口的IO了。

2023-04-19 14:04:08 2965

2965

........................... 62.3 DDR4 接口原理圖.................72.4 兼容的 JEDEC DDR4 器件

2023-04-14 17:03:27

了每種 PMIC 解決方案的優勢,并包括用于比較選項的選擇指南。提供了示例電源圖,以協助執行設計過程。內容1 引言............................22 LP8733xx

2023-04-14 16:40:42

。 二、主要規格●板載主處理器XCKU060-2FFVA1156I;●兩組 64Bit DDR4 SDRAM,每組容量 2GB;●FPGA采用BPI 加載模式●FMC 接口提供20對GTH和LA信號

2023-04-13 15:56:21

組DDR4 SDRAM緩存單元,每組最大支持4GB容量,72bit(包含ECC,8bit),可實現進行復雜邏輯與算法時的數據緩存。PCIe總線最大支持Gen3、x8,具備超強的數據吞吐能力;前面板預留

2023-04-08 10:38:05

你能告訴我在哪里可以獲得 i.MX8M Plus 的詳細 DDR4 布局跟蹤路由指南嗎?我在 i.MX8M Plus 硬件開發人員指南中找不到它。順便問一下,NXP 有帶 DDR4 的 i.MX8M Plus 評估板嗎?

2023-03-31 07:52:02

武漢萬象奧科HD-G2UL-CORE核心板支持512MB/1GB DDR4配置,本文檔主要評估測試核心板內存512MB(DDR4)性能(讀寫速率)。

2023-03-28 18:14:58 414

414

電子發燒友App

電子發燒友App

評論