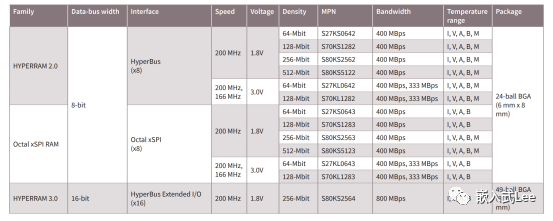

1、平臺(tái)芯片STM32H7A3,外掛2片Octo-SPI SRAM作為數(shù)據(jù)緩存,操作系統(tǒng)threadx文件系統(tǒng)filex。

2、數(shù)據(jù)在ram中讀寫都沒問題,緩存80kB以內(nèi)的數(shù)據(jù)寫入sd卡文件中也

2024-03-08 07:16:33

我將一個(gè)數(shù)組定義在SRAM2中,另一個(gè)數(shù)組定義在CCM中,我可以利用memcpy這個(gè)函數(shù)來將SRAM2里的數(shù)據(jù)拷貝到CCM中嗎。

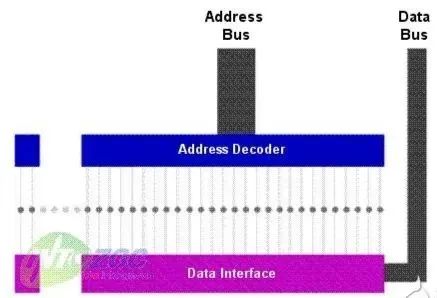

因?yàn)槲铱纯偩€矩陣圖,CCM的D-BUS和SRAM2并無交集,是不是也就意味著這兩塊內(nèi)存互相無法進(jìn)行交互呢?

2024-03-06 08:21:14

我在使用 UART FIFO 緩沖區(qū)時(shí)遇到了以下問題。

問題描述:

當(dāng)通過兩個(gè) UART 通道使用完整的 UART FIFO 緩沖區(qū)并通過兩個(gè)通道進(jìn)行通信時(shí),緩沖區(qū)中的數(shù)據(jù)有時(shí)會(huì)損壞,例如,UART

2024-03-06 06:59:31

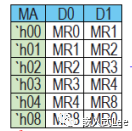

FX3自帶SDK中的例程GPIF ii sram-master:讀寫sram指令中的地址由狀態(tài)機(jī)中的地址計(jì)數(shù)器來決定,請(qǐng)教一下如何在FX3固件代碼中指定讀寫sram的地址,可否提供一個(gè)例程或相關(guān)文檔

2024-02-27 07:20:24

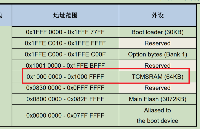

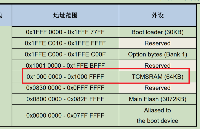

一般使用的均為通用SRAM空間,這部分SRAM使用的時(shí)候沒有限制,作為堆棧、變量、DMA使用等都可以,但TCMSRAM一般不使用,有的時(shí)候可能會(huì)被大家遺忘,如果大家

2024-02-24 09:43:16 186

186

PSOC6如何把變量定義在外部串行SPI SRAM中,并且在使用時(shí)可以跟內(nèi)部SRAM變量使用方法類似

2024-02-01 06:33:40

我們將 XMC4500 用于功能安全應(yīng)用。 有幾個(gè)用戶安裝了 1000 個(gè)或更多控制器。

在這些現(xiàn)場(chǎng)安裝中,我們每月在 PSRAM 和/或 DSRAM 中會(huì)遇到大約 1-2 個(gè)奇偶校驗(yàn)錯(cuò)誤。 錯(cuò)誤

2024-01-26 06:30:34

我把這個(gè)函數(shù)放進(jìn)了 PSRAM 地址,我檢查了地圖,它起作用了。

但是十六進(jìn)制文件不包括 PSRAM地址。

我怎樣才能配置 lsl 或工具來獲取 HEX 文件中的 PSRAM 地址?

2024-01-22 06:05:00

可以使用 DMA 進(jìn)行自動(dòng)緩沖區(qū)管理,從而啟用直通模式。 有人估計(jì)過使用BULK端點(diǎn)可以給我的最大數(shù)據(jù)速率嗎? 我不能使用等時(shí)端點(diǎn),因?yàn)橐呀?jīng)定義了 OpenJTAG 接口。

有人有通過 psoc5LP

2024-01-19 08:19:10

您能告訴我 PSoC? 4中SRAM陣列的數(shù)據(jù)保持電壓?jiǎn)幔?我想知道在 VDD 電源電壓下降或上升時(shí) SRAM 可以保留數(shù)據(jù)的最小電壓。

MPN: PSoC? 4100S Max/CY8C4148AZI-S555

2024-01-19 06:08:12

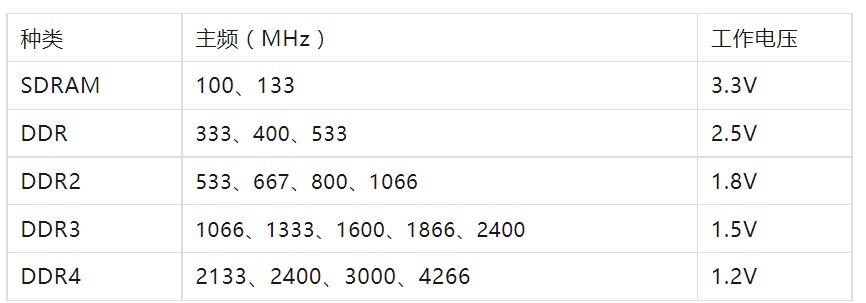

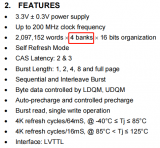

。 SDRAM是一種集成電路存儲(chǔ)器,可以通過同步鐘信號(hào)進(jìn)行數(shù)據(jù)讀寫。與傳統(tǒng)的靜態(tài)隨機(jī)存儲(chǔ)器(SRAM)相比,SDRAM具有更高的存儲(chǔ)密度和更低的成本。擴(kuò)展SDRAM接口使得微控制器能夠使用外部

2024-01-04 14:09:23 339

339 已用這種模式成功驅(qū)動(dòng)了一些psram,但是SRAM始終驅(qū)動(dòng)不了。

SRAM驅(qū)動(dòng)架構(gòu)

XMC復(fù)用模式讀時(shí)序,其中一個(gè)HCLK=4.16ns(240Mhz)

SRAM讀時(shí)序參數(shù)

SRAM讀時(shí)序圖

XMC

2024-01-04 10:46:19

JESD79-5B DDR5 SDRAM-2022 JEDEC

2023-12-25 09:51:55 2

2 xRMS最大值為 52,702,092)。

但波形緩沖器(Waveform buffer)以 固定數(shù)據(jù)速率波形(SINC4或LPF) 讀取的數(shù)據(jù)是24位ADC數(shù)據(jù),但我按照24位最大值0xFFFFFF

2023-12-25 07:21:24

請(qǐng)教一下DAC的問題。MCU向DAC的DIN引腳輸入數(shù)據(jù)后,DAC轉(zhuǎn)換到我們所希望的電壓值,DAC中鎖存器的作用是不是說當(dāng)完成一次DAC轉(zhuǎn)換后,如果不再向DIN引腳中輸入數(shù)據(jù),那么DAC的電壓輸出會(huì)

2023-12-19 08:13:51

,從基本原理到電路設(shè)計(jì)的細(xì)節(jié)。

SRAM是一種基于存儲(chǔ)雙穩(wěn)態(tài)的存儲(chǔ)器技術(shù),它使用觸發(fā)器來存儲(chǔ)

數(shù)據(jù)。一個(gè)典型的

SRAM單元由6個(gè)傳輸門(傳遞門)組成,其中包括兩個(gè)傳輸門用于存儲(chǔ)和讀取

數(shù)據(jù),以及兩個(gè)傳輸門用于寫入和刷新

數(shù)據(jù)。

SRAM的讀取操作是通過將地址輸入到

SRAM中來完成的。當(dāng)?shù)刂份斎氲?/div>

2023-12-18 11:22:39 496

496 1:請(qǐng)問下BF592 用于做音頻處理RAM不夠用可以外掛SDRAM或者SRAM嗎?如果可以有沒有相關(guān)的原理圖和軟件下載?

2:592是定點(diǎn)DSP,那對(duì)音頻采樣數(shù)據(jù)存儲(chǔ)時(shí)要定義成float類型好呢

2023-11-30 07:20:36

電子發(fā)燒友網(wǎng)站提供《參數(shù)在數(shù)據(jù)轉(zhuǎn)換器中的應(yīng)用.pdf》資料免費(fèi)下載

2023-11-27 11:46:03 0

0 中心的基建和運(yùn)維中具有無可替代的重要意義。 首先,預(yù)端接光纜系統(tǒng)能夠大大提高工程的安裝效率。在數(shù)據(jù)中心中,需要大量的光纖跳線來實(shí)現(xiàn)設(shè)備的連接,而預(yù)端接光纜系統(tǒng)可以提前將光纖跳線做好,到現(xiàn)場(chǎng)直接安裝,無需現(xiàn)場(chǎng)

2023-11-10 09:47:31 160

160 單片機(jī)可以替代PLC嗎?

2023-11-01 06:54:57

串口接收的數(shù)據(jù) 存在數(shù)組里 采取覆蓋的方式 第二次接收的時(shí)候要是還沒接收完就處理主函數(shù)的東西 不是會(huì)產(chǎn)生錯(cuò)誤 這種情況應(yīng)該怎么辦呢

2023-10-27 07:53:23

AT32F系列 I2S DMA雙緩沖替代實(shí)現(xiàn)方法演示AT32F系列I2S使用DMA半傳輸及傳輸完成中斷來達(dá)到DMA雙緩沖存儲(chǔ)接收數(shù)據(jù)的方法。

2023-10-27 06:21:27

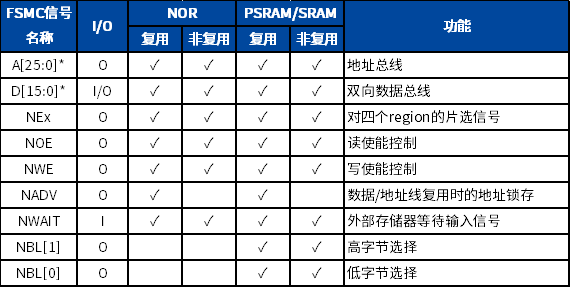

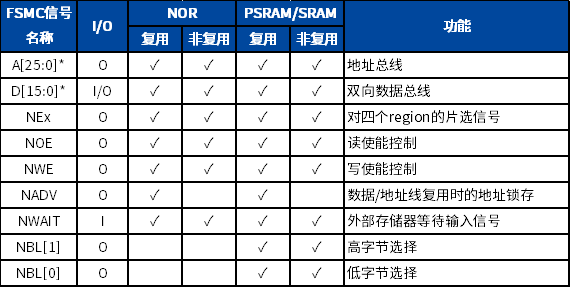

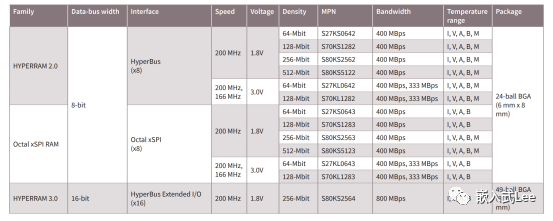

PSRAM/SRAM與XMC硬件連接的推薦方法描述了在AT32系列100引腳封裝芯片上以XMC連接PSRAM的硬件推薦方法,達(dá)到器件容易取得及價(jià)格合理的目標(biāo)。

2023-10-24 06:17:32

電感的兼容替代在近幾年的確是一個(gè)討論度比較高的問題,關(guān)于不同品牌電感替代的案例谷景也分享了很多。本篇我們我們探討另外一個(gè)關(guān)于電感替代的問題——同樣0805貼片電感封裝尺寸的是否可以直接替代

2023-10-23 14:40:47 314

314 AT32 部分型號(hào)有零等待閃存和非零等待閃存,程序在零等待閃存執(zhí)行速度比在非零等待閃存執(zhí)行速度快,如果有函數(shù)對(duì)執(zhí)行速度有要求,可以將該函數(shù)加載到零等待區(qū)執(zhí)行。當(dāng)零等待閃存使用完后,如果還有函數(shù)對(duì)執(zhí)行速度有要求,可以將該函數(shù)加載到 SRAM 執(zhí)行,前提是SRAM 還有足夠的空間存放該函數(shù)代碼。

2023-10-20 06:10:59

掉電后還能讀取到SRAM的數(shù)據(jù)嗎

2023-10-15 09:24:03

STM8可以實(shí)現(xiàn)從SRAM啟動(dòng)程序嗎

2023-10-09 07:38:29

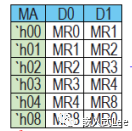

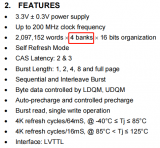

SDRAM的內(nèi)部是一個(gè)存儲(chǔ)陣列,將數(shù)據(jù)“填”進(jìn)去,你可以它想象成一張表格。和表格的檢索原理一樣,先指定一個(gè)行(Row),再指定一個(gè)列(Column),我們就可以準(zhǔn)確地找到所需要的單元格,這就是內(nèi)存芯片尋址的基本原理。

2023-09-28 17:26:29 637

637

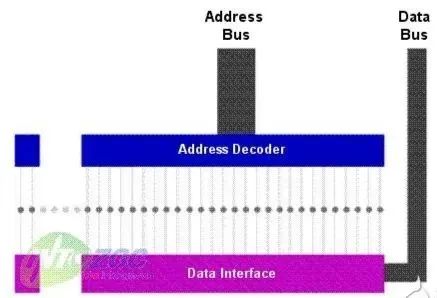

FSMC外擴(kuò)SRAM數(shù)據(jù)之間是怎么傳送的?先保存在FSMC再傳送外擴(kuò)SRAM

2023-09-27 06:03:22

使用MM32F3270 FSMC驅(qū)動(dòng)SRAM

2023-09-18 16:29:50 918

918

內(nèi)部閃存高達(dá)2MB

?高達(dá)512KB的內(nèi)部SRAM

?用于幀緩沖的外部存儲(chǔ)器

?16位或32位SDRAM/SRAM

?封裝:LQFP 144引腳,最高可達(dá)208。

2023-09-11 08:09:15

頻率可達(dá)216MHz/2(fCLK = HCLK /2)? 支持的存儲(chǔ)器類型? 靜態(tài)存儲(chǔ)支持? SRAM? PSRAM? NOR/ONENAND? ROM? LCD接口? 支持8080和6800模式

2023-09-11 06:58:26

應(yīng)用程序: 此示例代碼使用 M032 在 SRAM 中運(yùn)行 ISR 。

BSP 版本: M031_Series_BSP_CMSIS_V3.03.000

硬件: NuMaker-M032SE

2023-08-31 09:21:19

應(yīng)用程序:本示例代碼演示如何使用Nanopb在M252中執(zhí)行協(xié)議緩沖。 Nanopb是ANSI-C執(zhí)行Google協(xié)議緩沖數(shù)據(jù)格式。

BSP 版本:M251/M252/M254/M254/M256

2023-08-29 06:07:42

QSPI0可以映射到512Mb(0x2000_0000開始)地址空間直接訪問,其他QSPI是怎樣映射的?不是很清楚8M的psram對(duì)應(yīng)的地址空間是什么

2023-08-16 06:43:18

SDRAM全稱Synchronous Dynamic RAM,同步動(dòng)態(tài)隨機(jī)存儲(chǔ)器。首先,它是RAM,即隨機(jī)存儲(chǔ)器的一種。

2023-08-08 15:10:46 896

896

電子發(fā)燒友網(wǎng)站提供《STM32U5 HexaSPI總線到PSRAM的PCB布線規(guī)則.pdf》資料免費(fèi)下載

2023-08-01 09:06:33 0

0 IP_數(shù)據(jù)表(M-1):SRAM and TCAM

2023-07-06 20:12:09 0

0 我咨詢下 用N3290X 只在外圍掛一顆SPI flash (比如16M)可以將畫面 在下載時(shí) 直接下載到SPI flash 中(比如通過串口)還是需要先通過下載器將畫面下載到SPI flash 中?在運(yùn)行時(shí) 可否直接將SPI flash 中畫面數(shù)據(jù)拷貝到內(nèi)部sdram中 ?

2023-06-27 06:30:13

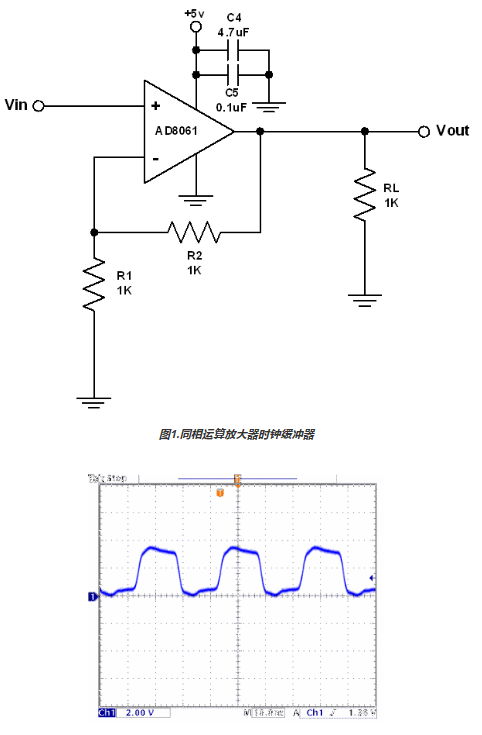

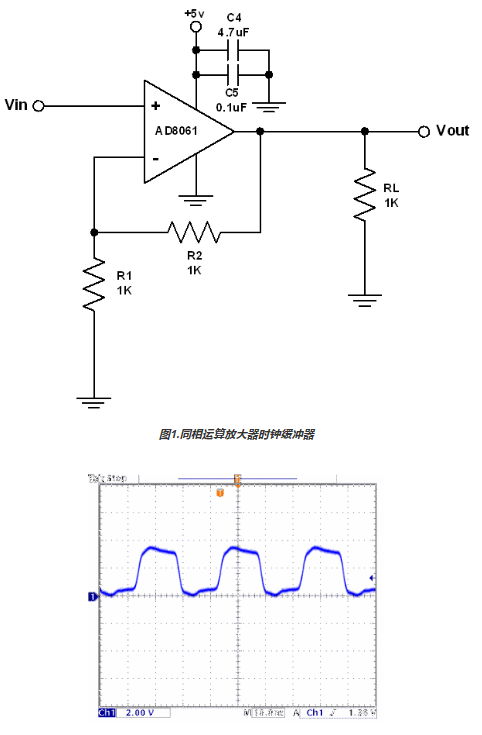

在消費(fèi)電子應(yīng)用中,與典型的時(shí)鐘緩沖應(yīng)用相比,其頻率往往較低,要求也更低,廉價(jià)的高速運(yùn)算放大器(~100 MHz帶寬)可以為傳統(tǒng)時(shí)鐘緩沖器提供有吸引力的替代方案。高速放大器可能比傳統(tǒng)時(shí)鐘緩沖器便宜,但它們可以適應(yīng)各種設(shè)計(jì)配置。

2023-06-17 17:29:14 704

704

我們正在破壞 RT1170 evkit 上的一些性能測(cè)試,我們正在使用 dev_msc_ramdisk_bm_cm7 示例。由于存儲(chǔ)緩沖區(qū)受內(nèi)部 DTCM 大小的限制,我們希望將其移動(dòng)到外部 SDRAM 上。我們找不到一種簡(jiǎn)單的方法來做到這一點(diǎn)。任何人都可以幫助我們嗎?

2023-06-12 07:51:04

PSRAM的時(shí)序比較簡(jiǎn)單,主要根據(jù)各個(gè)時(shí)序圖理解每個(gè)時(shí)序階段,及其參數(shù)。重點(diǎn)要理解DQS/DM是誰驅(qū)動(dòng)的,代表什么意思, 數(shù)據(jù)采樣的時(shí)間即DQS上升沿延遲數(shù)據(jù)建立時(shí)間之后采樣。

2023-06-08 11:30:55 19837

19837

以上分享了PSRAM接口一些關(guān)鍵的知識(shí)點(diǎn),大部分是容易理解錯(cuò)誤,且導(dǎo)致問題的點(diǎn),基本上理解這些點(diǎn)就能解決大部分問題了,作為入門參考也可以先看這篇,先有個(gè)大概了解。作為遇到問題不知如何解決時(shí)也可以參考這篇文章,基本上能解決大部分問題。

2023-06-08 11:25:04 3795

3795

我正在嘗試使用 RT1176 為我的 SDRAM 組配置 SEMC 的參數(shù)。

在各種參數(shù)中,EVB 設(shè)置值

“ sdramconfig.tPrescalePeriod_Ns ”為“160

2023-06-05 10:31:50

************************************************* *************************************

* 詳細(xì)說明:

* 這個(gè)例子的目的是展示如何保存數(shù)據(jù)在 SRAM 存儲(chǔ)器中通過

2023-06-05 09:47:48

我正在嘗試使用 MCUXpresso 配置工具版本 13.1 為 SRAM 配置 RT1172 SEMC。

我只將 SDRAM 視為一個(gè)選項(xiàng):

在此處的類似帖子中有回復(fù) (2022-08-30),這將在下一版本中通過“模式”設(shè)置提供:

是否有關(guān)于此功能可用性的狀態(tài)更新?

2023-06-02 08:28:39

GRANDMICRO有容微在數(shù)據(jù)中心方案應(yīng)用

2023-05-30 14:11:05 414

414 我正在尋找有關(guān)如何配置 FlexIO 以模擬 RT1176 和 FPGA 之間的 SRAM 接口的示例。我有一個(gè) 16 位并行數(shù)據(jù)總線,用于讀取和寫入 FPGA 上的內(nèi)存映射寄存器。我有 CLK

2023-05-29 07:41:53

=debug_flash_sdram_xip,則每次燒寫到NOR FLASH 太慢,等待消耗太長(zhǎng)時(shí)間。

2)如果使用 -DCMAKE_BUILD_TYPE=debug,則鏡像寫到 ILM中,但又受限與 ILM的大小。

因此手?jǐn)]了一個(gè)

2023-05-26 07:39:23

現(xiàn)在,我正在使用帶有 SDRAM 的 imxrt1052。所有變量都在 SDRAM 中。但我想要 SRAM 中的一些變量,以及 SDRAM 中的其他變量。怎么做 ?

2023-05-12 08:23:11

到了FSMC的NE3端口,地址為19位,數(shù)據(jù)為16位,設(shè)置一下cubemx,時(shí)序配置為0;4;0

生成代碼,我這里是用的Makefile

把顯存放在SRAM中,代碼如下

static uint16_t

2023-05-08 20:01:14

.icf

2) flexspi_nor_sdram.icf

使用 sdram.icf,代碼可以正常工作,但它是從 RAM 內(nèi)存中執(zhí)行的,因此在按下復(fù)位后它無法保留代碼。而

2023-05-05 06:38:08

本公司目前MCU系列,到目前為止, SWM34x 支持外接8M16M SDRAM,SWD34S系列已經(jīng)把SDRAM合封入芯片,合封的SDRAM大小根據(jù)芯片型號(hào)不同,具體見官方手冊(cè)。

2023-04-28 09:30:22 1496

1496

使用 MIMXRT1024CAG4B 并計(jì)劃在我們的設(shè)計(jì)中連接一個(gè) 8 位 SDRAM ( IS42S86400F-7TLI )。我可以從 A0 配置 8 位 SDRAM 的地址引腳嗎?或者在配置這些地址引腳時(shí)是否有任何特定的限制?

2023-04-28 08:58:11

如何使用 QDR(TM) II SRAM 和 DDR II SRAM 用戶手冊(cè)

2023-04-27 20:25:40 6

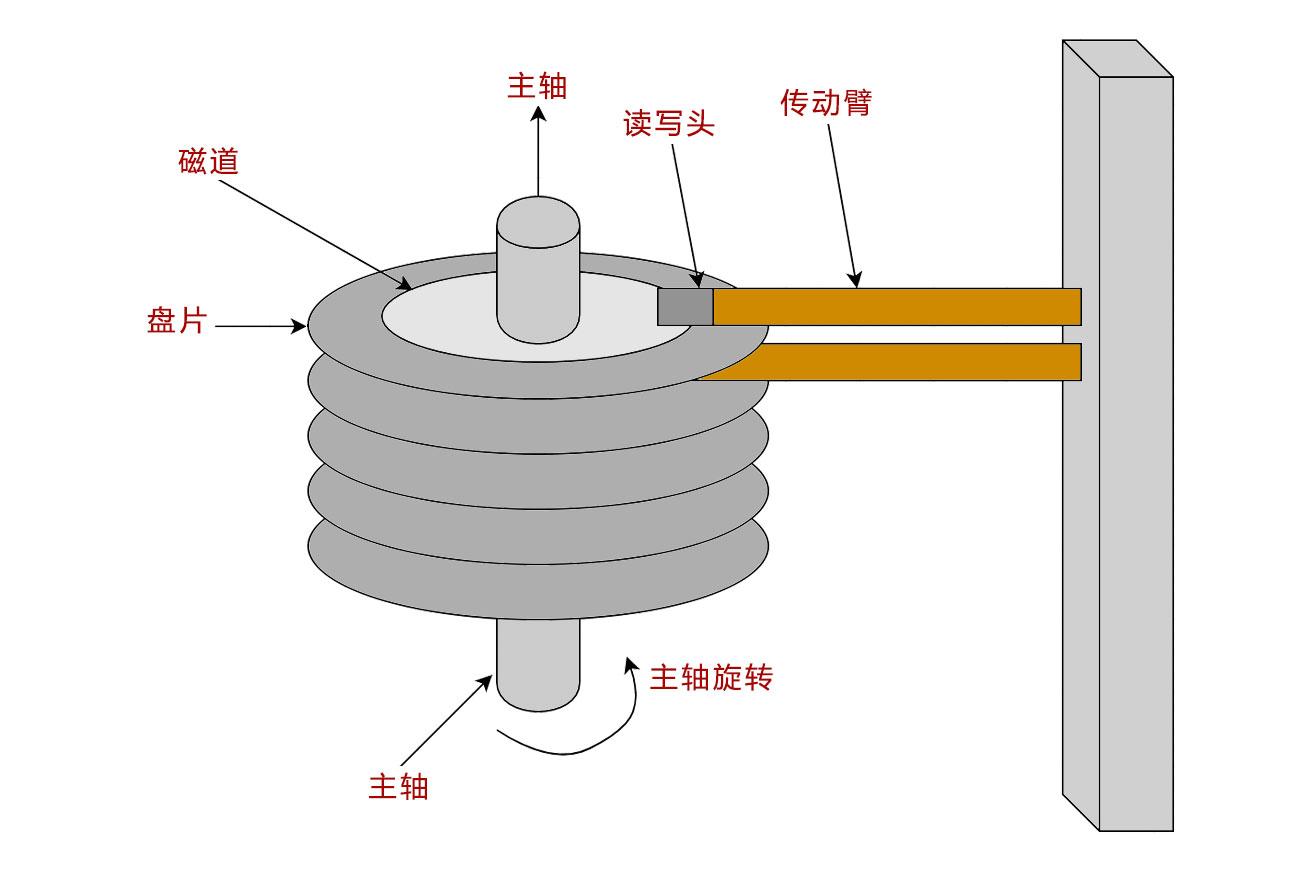

6 極高的運(yùn)動(dòng)定位精度和穩(wěn)定性,在數(shù)據(jù)存儲(chǔ)中具有著非常廣泛的應(yīng)用。在數(shù)據(jù)存儲(chǔ)的領(lǐng)域,通常需要壓電納米定位臺(tái)來實(shí)現(xiàn)納米甚至亞納米級(jí)別的運(yùn)動(dòng)控制精度。 壓電納米定位臺(tái)用于讀寫頭的高精度調(diào)節(jié) 壓電納米定位臺(tái)可以在光盤數(shù)據(jù)存儲(chǔ)

2023-04-26 16:23:02 431

431

我正在使用 S32k358 uC,我想禁用內(nèi)存區(qū)域的數(shù)據(jù)緩存。在框圖中,我看到樹形 SRAM 塊 SRAM0、SRAM1、SRAM2。是否可以禁用 SRAM2 的數(shù)據(jù)緩存并保留 SRAM 0 和 SRAM1 的數(shù)據(jù)緩存?

2023-04-23 08:01:09

。Bank1只能通過片選信號(hào)NE1以復(fù)用模式支持NOR/PSRAM 存儲(chǔ)器。Bank2只能通過片選信號(hào)NE2支持16位或8位NAND Flash。SPI2和SPI3接口可以在SPI模式和I2S音頻模式

2023-04-19 21:13:57

的 ITCM 和 DTCM)。我們的問題是:1- 沒有 SDRAM,我們是否可以增加 CM4 的代碼和數(shù)據(jù)空間?如果可以的話,CM7如何加載大于256KB的代碼到0x20200000呢?請(qǐng)指出

2023-04-19 07:17:13

SEMC接口支持4種設(shè)備,我想確認(rèn)以下問題:1、是否支持在同一個(gè)工程中通過SEMC接口訪問兩個(gè)不同的設(shè)備,比如外接SDRAM插件,外接SRAM,同一個(gè)工程中需要與兩個(gè)外設(shè)進(jìn)行數(shù)據(jù)交互。2、如果支持,兩個(gè)設(shè)備切換時(shí)延遲多少?

2023-04-17 08:23:31

SEMC接口支持4種設(shè)備,我想確認(rèn)以下問題:1、是否支持在同一個(gè)工程中通過SEMC接口訪問兩個(gè)不同的設(shè)備,比如外接SDRAM插件,外接SRAM,同一個(gè)工程中需要與兩個(gè)外設(shè)進(jìn)行數(shù)據(jù)交互。2、如果支持,兩個(gè)設(shè)備切換時(shí)延遲多少?

2023-04-17 06:51:39

我正在使用帶有為 MCUXpresso IDE 生成的 SDK 的 FRDM-K66F 板。我看到當(dāng)我生成 SDK 時(shí),CMSIS DSP 庫(kù)的包含版本是 V1.4.5 b。在 SDK 構(gòu)建過程中如何將其更新到最新版本或選擇替代版本?

2023-04-14 07:10:52

我有一些 AiThinker Esp32cam 在這里工作。如果將它們與開發(fā)板連接到arduino 控制臺(tái)中的 USB,則會(huì)出現(xiàn)此錯(cuò)誤:E (60) psram:PSRAM ID 讀取錯(cuò)誤

2023-04-12 06:33:56

在FPGA中,F(xiàn)IFO一般是使用RAM存儲(chǔ)器作為緩沖區(qū),可以分為同步FIFO或異步FIO,一般用于數(shù)據(jù)緩沖,或者不同時(shí)鐘域之間的數(shù)據(jù)傳遞。

2023-04-10 09:30:10 539

539 SRAM可以分為低速、中速、高速。===========================================================16位寬的SRAM//16BITSRAM指針

2023-04-06 15:13:03 554

554

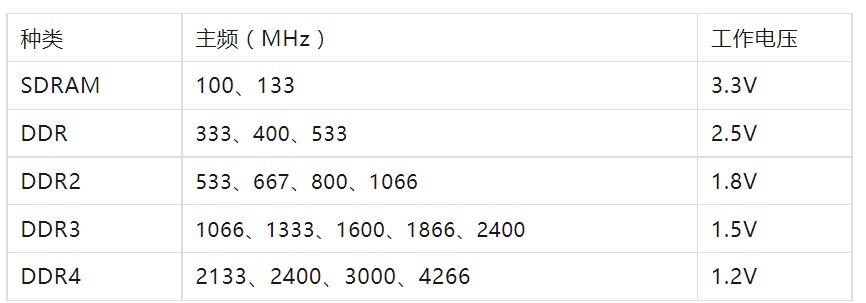

DDR內(nèi)存1代已經(jīng)淡出市場(chǎng),直接學(xué)習(xí)DDR3 SDRAM感覺有點(diǎn)跳躍;如下是DDR1、DDR2以及DDR3之間的對(duì)比。

2023-04-04 17:08:47 2867

2867

AVTP 時(shí)間同步/非時(shí)間同步控制格式。打包為 ACF CAN Brief /Full 消息)或打包成UDP 數(shù)據(jù)包. ? LLCE 打包消息并將其放在SRAM 的緩沖區(qū)中。數(shù)據(jù)包長(zhǎng)度由緩沖區(qū)大小的配置

2023-04-03 08:48:58

今天就帶你詳細(xì)了解一下到底什么是SRAM,在了解SRAM之前,有必要先說明一下RAM:RAM主要的作用就是存儲(chǔ)代碼和數(shù)據(jù)供CPU在需要的時(shí)候調(diào)用。

2023-03-30 14:11:51 587

587

SDRAM SLICE CARD

2023-03-30 12:05:53

RMII,這也可以讓我們更有效地進(jìn)行一些屏蔽/同步字檢測(cè)。我對(duì)物理層之上的以太網(wǎng)非常不熟悉,我不確定在場(chǎng)景 1 中我們是否可以充分禁用 MAC 的功能,使 FIFO 數(shù)據(jù)與傳輸?shù)?PHY 或從 PHY 接收

2023-03-30 08:36:13

我正在尋找一些與 IMXRT1064 的外部 SRAM 使用相關(guān)的信息。例如,EVK 有 256Mbit 166MHz SDRAM。166MHz與使用過的SDRAM有關(guān)。我試圖找到 SEMC 控制器

2023-03-30 07:11:18

嗨恩智浦專家,我知道 MIMXRT1xxx 能夠在 ITCM 中運(yùn)行 hello_world 但是 MIMXRT595 中沒有 ITCM 只有 SRAM。MIMXRT595-EVK是否可以在SRAM中運(yùn)行hello_world zephyr示例?

2023-03-30 06:38:30

ESP-12K-PSRAM-IPEX

2023-03-29 16:27:53

;=32,改變這個(gè)地址的數(shù)據(jù)也會(huì)改變這個(gè)地址的數(shù)據(jù)-32。這導(dǎo)致我寫的所有錯(cuò)誤數(shù)據(jù)。我檢查了我的 EMC 配置、數(shù)據(jù)寬度、時(shí)序,嘗試關(guān)閉緩沖區(qū),但沒有解決問題。我在想的是,如果我的EMC配置錯(cuò)誤,那么一開始直接

2023-03-28 08:13:08

我無法使用 SDRAM 啟動(dòng)代碼。我正在使用 lwip_dhcp_freertos_cm7 示例。以下是我的設(shè)置:?jiǎn)纹瑱C(jī)設(shè)置單片機(jī)設(shè)置預(yù)處理器設(shè)置:預(yù)處理器設(shè)置鏈接器設(shè)置鏈接器設(shè)置但是,代碼啟動(dòng)正常

2023-03-28 07:26:51

工程代碼可以登錄叁芯智能科技官方技術(shù)論壇下載。 在一些工程設(shè)計(jì)中,SDR SDRAM作為中間數(shù)據(jù)緩存器,往往需要接收上游傳輸過來的數(shù)據(jù),并且還要輸出下游所需的數(shù)據(jù)。為了能夠解決下上游傳輸數(shù)據(jù)的需要

2023-03-27 17:09:14

將 u-boot 代碼復(fù)制到 SRAM。但我知道我必須在鏈接器中啟用 __RAM_INIT 標(biāo)志才能初始化 ECC。如果不是,則在我將u-boot代碼復(fù)制到SRAM時(shí)出現(xiàn)異常。那是正常癥狀嗎?3) 啟動(dòng)時(shí)

2023-03-27 09:15:16

到此FIFO中,然后寫入到SDRAM中。輸出緩沖器為一個(gè)FIFO,SDRAM的數(shù)據(jù)輸入到此FIFO中,然后被VGA模塊讀出輸出給VGA接口。SDR SDRAM驅(qū)動(dòng)為控制接口模塊,完成對(duì)SDRAM的寫入

2023-03-24 19:29:11

控制器的系統(tǒng)時(shí)鐘頻率相同,并且內(nèi)部命令的發(fā)送與數(shù)據(jù)傳輸都是以該時(shí)鐘為基準(zhǔn);動(dòng)態(tài)是指存儲(chǔ)陣列需要不斷的刷新來保證數(shù)據(jù)不丟失。

SDR SDRAM中的SDR是指單數(shù)據(jù)速率,即每一根數(shù)據(jù)線上,每個(gè)時(shí)鐘只傳輸

2023-03-23 17:40:58

電子發(fā)燒友App

電子發(fā)燒友App

評(píng)論