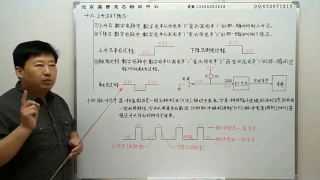

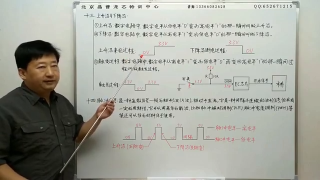

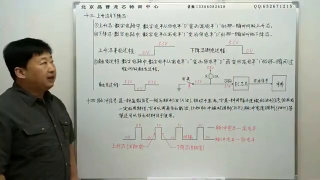

從字面上理解上升沿和下降沿是一個變量變化的時刻和一個無窮小的時間。但是plc程序中最小的時間單位是掃描周期,所以所謂的邊沿就是一個掃描周期。

?

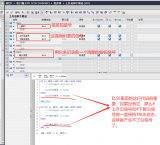

?上例中使用的bTrig變量都是用來讓下面的程序執(zhí)行一個掃描周期的,也可以理解為執(zhí)行bTrig的上升沿,和下面的編程效果一樣:

?

?上升功能塊R_TRIG的功能實際上是檢測輸入變量,當(dāng)輸入變量從低電平變?yōu)楦唠娖綍r,在第一掃描周期輸出高電平,然后輸出低電平。即,輸出一個掃描周期。

?

?與上升沿相同,下降沿檢測輸入變量從高到低變化的第一個掃描周期。

?

?為了理解的上升沿和下降沿的含義,我們可以靈活地將其應(yīng)用到程序中,比如讓程序執(zhí)行一個掃描周期,檢測一個變量的上升/下降沿,通過設(shè)置我們上面例子中的IF語句來重置一個變量,或者在案例中執(zhí)行一個條件后立即更改判斷變量的值,等等。

?

?本文原創(chuàng)首發(fā) www.nxhydt.com 源自 www.jcpeixun.com 轉(zhuǎn)載請注明出處,謝謝。

編輯:ymf

上升沿和下降沿是什么意思?

- plc(453901)

- 高電平(20884)

相關(guān)推薦

stm32外部中斷的邊沿檢測時,對上升沿或者下降沿是否有要求?

請問各位大佬,stm32外部中斷的邊沿檢測時,對上升沿或者下降沿是否有要求,必須小于或者大于多少時間,或者在多少時間內(nèi)必須上升或者下降多少V才算觸發(fā)。在spec中只看到了最小是10ns就可以,同時邊沿檢測的電平是GPIO的VIH和VIL嗎?

2024-03-20 08:31:04

使用HAL庫配置TIM2采集PWM測量頻率和脈沖寬度,如果將邊沿極性配置為上升+下降沿?

使用HAL庫配置TIM2采集PWM測量頻率和脈沖寬度,如果將邊沿極性配置為上升+下降沿,就可以一個通道測量頻率和占空比了,但是如何在HAL_TIM_IC_CaptureCallback中分辨此次中斷是由上升沿產(chǎn)生的,還是由下降沿產(chǎn)生的呢?

2024-03-12 06:52:38

HMC955LC4B

HMC955LC4B是一款1:2解復(fù)用器,支持高達(dá)32 Gbps的數(shù)據(jù)傳輸速率。該解復(fù)用器使用半速率時鐘的上升沿和下降沿對01-02序列中的數(shù)據(jù)進(jìn)行采樣,并在上升沿上將數(shù)據(jù)鎖存到差分輸出。該解復(fù)用器

2024-03-03 13:22:40

示波器探頭的工作原理與多功能應(yīng)用詳解

容性負(fù)載相當(dāng)于在被測電路上并聯(lián)了一個電容,對被測信號有濾波的作用,影響被測信號的上升下降時間,影響傳輸延遲,影響傳輸互連通道的帶寬。

2024-02-26 10:23:59 621

621

621

621

串行通信協(xié)議的帶寬是指什么?

在SPI和I2C等串行通信協(xié)議,兩者帶寬不一樣,這里的帶寬是指什么,傳輸速率還是其他什么?如果要求很高的傳輸速率,那么要求發(fā)送端要能很快的發(fā)送數(shù)據(jù),要有很短的上升沿下降沿時間,高低位電平也維持很短

2024-02-08 18:04:50

上升沿和下降沿是什么意思 上升沿和下降沿有何作用

上升沿和下降沿是什么意思 上升沿和下降沿有何作用? 上升沿和下降沿是在數(shù)字電路和信號處理中常用的概念,用于描述信號從低電平到高電平或從高電平到低電平的過程。 在數(shù)字電路中,信號通常是以離散的高電平

2024-02-06 14:50:04 1231

1231

1231

1231為什么脈沖數(shù)字信號的波形中其上升沿和下降沿展開后會有邊沿震蕩

為什么脈沖數(shù)字信號的波形中,其上升沿和下降沿展開后會有邊沿震蕩,求解釋 脈沖數(shù)字信號的波形中,上升沿和下降沿展開后會出現(xiàn)邊沿震蕩的現(xiàn)象。這個現(xiàn)象通常是由信號傳輸過程中的反射、傳導(dǎo)和輻射等因素產(chǎn)生

2024-02-06 14:49:41 245

245

245

245d觸發(fā)器有幾個穩(wěn)態(tài) 觸發(fā)器上升沿下降沿怎么判斷

的上升沿和下降沿。 一、SR觸發(fā)器 SR觸發(fā)器是最基本的觸發(fā)器之一,通過它可以實現(xiàn)存儲器、寄存器等功能。 SR觸發(fā)器有兩個輸入:S和R,以及兩個輸出:Q和Q'。在SR觸發(fā)器中,有四種不同的輸入組合,分別是: S=0,R=0:保持狀態(tài),穩(wěn)態(tài)

2024-02-06 13:36:55 366

366

366

366plc中常用的編寫程序的語言有哪些 plc中上升沿和下降沿怎么用

梯形圖是PLC中最常用和最廣泛支持的編程語言。它以線圖的形式展現(xiàn),使用繼電器邏輯圖形符號來表示邏輯關(guān)系和控制流程。

2024-01-10 15:04:17 143

143

143

143關(guān)于雅特力AT32F403A XMC復(fù)用模式驅(qū)動SRAM芯片

復(fù)用模式寫時序圖

SRAM寫時序參數(shù),看-55的

SRAM寫時序1,有刪減

.SRAM寫時序2

鎖存器74LVC273參數(shù),算上上升沿和下降沿,延遲至少11ns

其中sram

2024-01-04 10:46:19

使用LT8705過程中上下功率MOS管的死區(qū)時間最小是多少?

您好!

我請教一個關(guān)于LT8705死區(qū)時間的問題:客戶在使用LT8705過程中想確認(rèn)上下功率MOS管的死區(qū)時間最小是多少?目前客戶測試結(jié)果只有30ns左右。而根據(jù)MOS的上升沿和下降沿從20ns到40ns不等,有直通的風(fēng)險,請問LT8705是怎么調(diào)節(jié)死區(qū)時間防止直通的?謝謝!!

2024-01-03 06:23:18

AD9266輸出數(shù)據(jù)的沿和時鐘的沿為什么是對齊的?

AD9266輸出數(shù)據(jù)是在輸出時鐘的上升沿和下降沿處都有數(shù)據(jù),我的電路的是二進(jìn)制補碼輸出,10k的偏置電阻選用0.1%,電壓0.5v,輸出的DCS的時鐘沒有任何問題,頻率和沿都很穩(wěn)定,但是輸出的數(shù)據(jù)的沿和時鐘的沿是對齊的,這個和數(shù)據(jù)手冊的說明不同!!!糾結(jié)了很久,跪求可能的原因!!!

2023-12-22 08:12:03

怎么確定AD9923A的VPAT_NUM和VSEQ_NUM這兩個寄存器的值呢?

本人剛接觸關(guān)于CCD的知識,正在利用AD9923A調(diào)試ICX209AK,但在配置寄存器時遇到了一些問題,想問問各位做過類似項目的:

1.對于CCD所需的H1、H2、RG等信號,怎么確定它的上升沿

2023-12-22 07:58:47

使用AD9266遇到的問題求解

使用?2.ad9266是CMOS DDR數(shù)據(jù)輸出,通過管腳配置成二進(jìn)制補碼形式,DDR數(shù)據(jù)送到fpga,fpga選用xilinx的XC6SLX75,fpga內(nèi)部在ad9266輸出的ad_dco時鐘的上升沿和下降沿

2023-12-22 06:59:24

ad9942 Hcounter在VD_X下降沿的后第七個cli上升沿置0,這里的作用是是什么?

問題1 如下圖,Hcounter 在VD_X下降沿的后第七個cli上升沿置0,這里的作用是是什么,為什么在第七個位置置0?Hcounter 在ad9942內(nèi)部那些信號或者序列會使用到? 有沒有VD

2023-12-21 06:08:03

AD2S1200串行輸出波形為什么在上升沿就變化了?

應(yīng)該是在下降沿才會有數(shù)據(jù)變化的啊,上圖中有在上升沿就變化了,這是什么原因啊???

急急急!!!

2023-12-20 06:14:13

AD9781或是AD9783芯片的DCOP/DCON信號有什么用?

/DCON信號是AD給FPGA發(fā)信數(shù)據(jù)使用的,如上升沿時FPGA發(fā)送I路信號,下降沿時FPGA發(fā)送Q路信號,此時上升沿與下降沿需要在I或Q路信 號的中間位置么,就是保證上升沿與下降沿時,I和Q路信號有

2023-12-18 06:41:34

AD7764啟動采樣的時鐘是MCLK還是SCO,如果是SCO,是上升沿啟動還是下降沿啟動?

最近在使用AD7764,有幾個不懂的地方想請教一下:

1.AD7764啟動采樣的時鐘是MCLK還是SCO,如果是SCO,是上升沿啟動還是下降沿啟動?

2.根據(jù)datasheet操作指引,上電后

2023-12-15 07:05:23

關(guān)于AD6688采樣單音信號時比較奇怪的現(xiàn)象

的2211.84MHz,當(dāng)我給一個2211.84MHz的正弦信號時,我期待得到的是一條直線,因為頻率被移動到了DC了。但是采集回來的數(shù)據(jù)卻很奇怪,在一段時間會是固定的,但是另一端時間會有上升沿和下降沿

2023-12-01 07:09:14

AD8561單+5V供電,方波輸入,仿真下降沿比上升沿延時大是為什么?

AD8561單+5V供電,方波輸入,仿真下降沿比上升沿延時大,如果雙電源則延時則一樣,實際應(yīng)用是否也是這樣?官網(wǎng)的pspice模型

2023-11-24 06:17:21

i.MX-6ULL --ElfBoard SPI接口介紹

主設(shè)備。一主多從情況如下圖:

SPI 具有 4 種工作方式,時鐘極性(CPOL)和相位(CPHA)共同決定讀取數(shù)據(jù)的方式,比如信號上升沿讀取數(shù)據(jù)還是信號下降沿讀取數(shù)據(jù),并且一個片選信號可以設(shè)置一種模式

2023-11-21 10:19:05

AD817運放輸出大約1V的振鈴怎樣處理?

用AD817運放搭建的負(fù)反饋電路中,空載測試輸出波形在上升沿和下降沿會出現(xiàn)1V多的振鈴,應(yīng)該怎樣處理能把振林消除

2023-11-17 15:07:28

ada4870是否可以用作直流線性電源?

100pf-10nf。

目前,我們已經(jīng)驗證的電路采用了類似于線性電源的結(jié)構(gòu),如圖所示。

現(xiàn)在存在的問題是:圖1中,三極管射級輸出的直流電平存在較大的紋波,同時推完電路輸出方波的上升沿和下降沿存在

2023-11-17 14:10:15

用AD8009放大500uv的方波,電壓抬升怎么優(yōu)化?

您好:

我希望放大一個500uv的1PPS方波,需要比較好的上升沿和下降沿性能,選用了AD8009,放大了300倍,測試后發(fā)現(xiàn)電壓被抬高很多,是否是Vos引起的?

閱讀相關(guān)帖子,我現(xiàn)在覺得我的設(shè)計有

2023-11-14 06:07:04

ADL5303光電二極管放大電路,低輸入光抖動如何消除?

您好!

我使用ADL5303做光電二極管放大電路,因為響應(yīng)速度的原因使用RC濾波電路會導(dǎo)致信號上升沿和下降沿時間變長,所以C118和C122都不能焊接,在低輸入光時Vlog端有出現(xiàn)520KHZ、1MHZ、1.5MHZ的抖動,使用多種方法仍然無法消除,想尋求解決抖動的方法,謝謝!

2023-11-13 06:30:13

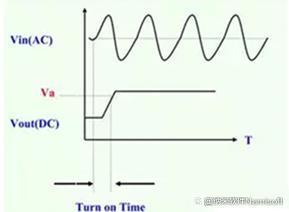

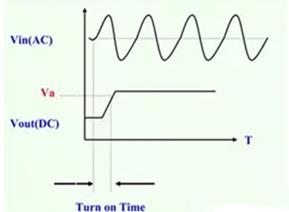

使用ATECLOUD電源測試系統(tǒng)測試啟動延遲和上升/下降時間

在集成電路中經(jīng)常會使用電源模塊來保證電路的穩(wěn)壓輸出,所以電源模塊的應(yīng)用十分的廣泛

2023-11-09 17:33:41 576

576

576

576

SPI的MISO管腳的波形上升沿和下降沿都有很大的弧度是什么原因?

示波器測量SPI通訊的CS,CLKMOSIMISO四顆線的信號,發(fā)現(xiàn)其他都很好,只有MISO的信號上升沿和下降沿都是有很大弧度的,是什么原因,如何解決?

2023-11-08 06:19:01

納米軟件電源模塊測試之啟動延遲和上升/下降時間

電源模塊的啟動延遲指從施加啟動輸入電壓到輸出電壓達(dá)到電壓額定值時所需的時間,上升時間是指電源模塊從歸零待機狀態(tài)到啟動狀態(tài)所需的時間,下降時間指的是電源模塊從工作狀態(tài)到歸零待機狀態(tài)所需的時間。

2023-10-09 15:50:04 307

307

307

307

STC8系列單片機技術(shù)參考手冊

、增強型 PWM、增強型 PWM 異常檢測、ADC 模數(shù)轉(zhuǎn)換中斷、LVD 低壓檢測、SPI 中斷、I2C 中斷、比較器中斷喚醒。STOP 模式可以由 INT0/INT1 端口上升沿/下降沿、INT2

2023-09-26 07:36:13

求分享K210裸機開發(fā)的寄存器手冊

K210芯片使用PWM時,無法指定對齊下降沿或者上升沿,從0計數(shù)到loadcount2翻轉(zhuǎn)為低,然后從0計數(shù)到channel[N].loadcount再翻轉(zhuǎn)為高,無法通過current_value

2023-09-15 07:36:14

異步時鐘同步疑惑

?也就是說采樣異步時鐘域信號時不打拍有什么后果?

另外,當(dāng)高速時鐘采樣慢速上升沿或下降沿時,采樣結(jié)果抖動怎么處理?比如DS18B20長線驅(qū)動時,波形上升沿和下降沿被長線的線間電容牽制導(dǎo)致波形邊沿變化緩慢 ,采用打2拍方式能否有用?

此圖采樣到緩慢上升沿時,采樣結(jié)果抖動波形。

2023-09-12 20:39:18

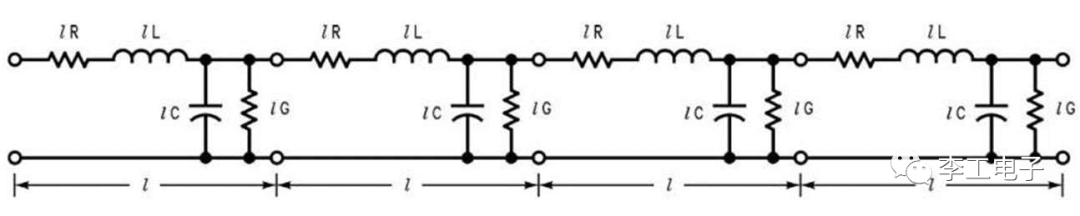

走線什么時候必須作為傳輸線考慮?

簡單地說,傳輸線是由兩條有一定長度的導(dǎo)線組成。如果信號在導(dǎo)線上的傳輸時間大于信號的跳變沿(上升沿/下降沿)時間的一半,則該走線判定為傳輸線。

2023-09-06 14:49:28 215

215

215

215

N9H20K51 gpio觸發(fā)后一直未進(jìn)中斷是為什么?

輸入模式

gpio_setintmode (GPIO_PORTE, BIT11, 1, 1);//設(shè)置中斷模式上升沿 和下降沿

gpio_setsrcgrp(GPIO_PORTE,BIT11

2023-09-04 07:40:57

求助,在STM32上RTT可以使用IO中斷模擬I2C從機接收數(shù)據(jù)嗎?

使用IO中斷在SCL上升沿和下降沿接收解析SDA的狀態(tài)讀取IIC數(shù)據(jù),RTT的IO中斷可以及時響應(yīng)嗎?

2023-09-03 09:49:08

有源晶振的電氣參數(shù):波形上升下降時間

晶振的輸出波形為單端輸出(Sine/Clipped Sine, CMOS/TTL) 和差分輸出(LVPECL, LVDS, HCSL)。差分輸出可以滿足高速數(shù)據(jù)傳輸,應(yīng)用于高速計算機,數(shù)字通信系統(tǒng),雷達(dá),測量儀器,頻率合成器等。

2023-08-25 11:01:08 619

619

619

619

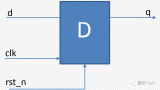

RTL設(shè)計規(guī)范有哪些?一個RTL用例設(shè)計介紹

D觸發(fā)器結(jié)構(gòu)如下圖所示,先有時鐘上升沿,然后才有D的值賦給Q,沒有上升沿Q值保持不變,時序邏輯在時鐘上升沿/下降沿后才變化

2023-08-18 10:23:36 1149

1149

1149

1149

M0518LD2設(shè)置上升沿中斷,但卻也相應(yīng)了下降沿中斷是為什么?

M0518LD2 外部中斷初始化時設(shè)置PD6為上升沿中斷,但經(jīng)查看波形發(fā)現(xiàn) PD6在下降沿時也觸發(fā)了中斷,不知為何?

2023-08-18 06:13:40

ARM MultiTrace用戶指南

·支持4位、8位和16位的數(shù)據(jù)端口寬度。

·支持半速率跟蹤時鐘,可在時鐘上升沿和下降沿捕獲數(shù)據(jù)。

·SoC電壓可以在1.0至3.3V的范圍內(nèi)。

·軌跡信息以10 ns的分辨率進(jìn)行時間標(biāo)記。

·多重跟蹤

2023-08-16 06:11:46

淺析PLC的上升沿與下降沿

有網(wǎng)友留言說:上升沿就是在信號從斷開到接通的那一瞬間接通,下降沿就是在信號從接通到斷開的那一瞬間接通。但是現(xiàn)在的問題它的實際用處是用在哪一些情況。我身邊也有PLC可以做個什么實驗來體驗一下呢?

2023-07-26 09:24:30 1470

1470

1470

1470HMC855LC5是一款串行器

HMC855LC5是一款1:4解復(fù)用器,設(shè)計用于高達(dá)28 Gbps數(shù)據(jù)解串應(yīng)用。 該器件使用半速率時鐘的上升沿和下降沿來采樣輸入數(shù)據(jù)序列D0-D3,并將數(shù)據(jù)鎖存至差分輸出。 片上生成1/4速率時鐘

2023-07-11 09:43:06

HMC854LC5是一款串行器

HMC854LC5是一款4:1多路復(fù)用器,設(shè)計用于28 Gbps數(shù)據(jù)串行應(yīng)用。 多路復(fù)用器在輸入時鐘的上升沿鎖存四個差分輸入。 該器件使用半速率時鐘的上升沿和下降沿來串行傳輸數(shù)據(jù)。 片上生成1/4

2023-07-11 09:39:21

HMC955LC4B是一款串行器

HMC955LC4B是一款1:2解復(fù)用器,支持高達(dá)32 Gbps的數(shù)據(jù)傳輸速率。該解復(fù)用器使用半速率時鐘的上升沿和下降沿對01-02序列中的數(shù)據(jù)進(jìn)行采樣,并在上升沿上將數(shù)據(jù)鎖存到差分輸出。該解復(fù)用器

2023-07-11 09:32:57

HMC954LC4B是一款復(fù)用器

HMC954LC4B是一款2:1多路復(fù)用器,設(shè)計用于32 Gbps數(shù)據(jù)串行應(yīng)用。 多路復(fù)用器在輸入時鐘的上升沿鎖存兩個差分輸入。 該器件使用半速率時鐘的上升沿和下降沿來串行傳輸數(shù)據(jù)

2023-07-11 09:30:01

關(guān)于N76E003的輸入捕獲的一些知識,不看后悔

的方式,支持雙邊沿,上升沿,下降沿,具體按照實際需求來

(5) 設(shè)置CAPCR,這個是關(guān)鍵的步驟,設(shè)置這個之后在發(fā)生了捕獲事件之后就會直接將定時器的值清0,重新開始計時,這樣的好處是我們完全可以不去

2023-06-25 08:42:33

ECSPI不是和標(biāo)準(zhǔn)的SPI重合嗎?

根據(jù) IMX6ULLRM,它讀取當(dāng)相位控制 (ECSPI_CONREG[PHA]) 位置位時,發(fā)送數(shù)據(jù)將在 SCLK 的上升沿移出,接收數(shù)據(jù)在 SCLK 的下降沿鎖存。最高有效位在第一個 SCLK

2023-06-08 09:44:27

西門子1200上升沿和下降沿的操作流程

通過上面的這個程序,我們就得到了上升沿信號和下降沿信號。比如說,當(dāng)形參“I_請求1”的實參”I0.0”從0變1時,那么形參“上升沿信號”就變?yōu)榱?。此時,我們就可以用這個形參=1的信號來做事情了。

2023-06-01 16:49:57 2846

2846

2846

2846

如何從ISR的上升沿讀取GPIO?

我在 GPIO_INTR_ANYEDGE 上配置了一個 GPIO ISR。

我想在 ISR 中知道它是上升沿還是下降沿。

怎么做?

如果我只是在 ISR 中讀取 GPIO 狀態(tài),它幾乎總是 0,即使

2023-05-30 10:37:08

開關(guān)電源MOSFET關(guān)斷緩沖電路

Q關(guān)斷,集電極電壓開始上升到2Vdc,電容C限制集電極電壓的上升速度,并減小上升電壓和下降電流的重疊,減低開關(guān)管Q的損耗。

2023-05-30 09:18:01 732

732

732

732

是否可以讓FSYNC數(shù)據(jù)在上升沿而不是下降沿觸發(fā)限定符?

31 位。我們計劃使用限定符來同步 32 位數(shù)據(jù)和 FSYNC。是否可以讓 FSYNC 數(shù)據(jù)在上升沿而不是下降沿觸發(fā)限定符?

2023-05-24 10:30:57

IMX8MN如果我們配置GPT在上升沿/下降沿觸發(fā)中斷,如何知道中斷是由下降沿還是上升沿觸發(fā)?

以獲得一個數(shù)組,其中包含每個 0 和 1 轉(zhuǎn)換的持續(xù)時間

我的想法是在輸入捕獲模式下使用 GPT 1,配置為觸發(fā)上升沿和下降沿的中斷,并在中斷中獲取位 (0/1) 的持續(xù)時間并將其存儲在數(shù)組中

2023-05-12 06:35:59

在時序電路里如何利用一個信號的上升沿和下降沿采樣數(shù)據(jù)呢?

外部輸入一個周期信號和一個數(shù)據(jù),我要利用這個周期信號的上升沿和下降沿采樣數(shù)據(jù)。除了利用高頻時鐘去檢測周期信號的上升沿和下降沿變換外,還有什么方法?

2023-05-10 10:36:28

在時序電路里如何利用一個信號的上升沿和下降沿采樣數(shù)據(jù)呢?

外部輸入一個周期信號和一個數(shù)據(jù),我要利用這個周期信號的上升沿和下降沿采樣數(shù)據(jù)。除了利用高頻時鐘去檢測周期信號的上升沿和下降沿變換外,還有什么方法?

2023-05-10 10:35:59

是否有可能在不添加/使用FTM1模塊和其他通道的情況下為PWM的每個上升沿或下降沿束獲得中斷/回調(diào)?

我正在使用S32K32118 EVB和S32DS.3.5

通過S32 配置工具,我在 FTM0、CH0 上創(chuàng)建了一個 PWM 波形。

我想知道是否有可能在不添加/使用 FTM1 模塊和其他通道的情況下為 PWM 的每個上升沿或下降沿(或至少在新周期開始/結(jié)束時)獲得中斷/回調(diào) 。

2023-05-04 08:27:26

安捷倫AFG3102波形發(fā)生器

長達(dá)128K的任意波形。在脈沖波形上可以單獨設(shè)置上升沿和下降沿時間。可以將外部信號連接,并疊加到輸出信號中。雙通道型號輸出可生成兩個完全相同或截然不同的信號。所有

2023-04-18 10:05:02

CH32V103基礎(chǔ)教程9-輸入捕獲

捕獲可對輸入信號的上升沿、下降沿或者雙邊沿進(jìn)行捕獲,其捕獲原理為:當(dāng)發(fā)生并捕獲信號跳變沿之后,計數(shù)器(CNT)值將被鎖存到捕獲比較寄存器(CCR)中,將前后兩次捕獲到的CCR寄存器中的值相減,即可計算出頻率或者脈寬。如果捕獲脈寬時長超過捕獲定時器的周期,會發(fā)生溢出,此時需要進(jìn)行額外處理。

2023-04-14 16:17:39

KEA8 KBI下降沿和上升沿問題求解

我正在FRDM - KEAZ128 上開發(fā)新代碼,我需要在下降沿和上升沿攔截單個引腳上的中斷,但從文檔來看,似乎只能使用下降沿或上升沿。它是否正確?如果沒有辦法在兩個邊緣設(shè)置 IRQ,唯一的其他方法是使用 ACMP 外圍設(shè)備或“更智能”的方法可用?

2023-03-23 07:53:32

電子發(fā)燒友App

電子發(fā)燒友App

評論