來(lái)源:?半導(dǎo)體行業(yè)觀察

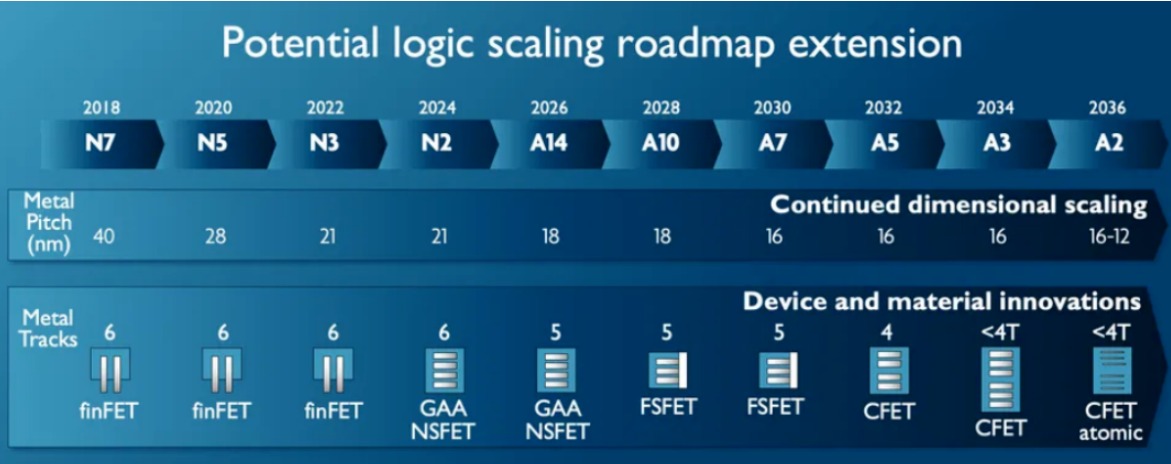

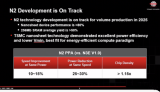

半導(dǎo)體制程已經(jīng)進(jìn)展到了3nm,今年開(kāi)始試產(chǎn),明年就將實(shí)現(xiàn)量產(chǎn),之后就將向2nm和1nm進(jìn)發(fā)。相對(duì)于2nm,目前的1nm工藝技術(shù)完全處于研發(fā)探索階段,還沒(méi)有落地的技術(shù)和產(chǎn)能規(guī)劃,也正是因?yàn)槿绱耍沟?nm技術(shù)具有更多的想象和拓展空間,全球的產(chǎn)學(xué)研各界都在進(jìn)行著相關(guān)工藝和材料的研究。

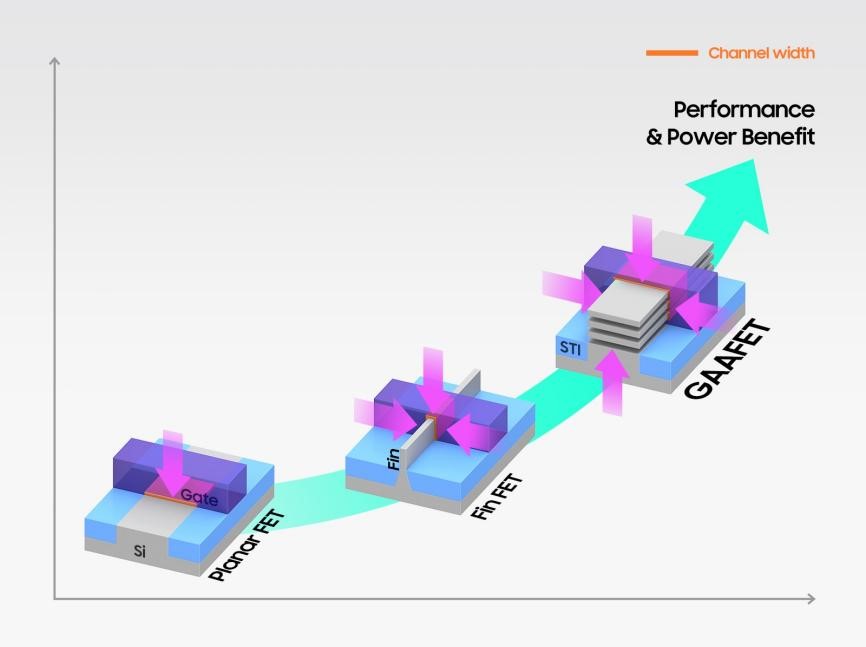

上周,IBM和三星公布了一種在芯片上垂直堆疊晶體管的新設(shè)計(jì),被稱為垂直傳輸場(chǎng)效應(yīng)晶體管 (Vertical Transport Field Effect Transistors,VTFET)。當(dāng)前的處理器和SoC,晶體管平放在硅表面上,然后電流從一側(cè)流向另一側(cè)。相比之下,VTFET彼此垂直,電流垂直流動(dòng)。該技術(shù)有望突破1nm制程工藝瓶頸。

IBM和三星表示,這種設(shè)計(jì)有兩個(gè)優(yōu)點(diǎn)。首先,它可以繞過(guò)許多性能限制,將摩爾定律擴(kuò)展到IBM當(dāng)前的納米片技術(shù)之外,更重要的是,由于電流更大,該設(shè)計(jì)減少了能源浪費(fèi),他們估計(jì)VTFET將使處理器的速度比采用 FinFET?晶體管設(shè)計(jì)的芯片快兩倍或功耗降低 85%。IBM和三星聲稱,這一工藝技術(shù)有望允許手機(jī)一次充電使用整整一周。他們表示,它還可以使某些能源密集型任務(wù)(包括加密采礦)更加節(jié)能,因此對(duì)環(huán)境的影響較小。

IBM?和三星尚未透露他們計(jì)劃何時(shí)將該工藝技術(shù)商業(yè)化。他們并不是唯一一家試圖突破 1 nm瓶頸的公司。今年5月,臺(tái)積電與合作伙伴發(fā)布了1nm工藝技術(shù)路徑;7?月,英特爾表示,其目標(biāo)是在 2024?年之前完成埃級(jí)芯片的設(shè)計(jì)。該公司計(jì)劃使用其新的“英特爾 20A”制程節(jié)點(diǎn)和 RibbonFET?晶體管來(lái)實(shí)現(xiàn)這一目標(biāo)。

?

臺(tái)積電依然是先鋒

近年來(lái),科學(xué)界一直在尋找可以替代硅的二維材料,挑戰(zhàn)1nm以下的制程工藝,但至今未能解決二維材料的高阻、低電流問(wèn)題。

近些年,在先進(jìn)制程的研發(fā)和商業(yè)化方面,臺(tái)積電一直是行業(yè)先鋒。

今年5月,臺(tái)積電、中國(guó)臺(tái)灣大學(xué)(NTU)和麻省理工學(xué)院(MIT)聯(lián)合宣布,1nm芯片研發(fā)取得重大突破。

該突破主要體現(xiàn)在材料方面,使用半金屬鉍(Bi)作為二維(2D)材料的接觸電極,可以大大降低電阻并增加電流。這可以實(shí)現(xiàn)接近現(xiàn)有半導(dǎo)體尺寸物理限制的能源效率。該消息是在IBM早些時(shí)候宣布其2nm芯片之后發(fā)布的。

每一種新的工藝技術(shù)都會(huì)帶來(lái)新的挑戰(zhàn),在這種情況下,關(guān)鍵挑戰(zhàn)是找到合適的晶體管結(jié)構(gòu)和材料。同時(shí),為晶體管供電的晶體管觸點(diǎn)對(duì)其性能至關(guān)重要。半導(dǎo)體工藝技術(shù)的進(jìn)一步小型化增加了接觸電阻,從而限制了它們的性能。因此,芯片制造商需要找到一種電阻非常低、可以傳輸大電流并且可以用于量產(chǎn)的觸點(diǎn)材料。

使用半金屬鉍作為晶體管的接觸電極可以大大降低電阻并增加電流。目前,臺(tái)積電使用鎢互連晶體管,而英特爾使用鈷互連。兩者都有其優(yōu)點(diǎn),并且都需要特定的設(shè)備和工具。

為了使用半金屬鉍作為晶體管的接觸電極,研究人員不得不使用氦離子束 (HIB)?光刻系統(tǒng)并設(shè)計(jì)一種“簡(jiǎn)單的沉積工藝”。這種工藝僅用于研發(fā)生產(chǎn)線,因此還沒(méi)有完全準(zhǔn)備好進(jìn)行大規(guī)模生產(chǎn)。

目前,臺(tái)積電的 1nm?制程節(jié)點(diǎn)仍處于探索階段,工廠正在嘗試各種選項(xiàng),也不能保證未來(lái)量產(chǎn)時(shí)確定使用半金屬鉍。

?

IMEC指向2027

近日,比利時(shí)微電子研究中心 (IMEC)表示,1nm制程2027年就可實(shí)現(xiàn)商業(yè)化,之后的0.7nm?預(yù)計(jì)將在2029年后實(shí)現(xiàn)量產(chǎn)。

IMEC的CEO Luc Van den hove博士在接受采訪時(shí)強(qiáng)調(diào),搭配全新技術(shù),“摩爾定律要前進(jìn)多少個(gè)世代都不是問(wèn)題。”據(jù)悉,IMEC和ASML合作的EUV設(shè)備研發(fā)工作正在進(jìn)行,日本的 TEL也參與其中,預(yù)計(jì)測(cè)試設(shè)備有望在2023年初完成,也有企業(yè)打算在2026年投入量產(chǎn)。

此外,IMEC還開(kāi)發(fā)了一種新方法,可以在采用1nm制程工藝技術(shù)構(gòu)建的芯片中使用金屬互連來(lái)減輕焦耳熱效應(yīng)。

IMEC研究人員表示,在對(duì)基于鋁的二元化合物的實(shí)驗(yàn)研究中,重點(diǎn)關(guān)注其電阻率,化學(xué)計(jì)量的AlCu和Al2Cu薄膜的電阻率低至9.5μΩcm。這些結(jié)果在實(shí)驗(yàn)上支持它們?cè)谙冗M(jìn)的半鑲嵌互連集成方案中用作新導(dǎo)體的承諾,在這些方案中,它們可以與氣隙結(jié)合以提高性能。然而,在這種組合中,焦耳熱效應(yīng)變得越來(lái)越重要。這是通過(guò)在12層后端 (BEOL)?結(jié)構(gòu)中結(jié)合實(shí)驗(yàn)和建模工作預(yù)測(cè)的。

1nm制程需要在后端最關(guān)鍵的層中引入新的導(dǎo)體材料,如二元和三元金屬間化合物(例如,Al?或 Ru?基),其電阻率低于按比例尺寸的常規(guī)元素金屬(例如 Cu、Co、Mo?或 Ru)。IMEC已經(jīng)通過(guò)實(shí)驗(yàn)研究了鋁化物薄膜的電阻率,包括 AlNi、Al 3 Sc、AlCu?和 Al 2 Cu。在20nm?及以上厚度時(shí),所有 PVD?沉積膜的電阻率與 Ru?或 Mo?相當(dāng)或更低。28nm?的 AlCu?和 Al 2膜的最低電阻率達(dá)到 9.5 μΩcmCu –?低于 Cu?的值。

IMEC設(shè)想在先進(jìn)的半鑲嵌集成方案中引入金屬間化合物,包括直接蝕刻可圖案化金屬以實(shí)現(xiàn)更高縱橫比的線條。通過(guò)在金屬線之間逐漸引入部分或全部氣隙,可以進(jìn)一步改善 RC?延遲。用電隔離氣隙代替?zhèn)鹘y(tǒng)的低 k?電介質(zhì)有望降低按比例尺寸的電容。但是氣隙的導(dǎo)熱性極差,這引起了對(duì)操作條件下焦耳熱的擔(dān)憂。

IMEC通過(guò)在局部 2?層金屬互連級(jí)別執(zhí)行焦耳熱“校準(zhǔn)”測(cè)量并通過(guò)建模將結(jié)果投影到 12?層 BEOL?結(jié)構(gòu),量化了這一挑戰(zhàn)。該研究預(yù)測(cè),空氣間隙會(huì)使溫度升高 20%。發(fā)現(xiàn)金屬線的密度起著重要作用:較高的金屬密度顯示有助于降低焦耳熱。

“這些研究結(jié)果是改進(jìn)半鑲嵌金屬化方案作為1nm制程互連選項(xiàng)的關(guān)鍵,” IMEC研究員兼納米互連項(xiàng)目總監(jiān) Zsolt Tokei?說(shuō)。“此外,IMEC正在通過(guò)其它選項(xiàng)擴(kuò)展互連路線圖,包括混合金屬化和新的中間線方案,同時(shí)解決與工藝集成和可靠性相關(guān)的關(guān)鍵挑戰(zhàn)。”

?

1nm之后將如何發(fā)展?

當(dāng)硅基芯片突破1nm之后,量子隧穿效應(yīng)大增,將形成“電子失控”,使芯片失效。這種情況下,替換芯片的硅襯底,也許是芯片進(jìn)一步發(fā)展的可行出路之一。

電子可以連續(xù)地從一個(gè)門(mén)流向下一個(gè)門(mén),而不是停留在預(yù)期的邏輯門(mén)內(nèi),這在本質(zhì)上使得晶體管不可能處于關(guān)閉狀態(tài)。

由于晶體管由三個(gè)端子組成:源極,漏極和柵極。電流從源極流向漏極,并由柵極控制,柵極根據(jù)施加的電壓而進(jìn)行導(dǎo)通或關(guān)斷電流。

硅和二硫化鉬(MoS2)都具有晶格結(jié)構(gòu),但是通過(guò)硅的電子有效質(zhì)量比二硫化鉬小。當(dāng)柵極長(zhǎng)度為5nm或更長(zhǎng)時(shí),硅晶體管可以正常工作。

而通過(guò)二硫化鉬的電子有更高的有效質(zhì)量,他們的流動(dòng)可以通過(guò)更小的門(mén)長(zhǎng)度來(lái)控制。勞倫斯伯克利國(guó)家實(shí)驗(yàn)室對(duì)此方案的可行性進(jìn)行了實(shí)驗(yàn)驗(yàn)證,但該研究仍處于非常早期的階段。

一個(gè)14nm制程芯片上有超過(guò)10億個(gè)晶體管,而伯克利實(shí)驗(yàn)室團(tuán)隊(duì)還沒(méi)有開(kāi)發(fā)出一種可行的方法來(lái)批量生產(chǎn)新的1nm晶體管,甚至還沒(méi)有開(kāi)發(fā)出使用這種晶體管的芯片。

但是哪怕僅僅作為概念的證明,這里的結(jié)果仍然是非常重要且令人鼓舞的,期待后續(xù)新材料的發(fā)現(xiàn)可以繼續(xù)允許更小的晶體管尺寸,并隨之提高未來(lái)芯片的能效。

?

中國(guó)也有亮點(diǎn)

目前,全球1nm制程工藝都處于研發(fā)探索階段,距離商業(yè)化生產(chǎn)還要幾年的時(shí)間。因此,雖然中國(guó)大陸地區(qū)的先進(jìn)制程工藝的商業(yè)化水平不高,但在相關(guān)的理論研究方面也在跟隨國(guó)際前沿。例如,湖南大學(xué)在1nm制程工藝的研究方面也有亮眼的表現(xiàn)。

今年6月,湖南大學(xué)的研究團(tuán)隊(duì)研發(fā)出了超短溝道的垂直場(chǎng)效應(yīng)晶體管(VFET)。這種晶體管技術(shù),可以把晶體管做到3nm大小,而溝道長(zhǎng)度只需要0.65nm。在以往的制程工藝中,溝道長(zhǎng)度代表的就是芯片制程,也就是說(shuō)0.65nm的溝道長(zhǎng)度,就意味著0.65nm制程。

就是晶體管不是平行排列的,是垂直排列的。這種縱向的結(jié)構(gòu)具有天然的短溝道特性,半導(dǎo)體溝道位于底電極與頂部電極之間,溝道長(zhǎng)度僅取決于材料厚度。

更重要的是,這種垂直場(chǎng)效應(yīng)晶體管不是平行排列的,是垂直排列的。這種縱向的結(jié)構(gòu)具有天然的短溝道特性,半導(dǎo)體溝道位于底電極與頂部電極之間,溝道長(zhǎng)度僅取決于材料厚度。

研究人員采用了范德華(vdW)金屬電極集成方法,以二硫化鉬(MoS2)作為半導(dǎo)體溝道的薄層甚至單原子層,也就是說(shuō)溝道長(zhǎng)度,其實(shí)就是一層二硫化鉬材料的厚度,所以最短達(dá)到了0.65nm。由于排列方式的不同,無(wú)需縮短晶體管與晶體管之間的距離,搭積木式的一層一層往上壘就行了,這就使其不完全依賴于高精度光刻機(jī)。不過(guò),該研究只是實(shí)驗(yàn)室的產(chǎn)物,要真正走向量產(chǎn),還有很長(zhǎng)的路要走。

?

向1nm光刻機(jī)進(jìn)發(fā)

以上談的都是工藝技術(shù)和材料的研發(fā),要實(shí)現(xiàn)1nm制程的落地,制造設(shè)備,特別是EUV光刻機(jī)是必不可少的,這就不得不提到ASML。

目前,ASML的主力出貨EUV光刻機(jī)分別是NXE:3400B?和3400C,這兩款機(jī)型的數(shù)值孔徑(NA)均為0.33,其中更新一款的3400C?的可用性已經(jīng)達(dá)到90%?左右。

ASML預(yù)期,到今年年底,NXE:3600D?將會(huì)開(kāi)始進(jìn)行交付,該設(shè)備的匹配套精準(zhǔn)度提升了,在30mJ/cm2下的晶圓吞吐量達(dá)到160片,相比3400C提高了18%,將會(huì)成為未來(lái)臺(tái)積電和三星3nm制程工藝的主要設(shè)備。

除此之外,ASML還公布了未來(lái)的三代光刻機(jī)研發(fā)計(jì)劃,三款機(jī)型的型號(hào)分別是NEXT、EXE:5000?和EXE:5200。從EXE:5000開(kāi)始,將數(shù)值孔徑提高到了0.55。

0.55NA?比0.33NA?有著巨大的提升,包括更高的對(duì)比度,圖像曝光成本更低等,是未來(lái)發(fā)展的趨勢(shì)。

目前,硅片、曝光潔凈室已經(jīng)逼近物理極限,現(xiàn)在的5nm/7nm?光刻機(jī)變得十分精密,設(shè)備零件多達(dá)10萬(wàn)+、體積為40個(gè)貨柜。據(jù)悉,1nm?光刻機(jī)體積要比現(xiàn)在3nm?的多出一倍。

由于光刻機(jī)擁有非常多的零件,需要高精度的裝配,導(dǎo)致光刻機(jī)從發(fā)貨到配置/培訓(xùn)的整個(gè)流程需要長(zhǎng)達(dá)兩年時(shí)間。按照這個(gè)參考推算,預(yù)計(jì)0.55NA?的大規(guī)模應(yīng)用得2025~2026年了,那時(shí),大概率是1nm制程工藝試產(chǎn)時(shí)段。

?

結(jié)語(yǔ)

以上這些只是目前行業(yè)內(nèi)進(jìn)行1nm制程相關(guān)研發(fā)工作的代表,并非全部。相信隨著3nm的量產(chǎn),以及2nm進(jìn)入商業(yè)化階段,1nm制程的研發(fā)會(huì)逐步成熟,當(dāng)下的這些實(shí)驗(yàn)室級(jí)研究,預(yù)估將有不少會(huì)落地到晶圓廠,同時(shí),還將會(huì)有更新的工藝和材料技術(shù)誕生。

封面圖片來(lái)源:半導(dǎo)體行業(yè)觀察

免責(zé)聲明:該文章系轉(zhuǎn)載,登載該文章目的為更廣泛的傳遞市場(chǎng)信息,文章內(nèi)容僅供參考。

如有內(nèi)容圖片侵權(quán)或者其他問(wèn)題,請(qǐng)聯(lián)系半導(dǎo)體芯科技進(jìn)行刪除。

?

審核編輯:ymf

電子發(fā)燒友App

電子發(fā)燒友App

評(píng)論