摘要

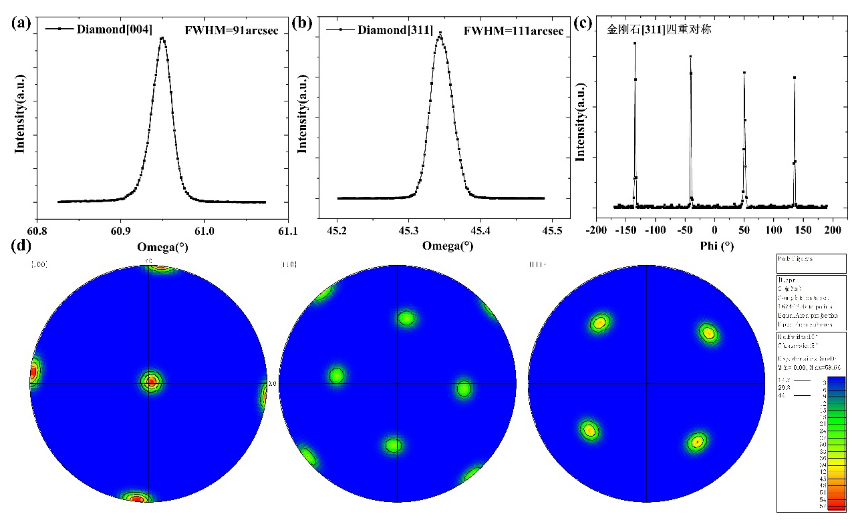

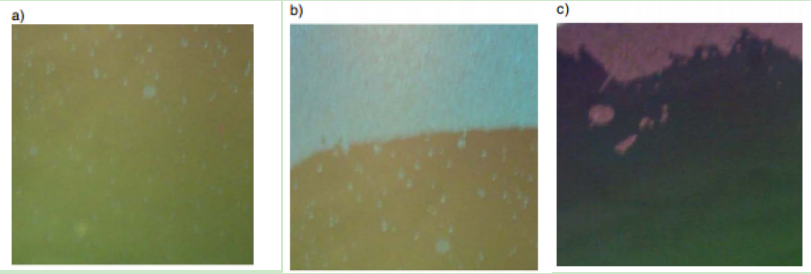

厚度約為1毫米的大面積均勻多晶金剛石薄膜在4英寸的襯底上生長并形成圖案。 氧化硅晶片使用集成電路兼容工藝的微系統應用。通過在4英寸上旋轉金剛石粉末裝載水,實現了密度為2X 1010 /cm2的均勻、可重復的播種。晶圓片。MPCVD系統中采用1.5%甲烷氫氣混合物,優化壓力和微波功率進行金剛石薄膜生長。4in的厚度變化小于20%。面積使用43托爾壓力和2.8kW微波功率。利用六氟化硫/O2/Ar氣體進行電子回旋共振ECR輔助微波等離子體反應離子蝕刻,蝕刻速率約為80nm/min,蝕刻速率的蝕刻速率變化小于10%區域的面積。

介紹

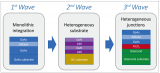

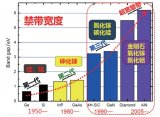

金剛石晶格中sp3C-C鍵的存在導致了其獨特的機械、化學、光學和熱性能,這與任何其他已知材料都不匹配。因此,金剛石成為一種獨特的材料的應用,包括微系統和微機電系統的MEMSd,特別是在高溫和惡劣的環境下。制造sp3C-C鍵的困難將化學氣相沉積CVDd金剛石的生產推遲到1952-53年,現在導致了一種可靠的金剛石微制造技術的發展延遲,該技術與傳統的微系統/MEMS技術兼容。由于目前還沒有可靠的大面積金剛石熱外延技術,許多研究主要集中在廉價的多晶金剛石多晶硅上,主要生長在小于2英寸的硅晶片上。雖然有些研究使用了4英寸。本文著重于所有這些問題,以發展和優化微系統的聚c技術。

聚c微系統技術

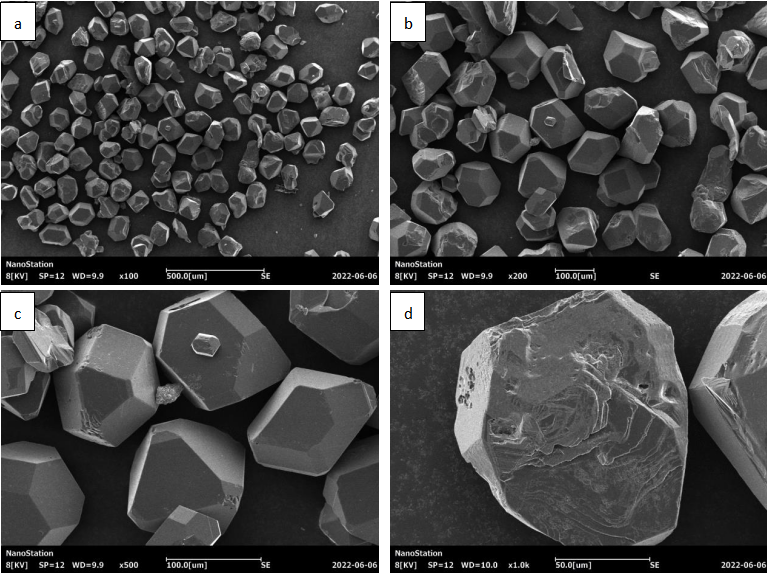

Seeding:本研究開發了一種能更好地控制均勻度和高密度的大面積播種新技術。通過在1000毫升去離子水中混合25克拉平均粒度為25納米的金剛石粉末,并加入懸浮試劑,制備負載金剛石粉末的水sDPLWd溶液。DPLW,特別適用于清潔親水表面,例如二氧化硅和氮化硅的表面,使用常規旋轉器施加到基底上。使用超聲波處理來提高懸浮粉末的均勻性。DPLW技術可在二氧化硅上產生密度在108–1010 cm-2范圍內的可再現、無損和均勻的晶種,這是以前在大面積二氧化硅或氮化硅表面上的任何晶種方法都無法實現的。

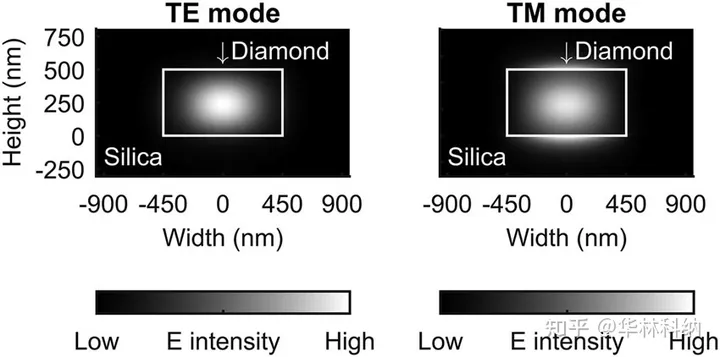

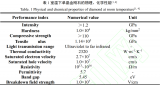

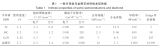

增長:多晶碳可以使用多種化學氣相沉積方法生長,包括微波等離子體化學氣相沉積、熱絲化學氣相沉積、射頻化學氣相沉積和直流電弧噴射化學氣相沉積。Ref32如表四所示。然而,MPCVD具有生產高薄膜質量、大基底尺寸、更少的污染和更好的可控性等,是應用最廣泛的電子和光學應用技術。

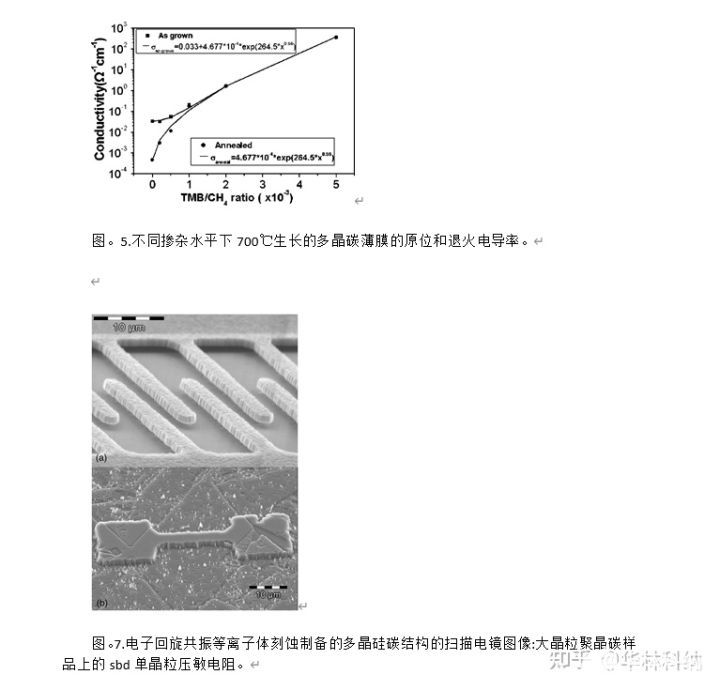

加添加劑:在氫等離子體中生長的化學氣相沉積金剛石膜具有薄的氫化表面層,其在暴露于大氣后變得導電。在600℃退火可以由于氫解吸效應去除該導電層。在本工作中,研究了多晶碳膜的硼摻雜作為TMB/甲烷氣體比、生長溫度和生長后溫度的函數。

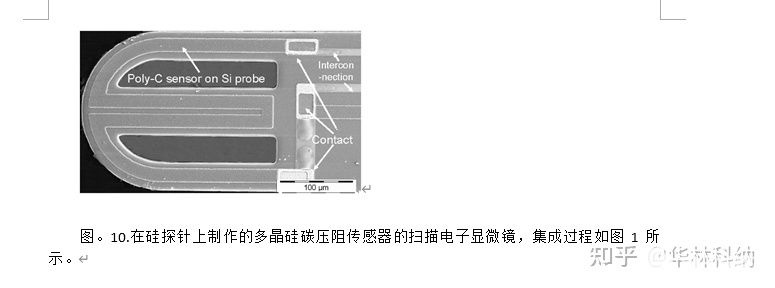

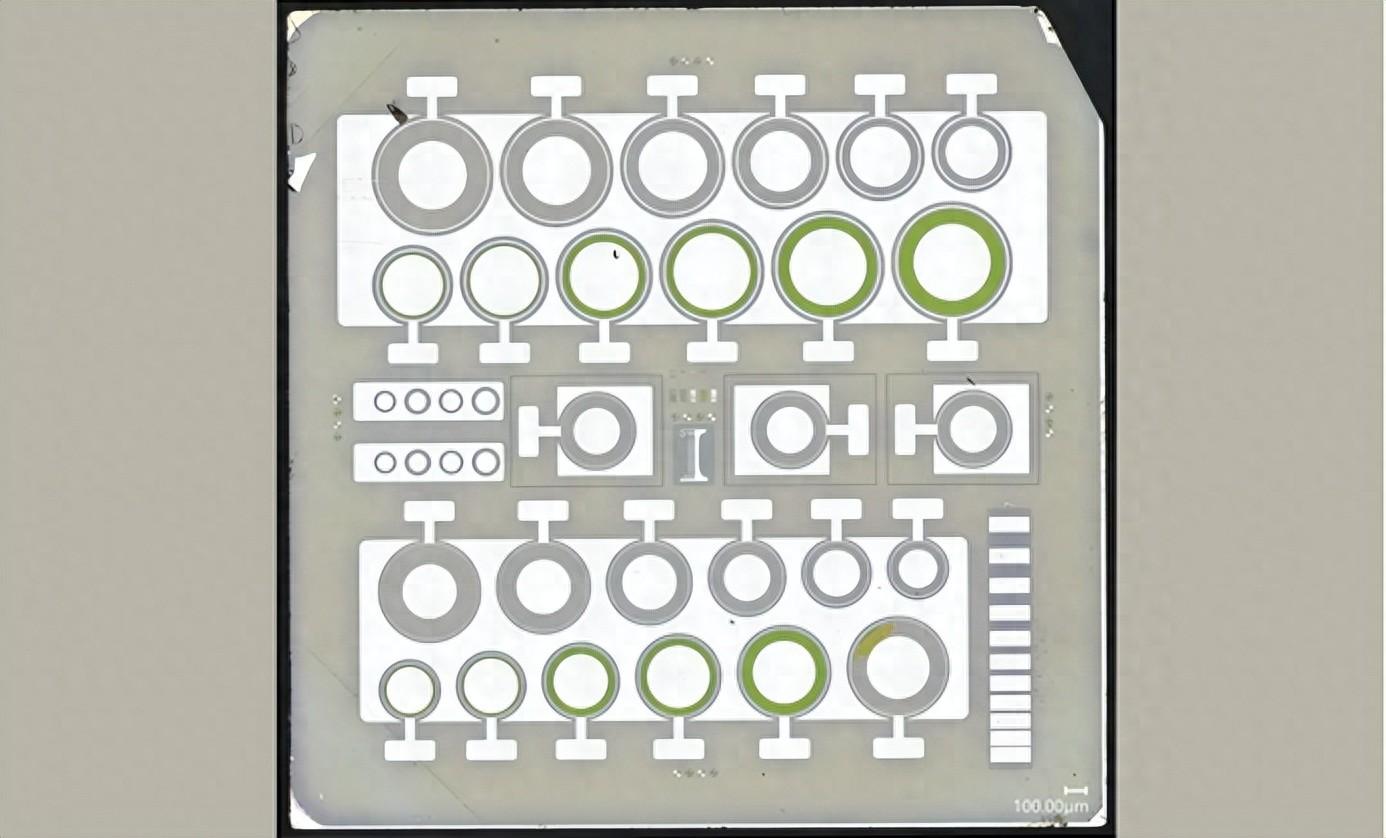

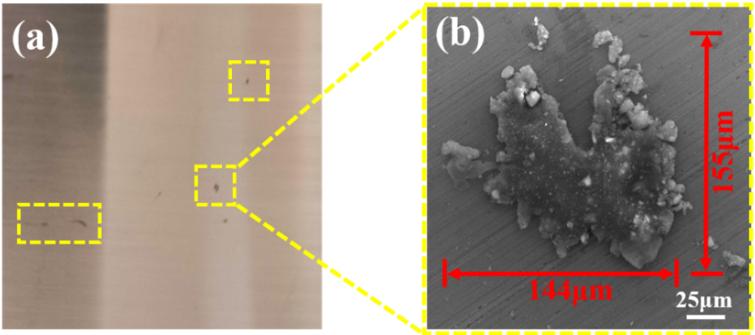

圖形:為了在大多數硅基微系統中將聚c器件集成到硅基微系統中,需要使用與典型硅處理相一致的技術來制作聚碳薄膜的圖案。由于聚c的濕式蝕刻是不可能的,唯一可用的圖案化技術是原位圖案化和干式蝕刻。原位圖案化技術依賴于選擇性播種,這種播種已經使用不同的方法實現,包括使用標準石刻的金剛石粉載光刻膠的DPRd使用二氧化硅作為掩模的選擇性播種和直接噴霧書寫。

歐姆接觸:聚碳和金屬薄膜之間的低電阻率歐姆接觸對于任何金剛石電子器件的應用都是必不可少的。多晶硅或多晶硅上的金屬接觸類型不僅取決于金屬的選擇,還取決于摻雜濃度、退火和其他參數。鈦和鉻在它們的頂部共沉積金以防止氧化,它們是最廣泛使用的金屬,因為它們能與聚碳形成碳化物并產生良好的性能退火后的電導率。

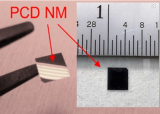

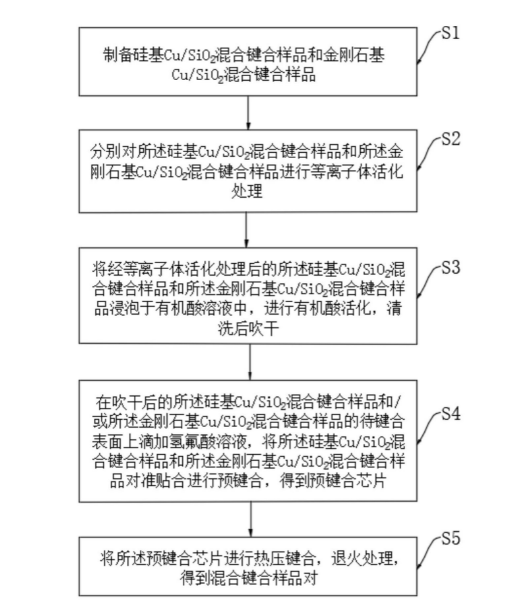

微系統過程集成:由于特殊的籽晶和生長要求,集成是限制多晶碳薄膜傳感器發展和應用的重要問題之一。集成電路中的一個常見程序是在多晶硅或金屬的上方和下方用電介質層如二氧化硅絕緣有源層,并通過接觸孔進行電連接。基于多晶碳壓阻位置傳感器的設計,我們開發了多晶碳薄膜制造工藝,如圖1所示。9將多晶碳技術集成到標準集成電路制造工藝中。該工藝使微米級的連續多晶碳膜與其上下的介電層絕緣,并通過接觸孔進行電連接,例如常見的集成電路工藝中的接觸孔。這種方法可以在金剛石生長和干蝕刻程序。多晶硅生長溫度可以在400℃和900℃之間變化,這取決于多晶硅下面使用的材料。錫含量為1%的鋁開關用作互連層,退火后可與碳多晶形成良好的歐姆接觸。圖10顯示了按照圖5所示工藝制造的碳多晶壓阻位置傳感器。在LTO沉積期間,聚碳膜被加熱到425℃20分鐘,但是所制造的位置傳感器的電導率與未構圖的膜一致。

?

結論

本文講述了在4英寸上實現了IC兼容聚c薄膜的制造工藝。利用DPLW自旋、高功率MPCVD和ECR輔助反應離子蝕刻技術進行氧化硅片。新的DPLW自旋方法可以給出4in以上的均勻播種密度為2X 1010 /cm2。晶圓片。優化后的生長表現出功率高效的大面積增長,比4英寸的厚度變化小于25%。晶圓片。微波等離子體輔助反應離子蝕刻采用六氟化硫/O2/Ar氣體,蝕刻速率為80nm/min,與4in相比的變化小于7%。區域的面積。

審核編輯:符乾江

電子發燒友App

電子發燒友App

評論