微處理器傳統(tǒng)上一直主導(dǎo)著計(jì)算領(lǐng)域,在需求更多算力的推動(dòng)下,硅基器件在密度方面不斷得到提升。按照摩爾定律,每隔兩年,晶體管密度就會(huì)翻番,這無(wú)疑是技術(shù)創(chuàng)新的金礦。在這場(chǎng)“淘金熱”中,考慮到定制硅涉及的專(zhuān)業(yè)知識(shí)和費(fèi)用,幾家大型半導(dǎo)體公司已在市場(chǎng)上斬獲了穩(wěn)固地位。現(xiàn)在,隨著對(duì)計(jì)算密集型器件需求的不斷增長(zhǎng),ASIC、FPGA?和嵌入式處理器等都被要求執(zhí)行更復(fù)雜的任務(wù)。而進(jìn)入的壁壘一直高得令人望而興嘆。

在整個(gè)產(chǎn)業(yè)鏈的終端應(yīng)用方面,系統(tǒng)的實(shí)施在很大程度上取決于利潤(rùn)。?IC?的開(kāi)發(fā)成本、專(zhuān)利許可費(fèi)和設(shè)計(jì)的便捷性都直接影響了創(chuàng)建現(xiàn)代電子產(chǎn)品的價(jià)格。設(shè)計(jì)師和開(kāi)發(fā)者一般都依賴硬件加速電路與傳統(tǒng)的嵌入式處理器來(lái)完成?和專(zhuān)用標(biāo)準(zhǔn)產(chǎn)品?(ASSP)中的核心功能,同時(shí)通用處理器眾所周知的設(shè)計(jì)流程也提供了諸多便捷與可靠性。其根本目標(biāo)是:以最低成本實(shí)現(xiàn)快速上市,同時(shí)滿足現(xiàn)代應(yīng)用日益增長(zhǎng)的復(fù)雜計(jì)算需求。那么問(wèn)題就變成了:哪種(些)芯片組合能夠以最少的開(kāi)發(fā)時(shí)間和成本,而最有效地實(shí)現(xiàn)這些應(yīng)用?

這正是?易靈思?FPGA?一顯身手的地方。?易靈思?FPGA?借助簡(jiǎn)單的軟件方法進(jìn)行軟硬件分工,將?FPGA?的固有架構(gòu)優(yōu)勢(shì)與流行的嵌入式處理器的便捷編程特性相結(jié)合。本文將介紹這種充分發(fā)揮?FPGA?潛力的新設(shè)計(jì)方法,如何使設(shè)計(jì)師能最大限度地提高系統(tǒng)設(shè)計(jì)能力和效率。

易靈思?架構(gòu)的基本優(yōu)勢(shì)

易靈思?鈦金?FPGA?在低端和高端?FPGA?之間取得平衡,是款兼具高密度、小封裝、低功耗和低價(jià)格等優(yōu)勢(shì)的器件。通過(guò)?16nm工藝技術(shù),鈦金?FPGA可以在小至?5.5?×?5.5?mm的封裝中集成了多達(dá)?100?萬(wàn)個(gè)邏輯單元?(LE)、以及大量存儲(chǔ)模塊和高速?DSP?模塊。

這是由于?易靈思?的?Quantum?計(jì)算內(nèi)核具有可重新配置的模塊,即邏輯和路由可互換的XLR單元。這消除了傳統(tǒng)布線,讓?LE?更小、使用更靈活,與傳統(tǒng)?FPGA?相比,利用率非常高。?當(dāng)需要時(shí),軟RISC-V?核可在FPGA內(nèi)核中被例化。在編譯時(shí),易靈思?的軟件會(huì)動(dòng)態(tài)選擇是將XLR?單元用作路由還是邏輯功能,以優(yōu)化其芯片資源。并且,?易靈思?FPGA?實(shí)現(xiàn)?的RISC-V?CPU?架構(gòu),不受?ARM?等專(zhuān)有?IP?內(nèi)核的約束,規(guī)避了任何專(zhuān)利許可費(fèi)用。

RISC-V?的興起

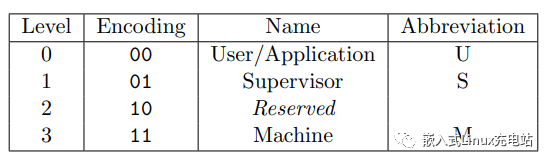

RISC-V?是一種免費(fèi)的指令集架構(gòu)(ISA),它附帶多種軟件參考設(shè)計(jì)、IP?軟核和實(shí)體器件。?RISC-V?和?ARM?之間的主要區(qū)別在于:?RISC-V?是一個(gè)開(kāi)放標(biāo)準(zhǔn),其中?ISA?沒(méi)有定義任何特定的微處理器架構(gòu);其它流行的處理器技術(shù)(如:x86、x64?和?ARM)都是基于使用供應(yīng)商提供的?ISA?和硬件架構(gòu)而付費(fèi)的商業(yè)模式。

模塊化、開(kāi)源?RISC-V?架構(gòu)的日益普及,使開(kāi)發(fā)者可以免版稅使用這些內(nèi)核并創(chuàng)建非指定供應(yīng)商的計(jì)算方案。隨著摩爾定律繼續(xù)放緩,這為創(chuàng)新打開(kāi)了大門(mén)。?RISC-V?處理核可以集成到?FPGA?中,以將便捷編程特性,與?FPGA?和?ASIC?架構(gòu)的并行處理能力和靈活性/可重配置性相結(jié)合。

采用?易靈思?FPGA?的新設(shè)計(jì)方法

易靈思?FPGA?的優(yōu)點(diǎn)并不僅限于其優(yōu)化的成本和性能。“量子加速”概念還帶來(lái)了與傳統(tǒng)嵌入式處理器相同的編程便捷性。量子加速依賴于兩種關(guān)鍵技術(shù)來(lái)簡(jiǎn)化和優(yōu)化設(shè)計(jì)流程與設(shè)計(jì)本身:

1、使用RISC-V處理器

2、使用量子加速器

借助嵌入式RISC-V軟核從RISC?ISA的便捷編程性中獲益

首先,高度可擴(kuò)展的?RISC-V?處理器被用作系統(tǒng)主力,以確保系統(tǒng)功能最大程度的在軟件中表達(dá)。使用?RISC-V?處理器的一個(gè)固有優(yōu)勢(shì)是其自定義指令,可用于擴(kuò)展處理器的功能以滿足應(yīng)用要求。這確保在使用熟悉的?C/C++?語(yǔ)言的同時(shí),以最高效率由處理器在本地執(zhí)行高度加速的任務(wù)。

因此,例如,要用C?語(yǔ)言對(duì)沒(méi)有自定義擴(kuò)展指令的的傳統(tǒng)嵌入式處理器編寫(xiě)卷積任務(wù)程序,設(shè)計(jì)師必須將其分解為幾條更簡(jiǎn)單的指令。而使用?RISC-V?自定義指令,則可以在一次執(zhí)行中完成上述任務(wù)。這些基于特定應(yīng)用的指令大大減少了標(biāo)準(zhǔn)指令所需的周期數(shù),并通過(guò)降低功耗大大提高了系統(tǒng)效率。對(duì)于人工智能算法中通常使用的卷積,使用自定義指令可將卷積加速?40至?50倍。從而顯著提高了系統(tǒng)性能。

定制指令還能讓更廣泛的產(chǎn)品組合,更快的上市。?易靈思?的一個(gè)合作伙伴創(chuàng)建了一個(gè)包含數(shù)百個(gè)自定義指令的庫(kù),這些指令可被例化并按需調(diào)用。這給他們帶來(lái)的效果是:可以在一個(gè)通用的硬件平臺(tái)上,定義、創(chuàng)建和快速交付眾多的用戶產(chǎn)品,而產(chǎn)品間的差異僅靠?RISC-V?處理器的軟件優(yōu)化就可實(shí)現(xiàn)。

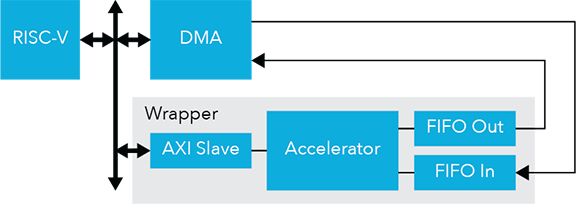

借助?FPGA?的架構(gòu)靈活性進(jìn)行直捷加速

然而,自定義指令往往適合較少量的數(shù)據(jù)處理。如果用戶希望對(duì)更大數(shù)據(jù)塊執(zhí)行數(shù)學(xué)函數(shù)運(yùn)算。量子加速器套接字(socket)定義了一個(gè)框架,使用戶能夠根據(jù)應(yīng)用的要求輕松地“指向”數(shù)據(jù)、檢索數(shù)據(jù)并編輯其內(nèi)容。此加速器套接字具有針對(duì)加速器功能、RISC-V?處理器、直接內(nèi)存訪問(wèn)(DMA)控制器和其它處理模塊的特定輸入和輸出(見(jiàn)圖)。?DMA、回調(diào)(callback)和與?RISC-V?處理器的連接都在?C?中調(diào)用,并幾乎替程序員自動(dòng)執(zhí)行。所需要的只是一點(diǎn)用于加速的VHDL代碼,而易靈思?也已經(jīng)提供了許多相關(guān)示例。

圖1

說(shuō)明:?易靈思?量子加速器套接字具有特定的輸入和輸出,使用戶能夠指向大數(shù)據(jù)塊對(duì)其檢索和編輯并進(jìn)行硬件加速。該套接字只需最小的?VHDL?設(shè)計(jì)就可以無(wú)縫地進(jìn)行后續(xù)數(shù)據(jù)移動(dòng),因此設(shè)計(jì)師可以簡(jiǎn)單地只需緊盯性能瓶頸就好。

這種方法的好處體現(xiàn)在極大地縮短了上市時(shí)間。使用這種預(yù)定義的加速建構(gòu),易靈思?的一位合作伙伴設(shè)計(jì)了一款相機(jī)系統(tǒng),包含輸入傳感器、人工智能引擎、目標(biāo)檢測(cè)和分類(lèi)、以及輸出顯示子系統(tǒng)。從項(xiàng)目啟動(dòng)到功能齊全的樣機(jī)以及量產(chǎn),整個(gè)過(guò)程才耗時(shí)一周多一點(diǎn)。

硬件加速的微方法和宏路徑

總之,易靈思?FPGA?既利用了開(kāi)放式?RISC-V?標(biāo)準(zhǔn)的固有優(yōu)勢(shì),又結(jié)合了使用定制指令或能快速修改大塊數(shù)據(jù)的定制加速器框架的長(zhǎng)處。這使電子設(shè)計(jì)公司和制造商能夠?qū)崿F(xiàn)以下目標(biāo):

通過(guò)優(yōu)化的軟件設(shè)計(jì)流程,使產(chǎn)品最快上市

通過(guò)軟件定義的架構(gòu)化靈活平臺(tái)最大限度地降低設(shè)計(jì)和生產(chǎn)成本

創(chuàng)建一個(gè)面向未來(lái)的設(shè)計(jì),既滿足現(xiàn)代應(yīng)用的計(jì)算需求,又可以通過(guò)附加功能輕松升級(jí)

易于編程的?FPGA?的價(jià)值

易靈思?把?FPGA?從傳統(tǒng)的不起眼的設(shè)計(jì)替代品轉(zhuǎn)變?yōu)樵O(shè)計(jì)必需品。這些設(shè)計(jì)技術(shù)模糊了傳統(tǒng)系統(tǒng)架構(gòu)的界限。隨著可配置、經(jīng)濟(jì)、低功耗?、具傳統(tǒng)嵌入式處理器方案速度的FPGA?的推出,借助以下方式可推動(dòng)大眾市場(chǎng)采用這些平臺(tái):

用集成的?FPGA方案完全替代?ASSP?設(shè)計(jì)

擴(kuò)展現(xiàn)有?MCU?的功能以適應(yīng)新要求和新市場(chǎng)

在保有傳統(tǒng)嵌入式處理器(例如?ARM)設(shè)計(jì)流程簡(jiǎn)單性的情況下替換嵌入式處理器

與?ASIC?等定制芯片相比,構(gòu)思和生成基于FPGA的方案所需的時(shí)間已大為縮短。?在成品足夠便宜時(shí),在適應(yīng)性強(qiáng)的?FPGA?上實(shí)現(xiàn)定制功能,是可以取代ASSP。?易靈思?嵌入式?RISC-V?處理器也可以進(jìn)行定制,以模仿和擴(kuò)展現(xiàn)有?MCU?的功能。從模仿一款熟悉的?MCU?開(kāi)始,可以在?FPGA?架構(gòu)中例化增強(qiáng)的自定義功能以及自定義加速模塊和?I/O?信號(hào)調(diào)整。

使?FPGA?成為設(shè)計(jì)要素

最重要的范式轉(zhuǎn)變?cè)谟谀軌蚶脗鹘y(tǒng)嵌入式處理器(例如?ARM)設(shè)計(jì)流程的簡(jiǎn)單性進(jìn)行快速創(chuàng)新。高度集成的?易靈思方案包含了已為人熟知的控制器架構(gòu)和高度加速的配套模塊的各種衍生品,所有這些都在同一個(gè)硅芯片中。這為?易靈思?FPGA?在邊緣計(jì)算之外——從基本的物聯(lián)網(wǎng)設(shè)備到數(shù)據(jù)中心卡——的更多樣化市場(chǎng)打開(kāi)了大門(mén)。

對(duì)于很多以往需要用到通用嵌入式處理器+強(qiáng)大的FPGA的設(shè)計(jì),設(shè)計(jì)師們現(xiàn)在可以用更簡(jiǎn)單的方式在?FPGA上實(shí)現(xiàn)。傳統(tǒng)上利用標(biāo)準(zhǔn)?CPU?或?MCU(例如物聯(lián)網(wǎng)傳感器節(jié)點(diǎn))的項(xiàng)目現(xiàn)在都可以被?FPGA?所取代,且功耗相當(dāng)(如果不是更少的話),外形小巧、成本低廉以及可以直接采用軟件設(shè)計(jì)流程。還有最大的好處是:基于?易靈思?FPGA?平臺(tái)的架構(gòu)靈活性,這些設(shè)計(jì)自來(lái)就是面向未來(lái)且可升級(jí)的。

推動(dòng)器件向高算力邁進(jìn)的設(shè)計(jì)師也可以借力?易靈思?FPGA。這使業(yè)務(wù)能夠從傳統(tǒng)的物聯(lián)網(wǎng)和寬帶用例(如家庭自動(dòng)化、機(jī)器監(jiān)控和移動(dòng)設(shè)備上的常用高清視頻流)轉(zhuǎn)向下一代應(yīng)用,如自動(dòng)駕駛汽車(chē)、無(wú)縫沉浸式現(xiàn)實(shí)體驗(yàn)(AR/VR頭戴設(shè)備)?,?等等。?易靈思?FPGA?還可以滿足這些基于邊緣、高帶寬或時(shí)間敏感的用例。企業(yè)可以通過(guò)正確的處理能力來(lái)滿足未來(lái)計(jì)算要求,從而有效地訓(xùn)練、運(yùn)行和升級(jí)各自的機(jī)器學(xué)習(xí)算法。

結(jié)論

易靈思?FPGA?可以顯著簡(jiǎn)化設(shè)計(jì)周期,立即擺脫對(duì)?ASIC?的硬件開(kāi)發(fā)要求,并簡(jiǎn)化相對(duì)CPU?和?GPU?不夠直接的硬件加速過(guò)程。?這種FPGA?產(chǎn)生了巨大影響,將?FPGA帶入了很多以往不可企及的新市場(chǎng)。?在向熟悉的軟件技術(shù)開(kāi)放硬件設(shè)計(jì)環(huán)境的過(guò)程中,易靈思?極大擴(kuò)展了可移植到?FPGA?的設(shè)計(jì)范圍,進(jìn)一步縮短了上市時(shí)間并提高了最終用戶應(yīng)用的靈活性。?由此帶來(lái)的成本和密度優(yōu)勢(shì)將使?FPGA?在市場(chǎng)上的拓展遠(yuǎn)遠(yuǎn)超出傳統(tǒng)的應(yīng)用范疇,并推動(dòng)其進(jìn)入可觸及我們生活方方面面的應(yīng)用。

審核編輯:湯梓紅

電子發(fā)燒友App

電子發(fā)燒友App

評(píng)論