臺(tái)積電計(jì)劃在嘉義科學(xué)園區(qū)投資超過(guò)5000億元新臺(tái)幣,建設(shè)六座先進(jìn)封裝廠,這一舉措無(wú)疑將對(duì)半導(dǎo)體產(chǎn)業(yè)產(chǎn)生深遠(yuǎn)影響。

2024-03-20 11:28:14 333

333 任務(wù)要求:

了解微電子封裝中的引線鍵合工藝,學(xué)習(xí)金絲引線鍵合原理,開(kāi)發(fā)引線鍵合工藝仿真方法,通過(guò)數(shù)據(jù)統(tǒng)計(jì)分析和仿真結(jié)果,分析得出引線鍵合工序關(guān)鍵工藝參數(shù)和參數(shù)窗口,并給出工藝參數(shù)和鍵合質(zhì)量之間的關(guān)系

2024-03-10 14:14:51

技術(shù)的高可靠性先進(jìn)互連工藝。通過(guò)系列質(zhì)量評(píng)估與測(cè)試方法對(duì)比分析了不同燒結(jié)工藝對(duì)芯片雙面銀燒結(jié)層和芯片剪切強(qiáng)度的影響,分析了襯板表面材料對(duì)銅線鍵合強(qiáng)度的影響,最后對(duì)試制樣品進(jìn)行溫度沖擊測(cè)試,討論了溫度沖擊對(duì)銀燒結(jié)顯微組織及

2024-03-05 08:41:47 104

104

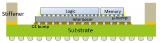

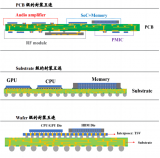

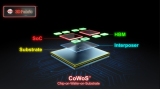

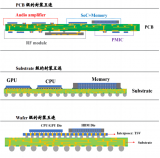

)和集成電路的飛速發(fā)展,人工智能芯片逐漸成為全球科技競(jìng)爭(zhēng)的焦點(diǎn)。在后摩爾時(shí)代,AI 芯片的算力提升和功耗降低越來(lái)越依靠具有硅通孔、微凸點(diǎn)、異構(gòu)集成、Chiplet等技術(shù)特點(diǎn)的先進(jìn)封裝技術(shù)。從 AI 芯片的分類(lèi)與特點(diǎn)出發(fā),對(duì)國(guó)內(nèi)外典型先進(jìn)封裝技術(shù)

2024-03-04 18:19:18 582

582

先進(jìn)封裝開(kāi)辟了 More-than-Moore的集成電路發(fā)展路線,能夠在不縮小制程節(jié)點(diǎn)的背景下,僅通過(guò)改進(jìn)封裝方式就能提升芯片性能,還能夠打破“存儲(chǔ)墻”和“面積墻”。

2024-02-26 11:22:10 323

323

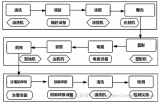

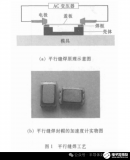

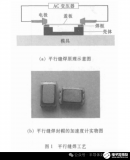

密性等。本文介紹了五種用于MEMS封裝的封帽工藝技術(shù),即平行縫焊、釬焊、激光焊接、超聲焊接和膠粘封帽。總結(jié)了不同封帽工藝的特點(diǎn)以及不同MEMS器件對(duì)封帽工藝的選擇。本文還介紹了幾種常用的吸附劑類(lèi)型,針對(duì)吸附劑易于飽和問(wèn)題,給出了封帽工藝解決方案,探

2024-02-25 08:39:28 171

171

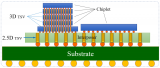

level package),2.5D封裝(interposer,RDL等),3D封裝(TSV)等先進(jìn)封裝技術(shù)。 審核編輯 黃宇

2024-02-21 10:34:20 176

176

這標(biāo)志著中國(guó)大陸在半導(dǎo)體產(chǎn)業(yè)鏈中的地位顯著提升,不僅在半導(dǎo)體晶圓制造等成熟工藝中占有一席之地,還在先進(jìn)封裝領(lǐng)域有相當(dāng)?shù)母?jìng)爭(zhēng)實(shí)力,與外資企業(yè)如日月光投控、京元電爭(zhēng)奪AI芯片必不可少的先進(jìn)封裝市場(chǎng)份額。

2024-02-20 14:48:56 448

448 此舉意味著,大陸半導(dǎo)體產(chǎn)業(yè)鏈不僅在晶圓代工成熟制程上站穩(wěn)腳跟,現(xiàn)在又在先進(jìn)封裝領(lǐng)域嶄露頭角,成功挺進(jìn)AI芯片所需的高端封裝市場(chǎng),與日月光投控、京元電等臺(tái)灣廠商展開(kāi)競(jìng)爭(zhēng)。

2024-02-20 09:26:09 126

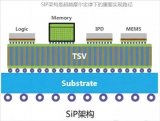

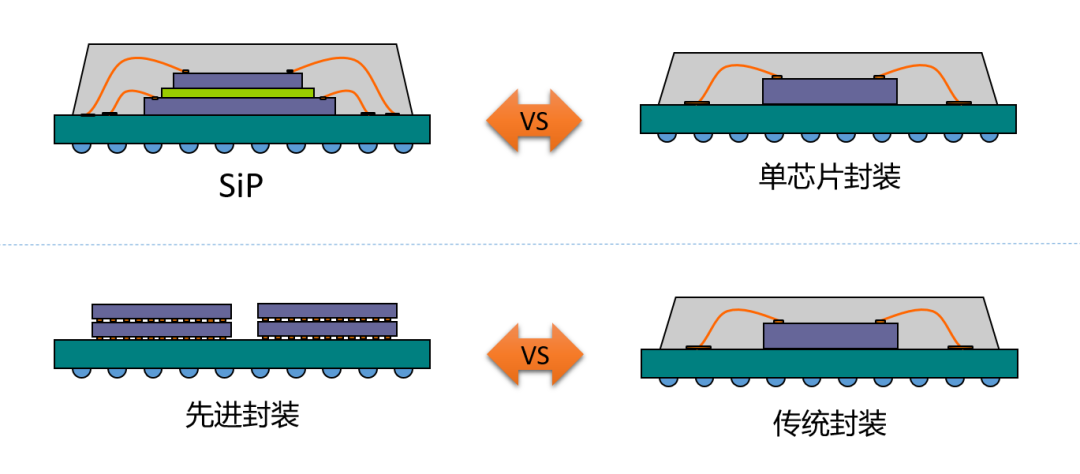

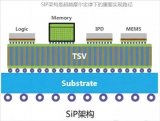

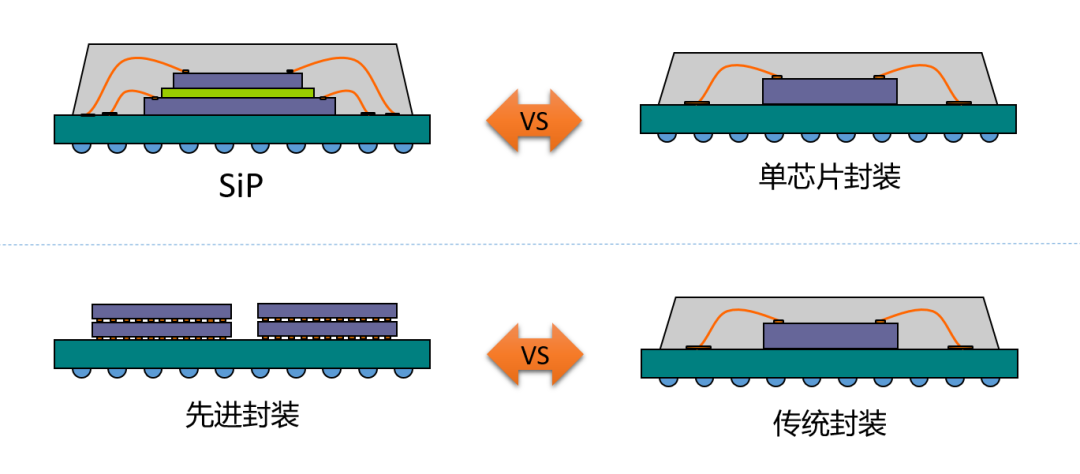

126 SiP(System in Package)技術(shù)是一種先進(jìn)的封裝技術(shù),SiP技術(shù)允許將多個(gè)集成電路(IC)或者電子組件集成到一個(gè)單一的封裝中。這種SiP封裝技術(shù)可以實(shí)現(xiàn)不同功能組件的物理集成,而這些組件可能是用不同的制造工藝制造的。

2024-02-19 15:22:19 334

334

先進(jìn)封裝產(chǎn)品通過(guò)半導(dǎo)體中道工藝實(shí)現(xiàn)芯片物理性能的優(yōu)化或者說(shuō)維持裸片性能的優(yōu)勢(shì),接下來(lái)的后道封裝從工序上而言與傳統(tǒng)封裝基本類(lèi)似。

2024-01-30 15:54:57 228

228

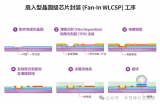

在本文中,我們將重點(diǎn)介紹半導(dǎo)體封裝的另一種主要方法——晶圓級(jí)封裝(WLP)。本文將探討晶圓級(jí)封裝的五項(xiàng)基本工藝,包括:光刻(Photolithography)工藝、濺射(Sputtering)工藝

2024-01-24 09:39:09 335

335

最近,在先進(jìn)封裝領(lǐng)域又出現(xiàn)了一個(gè)新的名詞“3.5D封裝”,以前聽(tīng)?wèi)T了2.5D和3D封裝,3.5D封裝又有什么新的特點(diǎn)呢?還是僅僅是一個(gè)吸引關(guān)注度的噱頭?

2024-01-23 16:13:29 496

496

顯微測(cè)量是利用顯微鏡對(duì)微小尺寸和形狀進(jìn)行高精度測(cè)量的技術(shù),在先進(jìn)制造業(yè)中具有重要意義。它為制造業(yè)提供了準(zhǔn)確、可靠的測(cè)量手段,幫助企業(yè)實(shí)現(xiàn)更高水平的制造和更高質(zhì)量的產(chǎn)品。隨著科技的不斷進(jìn)步,顯微測(cè)量技術(shù)有望在未來(lái)取得更大的突破和應(yīng)用。

2024-01-23 10:02:17 0

0 因?yàn)锳I芯片需求的大爆發(fā),臺(tái)積電先進(jìn)封裝產(chǎn)能供不應(yīng)求,而且產(chǎn)能供不應(yīng)求的狀況可能延續(xù)到2025年;這是臺(tái)積電總裁魏哲家在法人說(shuō)明會(huì)上透露的。 而且臺(tái)積電一直持續(xù)的擴(kuò)張先進(jìn)封裝產(chǎn)能,但是依然不能滿足AI的強(qiáng)勁需求;這在一定程度會(huì)使得其他相關(guān)封裝廠商因?yàn)榻邮苻D(zhuǎn)單而受益。

2024-01-22 18:48:08 560

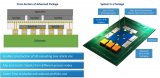

560 芯片的先進(jìn)封裝是一種超越摩爾定律的重要技術(shù),它可以提供更好的兼容性和更高的連接密度,使得系統(tǒng)集成度的提高不再局限于同一顆芯片。

2024-01-16 14:53:51 301

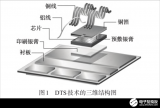

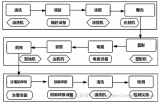

301 半導(dǎo)體器件有許多封裝形式,按封裝的外形、尺寸、結(jié)構(gòu)分類(lèi)可分為引腳插入型、表面貼裝型和高級(jí)封裝三類(lèi)。從DIP、SOP、QFP、PGA、BGA到CSP再到SIP,技術(shù)指標(biāo)一代比一代先進(jìn)。總體說(shuō)來(lái),半導(dǎo)體

2024-01-16 09:54:34 606

606

摘要:論述了傳統(tǒng)的集成電路裝片工藝面臨的挑戰(zhàn)以及現(xiàn)有用DAF膜(DieAttachmentFilm,裝片膠膜)技術(shù)進(jìn)行裝片的局限性;介紹了一種先進(jìn)的、通過(guò)噴霧結(jié)合旋轉(zhuǎn)的涂膠模式制備晶圓背面

2023-12-30 08:09:58 337

337

歡迎了解 楊彥章 鐘上彪 陳志華 (光華科學(xué)技術(shù)研究院(廣東)有限公司) 摘要 先進(jìn)封裝是半導(dǎo)體行業(yè)未來(lái)發(fā)展的重要一環(huán),是超越摩爾定律的關(guān)鍵技術(shù)。本文通過(guò)對(duì)不同封裝材料進(jìn)行表面金屬化處理,發(fā)現(xiàn)粗糙度

2023-12-28 08:45:34 119

119

LED顯示屏行業(yè)發(fā)展至今,已經(jīng)出現(xiàn)過(guò)多種生產(chǎn)封裝工藝,小間距市場(chǎng)目前以SMT貼片技術(shù)為主,在微間距市場(chǎng),COB封裝技術(shù)憑借更高像素密度,更精密的顯示效果,越來(lái)越獲得市場(chǎng)認(rèn)可。

2023-12-27 09:46:21 828

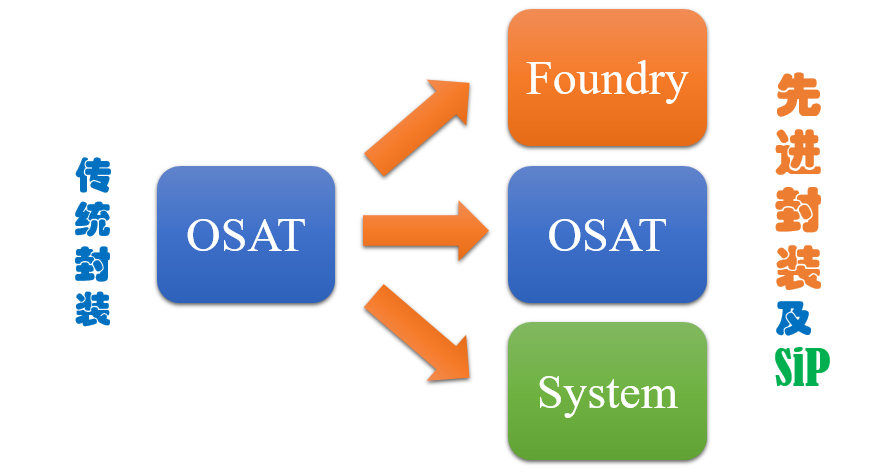

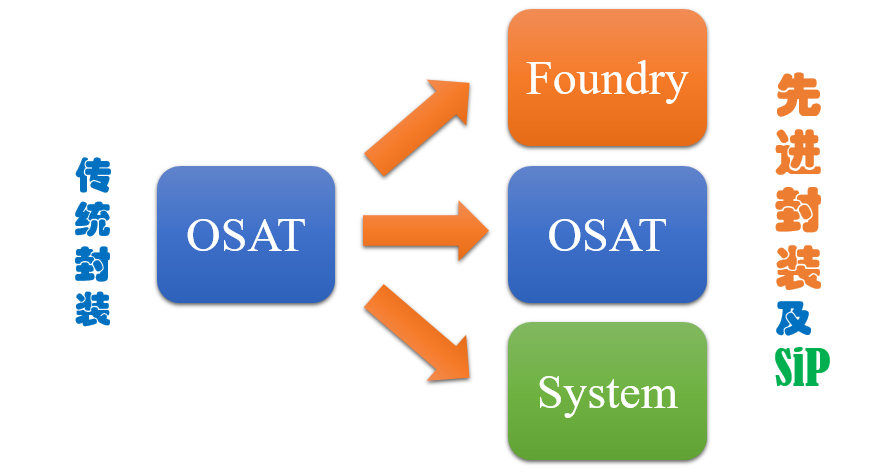

828 說(shuō)起傳統(tǒng)封裝,大家都會(huì)想到日月光ASE,安靠Amkor,長(zhǎng)電JCET,華天HT,通富微電TF等這些封裝大廠OSAT;說(shuō)起先進(jìn)封裝,當(dāng)今業(yè)界風(fēng)頭最盛的卻是臺(tái)積電TSMC,英特爾Intel,三星SAMSUNG等這些頂尖的半導(dǎo)體晶圓廠IC Foundry,這是為何呢?

2023-12-21 09:32:02 474

474

作為全球領(lǐng)先的芯片封測(cè)企業(yè),長(zhǎng)電科技深刻理解先進(jìn)的封裝設(shè)計(jì)能力對(duì)于確保半導(dǎo)體行業(yè)的產(chǎn)品性能、功能和成本至關(guān)重要。大規(guī)模高密度的集成電路為產(chǎn)品設(shè)計(jì)提供了極大的靈活性。例如Chiplet等前沿技術(shù)包含

2023-12-18 11:11:46 390

390 先進(jìn)的封裝技術(shù)可以將多個(gè)半導(dǎo)體芯片和組件集成到高性能的系統(tǒng)中。隨著摩爾定律的縮小趨勢(shì)面臨極限,先進(jìn)封裝為持續(xù)改善計(jì)算性能、節(jié)能和功能提供了一條途徑。但是,與亞洲相比,美國(guó)目前在先進(jìn)封裝技術(shù)方面落后

2023-12-14 10:27:14 383

383

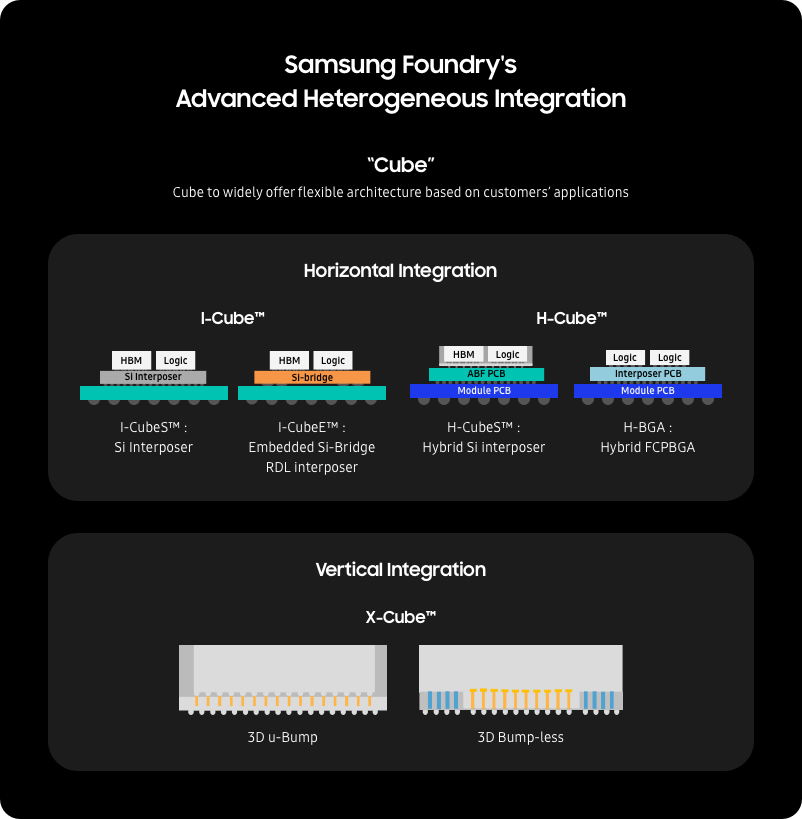

在先進(jìn)封裝領(lǐng)域,三星正積極研發(fā)HBM技術(shù),并與臺(tái)積電攜手合作,助推CoWoS工藝發(fā)展,從而擴(kuò)大HBM3產(chǎn)品的銷(xiāo)售版圖。此外,三星于2022年加入臺(tái)積電OIP 3DFabric聯(lián)盟,以期拓寬業(yè)務(wù)領(lǐng)域,為未來(lái)HBM產(chǎn)品提供解決之道。

2023-12-12 14:28:23 165

165 隨著半導(dǎo)體技術(shù)的不斷發(fā)展,封裝工藝也面臨著一系列挑戰(zhàn)。本文將探討其中一個(gè)重要的挑戰(zhàn),并提出一種化解該挑戰(zhàn)的工藝方法。

2023-12-11 14:53:37 177

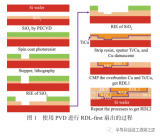

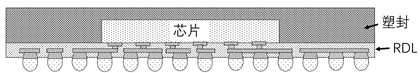

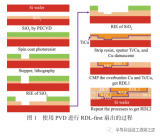

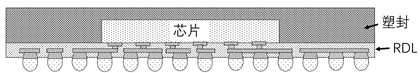

177 隨著摩爾定律逐步達(dá)到極限,大量行業(yè)巨頭暫停了 7 nm 以下工藝的研發(fā),轉(zhuǎn)而將目光投向先進(jìn)封裝領(lǐng)域。其中再布線先行( RDL-first ) 工藝作為先進(jìn)封裝技術(shù)的重要組成部分,因其具備

2023-12-07 11:33:44 723

723

半導(dǎo)體芯片封裝的目的無(wú)非是要起到對(duì)芯片本身的保護(hù)作用和實(shí)現(xiàn)芯片之間的信號(hào)互聯(lián)。在過(guò)去的很長(zhǎng)時(shí)間段里,芯片性能的提升主要是依靠設(shè)計(jì)以及制造工藝的提升。

2023-12-06 10:22:54 505

505

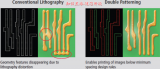

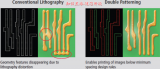

DPT Double Patterning Technology。double pattern就是先進(jìn)工藝下底層金屬/poly加工制造的一種技術(shù),先進(jìn)工藝下,如果用DUV,光的波長(zhǎng)已經(jīng)無(wú)法直接刻出

2023-12-01 10:20:03 596

596

隨著晶圓級(jí)封裝技術(shù)的不斷提升,眾多芯片設(shè)計(jì)及封測(cè)公司開(kāi)始思考并嘗試采用晶圓級(jí)封裝技術(shù)替代傳統(tǒng)封裝。其中HRP(Heat?Re-distribution?Packaging)晶圓級(jí)先進(jìn)封裝工藝技術(shù)

2023-11-30 09:23:24 1120

1120

相比于晶圓制造,中國(guó)大陸封測(cè)環(huán)節(jié)較為成熟,占據(jù)全球封測(cè)接近40%的份額,但中國(guó)大陸先進(jìn)封裝的滲透率較低,2022年僅為14%,低于全球45%的滲透率。在制程工藝受到外部制裁的背景下

2023-11-25 15:44:25 739

739 合封芯片工藝是一種先進(jìn)的芯片封裝技術(shù),將多個(gè)芯片或不同的功能的電子模塊封裝在一起,從而形成一個(gè)系統(tǒng)或子系統(tǒng)。合封芯片更容易實(shí)現(xiàn)更復(fù)雜、更高效的任務(wù)。本文將從合封芯片工藝的工作原理、應(yīng)用場(chǎng)景、技術(shù)要點(diǎn)等方面進(jìn)行深入解讀。

2023-11-24 17:36:32 332

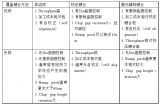

332 先進(jìn)封裝基本術(shù)語(yǔ)

2023-11-24 14:53:10 362

362

我們?yōu)槭裁葱枰私庖恍?b class="flag-6" style="color: red">先進(jìn)封裝?

2023-11-23 16:32:06 281

281

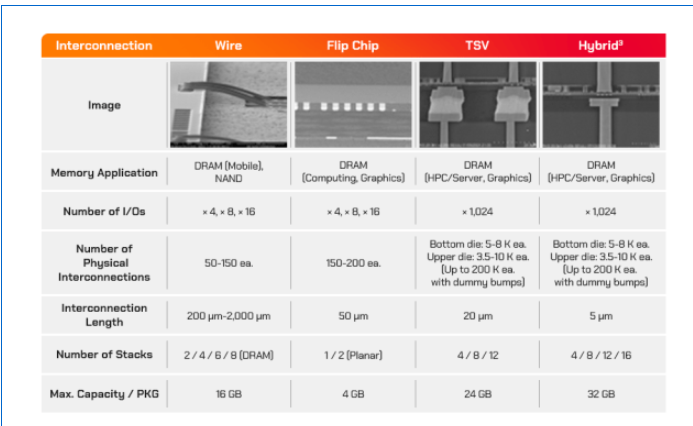

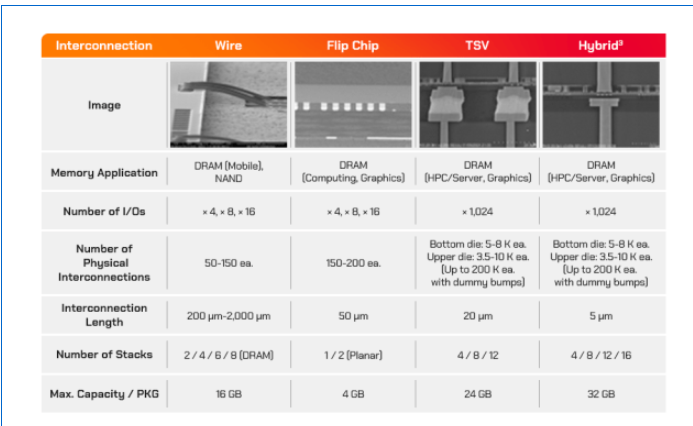

互連技術(shù)是封裝的關(guān)鍵和必要部分。芯片通過(guò)封裝互連,以接收功率、交換信號(hào)并最終進(jìn)行操作。由于半導(dǎo)體產(chǎn)品的速度、密度和功能隨互連方式的不同而不同,互連方法也在不斷變化和發(fā)展。

2023-11-23 15:13:58 181

181

這一計(jì)劃被命名為國(guó)家先進(jìn)封裝制造計(jì)劃 (NAPMP),將投資30億美元用于項(xiàng)目,其中包括用于向美國(guó)制造商驗(yàn)證和過(guò)渡新技術(shù)的先進(jìn)封裝試點(diǎn)設(shè)施、確保新工藝和工具配備有能力的員工培訓(xùn)計(jì)劃以及項(xiàng)目資金。該部門(mén)預(yù)計(jì)將于2024年宣布 NAPMP 的第一個(gè)資助機(jī)會(huì)(針對(duì)材料和基材)。

2023-11-22 15:51:44 363

363 IGBT模塊的封裝技術(shù)難度高,高可靠性設(shè)計(jì)和封裝工藝控制是其技術(shù)難點(diǎn)。

2023-11-21 15:49:45 673

673

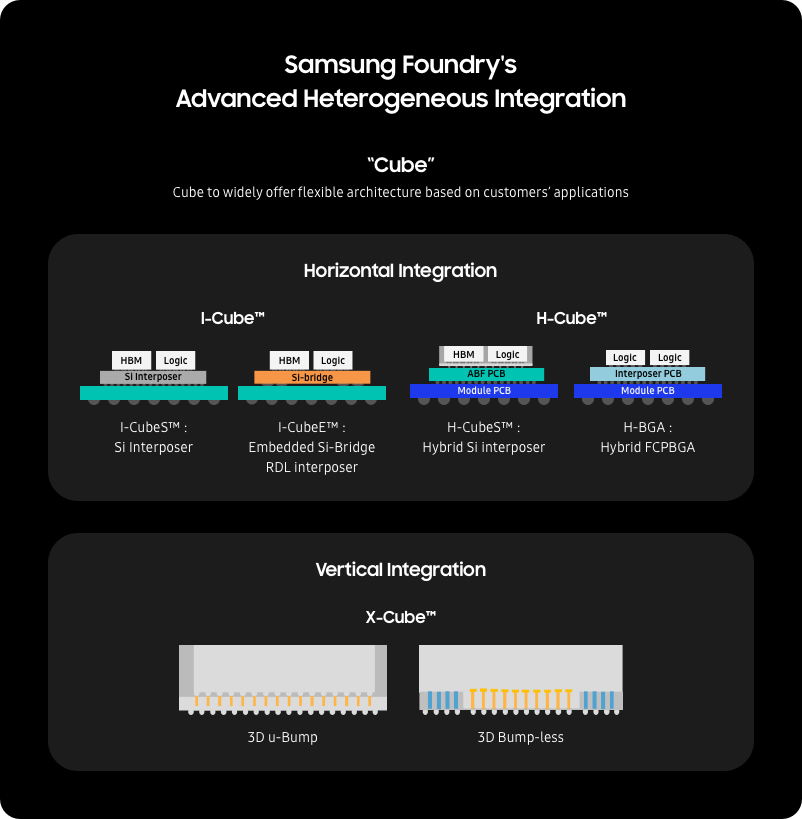

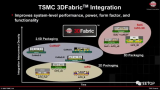

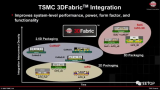

,絕大多數(shù)廠商會(huì)選擇異構(gòu)集成的方式,借助先進(jìn)封裝技術(shù)實(shí)現(xiàn)“超越摩爾”。諸如臺(tái)積電、英特爾等廠商,也都紛紛推出了3DFabric、Foveros之類(lèi)的技術(shù),而三星也不甘落后,一并追求突破半導(dǎo)體技術(shù)的極限。 ? 為了進(jìn)一步發(fā)揮其先進(jìn)封裝技術(shù)

2023-11-21 00:13:00 1155

1155

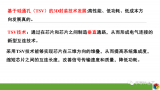

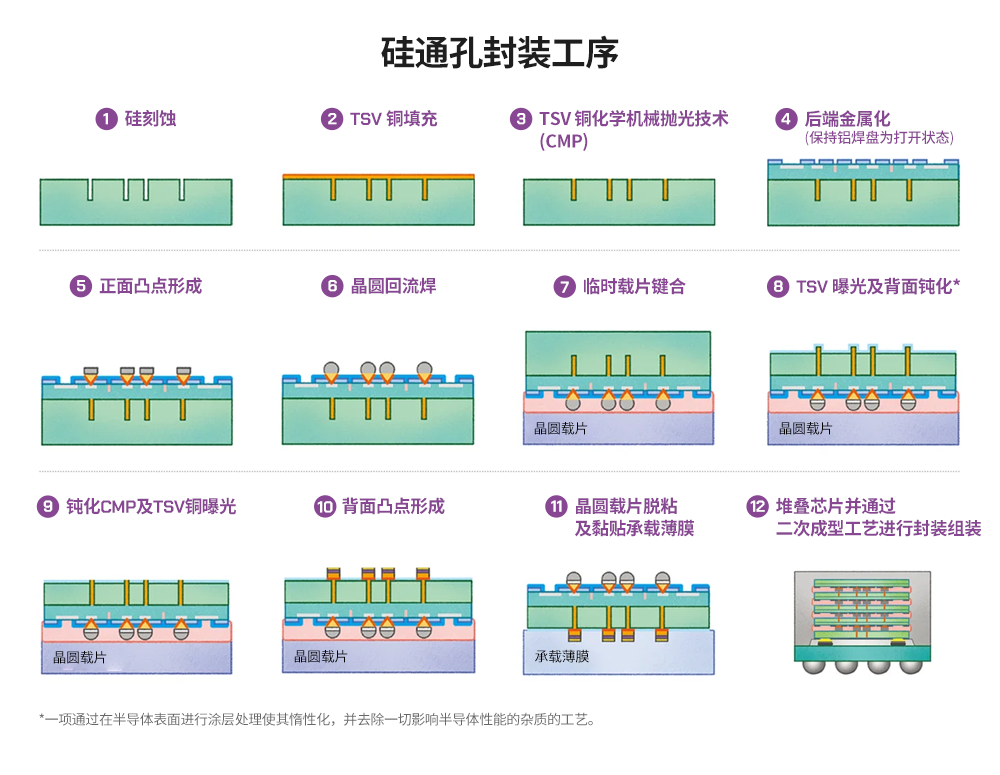

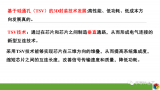

硅通孔(TVS)技術(shù)相關(guān)知識(shí)

2023-11-20 11:15:46 308

308

近年來(lái),隨著晶圓級(jí)封裝技術(shù)的不斷提升,眾多芯片設(shè)計(jì)及封測(cè)公司開(kāi)始思考并嘗試采用晶圓級(jí)封裝技術(shù)替代傳統(tǒng)封裝。其中HRP(Heat Re-distribution Packaging)晶圓級(jí)先進(jìn)封裝工藝技術(shù)

2023-11-18 15:26:58 0

0 三星計(jì)劃在2024年先進(jìn)3D芯片封裝技術(shù)SAINT(Samsung Advanced Interconnection Technology,三星高級(jí)互連技術(shù)),能以更小尺寸的封裝,將AI芯片等高性能芯片的內(nèi)存和處理器集成。

2023-11-15 11:09:30 932

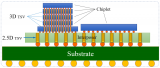

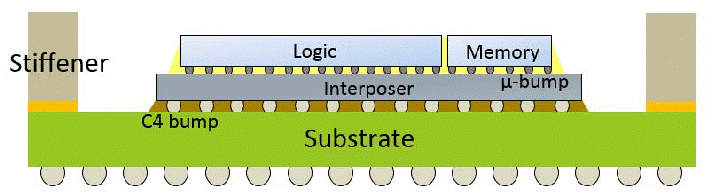

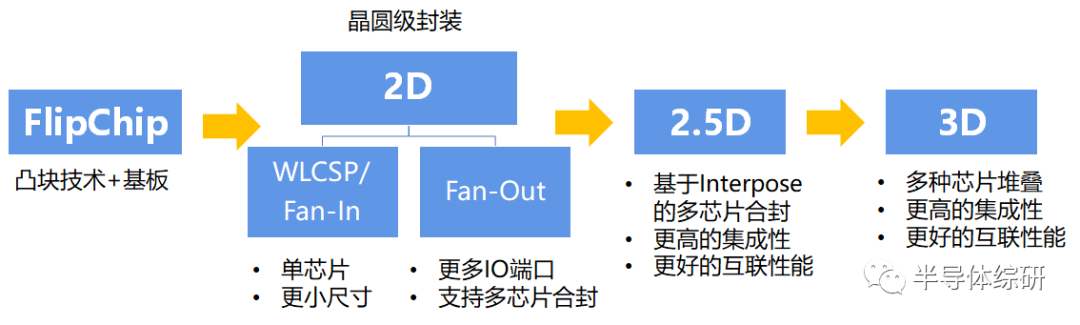

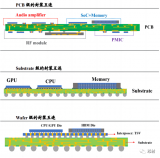

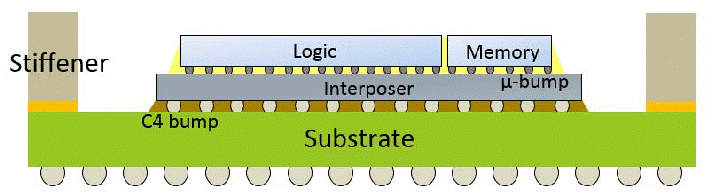

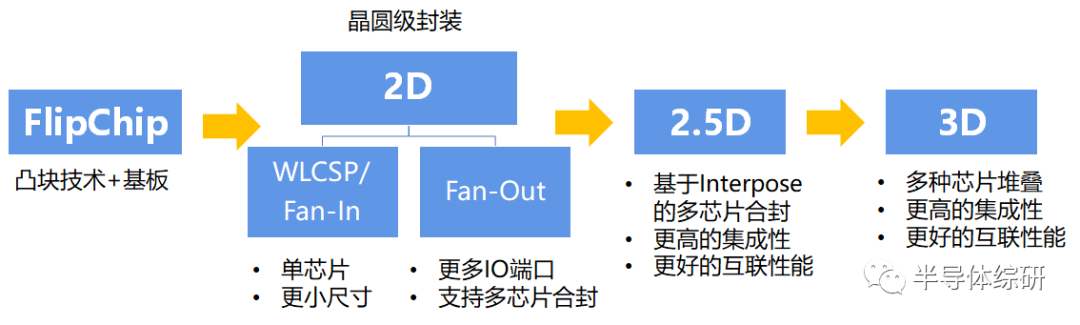

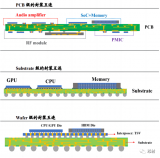

932 半導(dǎo)體產(chǎn)品在由二維向三維發(fā)展,從技術(shù)發(fā)展方向半導(dǎo)體產(chǎn)品出現(xiàn)了系統(tǒng)級(jí)封裝(SiP)等新的封裝方式,從技術(shù)實(shí)現(xiàn)方法出現(xiàn)了倒裝(FlipChip),凸塊(Bumping),晶圓級(jí)封裝(Waferlevelpackage),2.5D封裝(interposer,RDL等),3D封裝(TSV)等先進(jìn)封裝技術(shù)。

2023-10-31 09:16:29 836

836

扇出型晶圓級(jí)封裝技術(shù)的優(yōu)勢(shì)在于能夠利用高密度布線制造工藝,形成功率損耗更低、功能性更強(qiáng)的芯片封裝結(jié)構(gòu),讓系統(tǒng)級(jí)封裝(System in a Package, SiP)和3D芯片封裝更愿意采用扇出型晶圓級(jí)封裝工藝。

2023-10-25 15:16:14 314

314

隨著半導(dǎo)體工藝的不斷發(fā)展,先進(jìn)封裝技術(shù)正在迅速發(fā)展,封裝設(shè)備市場(chǎng)也將迎來(lái)新的發(fā)展機(jī)遇。作為先進(jìn)封裝設(shè)備中的關(guān)鍵設(shè)備之一,劃片機(jī)的發(fā)展也備受關(guān)注。劃片機(jī)是用于切割晶圓或芯片的設(shè)備,其精度和穩(wěn)定性

2023-10-18 17:03:28 494

494

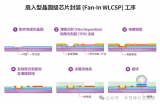

晶圓級(jí)封裝是指晶圓切割前的工藝。晶圓級(jí)封裝分為扇入型晶圓級(jí)芯片封裝(Fan-In WLCSP)和扇出型晶圓級(jí)芯片封裝(Fan-Out WLCSP),其特點(diǎn)是在整個(gè)封裝過(guò)程中,晶圓始終保持完整。

2023-10-18 09:31:05 1339

1339

電子發(fā)燒友網(wǎng)報(bào)道(文/李寧遠(yuǎn))先進(jìn)芯片封裝的發(fā)展不可謂不快,根據(jù)Yole統(tǒng)計(jì)數(shù)據(jù),2021年到2027年先進(jìn)封裝占比不斷攀升,其中2.5D/3D先進(jìn)封裝市場(chǎng)收入規(guī)模年復(fù)合增長(zhǎng)率最高,在先進(jìn)封裝多個(gè)

2023-10-17 09:05:07 1000

1000 此時(shí)先進(jìn)封裝開(kāi)始嶄露頭角,以蘋(píng)果和臺(tái)積電為代表,開(kāi)啟了一場(chǎng)新的革命,其主要分為兩大類(lèi),一種是基于XY平面延伸的先進(jìn)封裝技術(shù),主要通過(guò)RDL進(jìn)行信號(hào)的延伸和互連;第二種則是基于Z軸延伸的先進(jìn)封裝技術(shù),主要通過(guò)TSV進(jìn)行信號(hào)延伸和互連。

2023-10-10 17:04:30 573

573

半導(dǎo)體封裝技術(shù)的發(fā)展一直都是電子行業(yè)持續(xù)創(chuàng)新的重要驅(qū)動(dòng)力。隨著集成電路技術(shù)的發(fā)展,半導(dǎo)體封裝技術(shù)也經(jīng)歷了從基礎(chǔ)的封裝到高密度、高性能的封裝的演變。本文將介紹半導(dǎo)體封裝工藝的四個(gè)等級(jí),以助讀者更好地理解這一關(guān)鍵技術(shù)。

2023-10-09 09:31:55 933

933

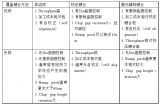

先進(jìn)封裝技術(shù)以SiP、WLP、2.5D/3D為三大發(fā)展重點(diǎn)。先進(jìn)封裝核心技術(shù)包括Bumping凸點(diǎn)、RDL重布線、硅中介層和TSV通孔等,依托這些技術(shù)的組合各廠商發(fā)展出了滿足多樣化需求的封裝解決方案,SiP系統(tǒng)級(jí)封裝、WLP晶圓級(jí)封裝、2.5D/3D封裝為三大發(fā)展重點(diǎn)。

2023-09-28 15:29:37 1613

1613

先進(jìn)封裝增速高于整體封裝,將成為全球封裝市場(chǎng)主要增量。根據(jù)Yole的數(shù)據(jù),全球封裝市場(chǎng)規(guī)模穩(wěn)步增長(zhǎng),2021 年全球封裝 市場(chǎng)規(guī)模 約達(dá) 777 億美元。其中,先進(jìn)封裝全球市場(chǎng)規(guī)模約 350 億美元,占比約 45%, 2025 年,先進(jìn)封裝在全部封裝市場(chǎng)的 占比將增長(zhǎng)至 49.4%。

2023-09-22 10:43:18 1189

1189

來(lái)源:ACT半導(dǎo)體芯科技 2023年8月31日 “先進(jìn)封裝技術(shù)之設(shè)計(jì)·材料·工藝新發(fā)展” 在線主題會(huì)議已圓滿結(jié)束! 會(huì)議當(dāng)天,演講嘉賓們的精彩分享 引得在線聽(tīng)眾踴躍提問(wèn) 由于時(shí)間原因 很多問(wèn)題都嘉賓

2023-09-08 15:40:38 210

210

英特爾聯(lián)合創(chuàng)始人戈登摩爾曾預(yù)言,芯片上的晶體管數(shù)量每隔一到兩年就會(huì)增加一倍。由于圖案微型化技術(shù)的發(fā)展,這一預(yù)測(cè)被稱為摩爾定律,直到最近才得以實(shí)現(xiàn)。

2023-09-07 09:19:38 229

229

? 半導(dǎo)體器件有許多封裝形式,按封裝的外形、尺寸、結(jié)構(gòu)分類(lèi)可分為引腳插入型、表面貼裝型和高級(jí)封裝三類(lèi)。從DIP、SOP、QFP、PGA、BGA到CSP再到SIP,技術(shù)指標(biāo)一代比一代先進(jìn)。總體說(shuō)來(lái)

2023-08-28 09:37:11 1072

1072

來(lái)源:ACT半導(dǎo)體芯科技 隨著中國(guó)半導(dǎo)體產(chǎn)業(yè)的不斷升級(jí),國(guó)內(nèi)的傳統(tǒng)封裝工藝繼續(xù)保持優(yōu)勢(shì),同時(shí)先進(jìn)封裝技術(shù)在下游應(yīng)用需求驅(qū)動(dòng)下快速發(fā)展。特別是超算、物聯(lián)網(wǎng)、智能終端產(chǎn)品等對(duì)芯片體積和功耗的苛求,這些

2023-08-25 17:06:10 299

299

來(lái)源:ACT半導(dǎo)體芯科技 隨著中國(guó)半導(dǎo)體產(chǎn)業(yè)的不斷升級(jí),國(guó)內(nèi)的傳統(tǒng)封裝工藝繼續(xù)保持優(yōu)勢(shì),同時(shí)先進(jìn)封裝技術(shù)在下游應(yīng)用需求驅(qū)動(dòng)下快速發(fā)展。特別是超算、物聯(lián)網(wǎng)、智能終端產(chǎn)品等對(duì)芯片體積和功耗的苛求,這些

2023-08-18 17:57:49 775

775

(Waferlevelpackage),2.5D封裝(interposer,RDL等),3D封裝(TSV)等先進(jìn)封裝技術(shù)。免責(zé)聲明:本文轉(zhuǎn)自網(wǎng)絡(luò),版權(quán)歸原作者所有,如涉及作品版權(quán)問(wèn)題,

2023-08-14 09:59:24 457

457

半導(dǎo)體器件有許多封裝形式,按封裝的外形、尺寸、結(jié)構(gòu)分類(lèi)可分為引腳插入型、表面貼裝型和高級(jí)封裝三類(lèi)。從DIP、SOP、QFP、PGA、BGA到CSP再到SIP,技術(shù)指標(biāo)一代比一代先進(jìn)。

2023-08-14 09:59:17 1086

1086

半導(dǎo)體器件有許多封裝形式,按封裝的外形、尺寸、結(jié)構(gòu)分類(lèi)可分為引腳插入型、表面貼裝型和高級(jí)封裝三類(lèi)。從DIP、SOP、QFP、PGA、BGA到CSP再到SIP,技術(shù)指標(biāo)一代比一代先進(jìn)。

2023-08-11 09:43:43 1796

1796

先進(jìn)封裝處于晶圓制造與封測(cè)制程中的交叉區(qū)域,涉及IDM、晶圓代工、封測(cè)廠商,市場(chǎng)格局較為集中,前6 大廠商份額合計(jì)超過(guò)80%。全球主要的 6 家廠商,包括 2 家 IDM 廠商(英特爾、三星),一家

2023-08-11 09:11:48 456

456

先進(jìn)封裝處于晶圓制造與封測(cè)的交叉區(qū)域 先進(jìn)封裝處于晶圓制造與封測(cè)制程中的交叉區(qū)域,涉及IDM、晶圓代工、封測(cè)廠商。先進(jìn)封裝要求在晶圓劃片前融入封裝工藝步驟,具體包括應(yīng)用晶圓研磨薄化、重布線(RDL

2023-08-07 10:59:46 852

852

level package),2.5D封裝(interposer,RDL等),3D封裝(TSV)等先進(jìn)封裝技術(shù)。

2023-08-05 09:54:29 398

398

據(jù)lexisnexis介紹,臺(tái)積電擁有2946項(xiàng)尖端包裝專(zhuān)利,這是其他公司引用的專(zhuān)利數(shù)量中最高的。專(zhuān)利件數(shù)和質(zhì)量排在第二位的三星電子為2404件。英特爾在先進(jìn)封裝產(chǎn)品有價(jià)證券組合中擁有1434項(xiàng)專(zhuān)利,位居第三。

2023-08-02 10:43:30 966

966 隨著chatGPT橫空出世,生成式AI紅遍全球,帶動(dòng)AI芯片的需求強(qiáng)勁,英偉達(dá)(NVIDIA)的H100、A100全部由臺(tái)積電代工,并使用臺(tái)積電的CoWoS先進(jìn)封裝技術(shù),除了英偉達(dá)外,AMD MI300也導(dǎo)入CoWoS技術(shù),造成CoWoS產(chǎn)能供不應(yīng)求。

2023-07-31 12:49:24 2214

2214 在半導(dǎo)體產(chǎn)業(yè)中,芯片設(shè)計(jì)和制造始終是核心環(huán)節(jié),但隨著技術(shù)的進(jìn)步,封裝技術(shù)也日益受到重視。先進(jìn)封裝不僅能保護(hù)芯片,還能提高其性能、效率和可靠性。本文將探討先進(jìn)封裝的四大要素及其作用。

2023-07-27 10:25:50 1048

1048

電動(dòng)機(jī)的技術(shù)經(jīng)濟(jì)指標(biāo)在很大程度上與其制造材料、制造工藝有關(guān)。在電動(dòng)機(jī)制造廠中,同樣的設(shè)計(jì)結(jié)構(gòu),同一批原材料所制成的產(chǎn)品,其質(zhì)量往往相差甚大。沒(méi)有先進(jìn)的制造工藝技術(shù),很難生產(chǎn)出先進(jìn)的產(chǎn)品。今天我們來(lái)看看電機(jī)制造中的那些關(guān)鍵工藝。

2023-07-21 17:19:25 694

694

論文在III-B部分描述了論文方法背后的SLAM管道。論文的2D潛在先驗(yàn)網(wǎng)絡(luò)(LPN)在III-C中描述。LPN輸出融合到論文在III-D中描述的論文新穎的準(zhǔn)平面超分段(QPOS)方法分割的地圖

2023-07-19 15:55:21 274

274

封測(cè)行業(yè)能否提升產(chǎn)業(yè)價(jià)值、取得重大突破的關(guān)鍵。從長(zhǎng)期來(lái)看,國(guó)內(nèi)半導(dǎo)體產(chǎn)業(yè)正處于快速發(fā)展期,芯片設(shè)計(jì)公司和晶圓代工廠的增加將帶動(dòng)本地封測(cè)需求。先進(jìn)芯片堆疊、互連技術(shù)成為先進(jìn)封裝核心工藝,為Chiplet發(fā)展提供技術(shù)基礎(chǔ);5

2023-07-17 20:04:55 320

320

Chiplet技術(shù)是一種利用先進(jìn)封裝方法將不同工藝/功能的芯片進(jìn)行異質(zhì)集成的技術(shù)。這種技術(shù)設(shè)計(jì)的核心思想是先分后合,即先將單芯片中的功能塊拆分出來(lái),再通過(guò)先進(jìn)封裝模塊將其集成為大的單芯片。

2023-07-17 09:21:50 2308

2308

先進(jìn)封裝是“超越摩爾”(More than Moore)時(shí)代的一大技術(shù)亮點(diǎn)。當(dāng)芯片在每個(gè)工藝節(jié)點(diǎn)上的微縮越來(lái)越困難、也越來(lái)越昂貴之際,工程師們將多個(gè)芯片放入先進(jìn)的封裝中,就不必再費(fèi)力縮小芯片了。本文將對(duì)先進(jìn)封裝技術(shù)中最常見(jiàn)的10個(gè)術(shù)語(yǔ)進(jìn)行簡(jiǎn)單介紹。

2023-07-12 10:48:03 625

625

1. 先進(jìn)制程受限,先進(jìn)封裝/Chiplet提升算力,必有取舍。

2023-07-07 09:42:04 1692

1692

對(duì)于MiniLED和MicroLED的封裝技術(shù),除了之前提到的COB、coG、coF、IMD和MiP工藝,還有一些新的封裝技術(shù),例如:0CRL(Oxide-BufferedCuInGaZn/Quar

2023-07-06 16:00:52 401

401

隨著異構(gòu)集成模塊功能和特征尺寸的不斷增加,三維集成技術(shù)應(yīng)運(yùn)而生。凸點(diǎn)之間的互連 是實(shí)現(xiàn)芯片三維疊層的關(guān)鍵,制備出高可靠性的微凸點(diǎn)對(duì)微電子封裝技術(shù)的進(jìn)一步發(fā)展具有重要意 義。整理歸納了先進(jìn)封裝

2023-07-06 09:56:16 1150

1150

AI訂單激增,影響傳至先進(jìn)封裝市場(chǎng)。

2023-07-05 18:19:37 774

774

在異質(zhì)異構(gòu)的世界里,chiplet是“生產(chǎn)關(guān)系”,是決定如何拆分及組合芯粒的方式與規(guī)則;先進(jìn)封裝技術(shù)是“生產(chǎn)力”,通過(guò)堆疊、拼接等方法實(shí)現(xiàn)不同芯粒的互連。先進(jìn)封裝技術(shù)已成為實(shí)現(xiàn)異質(zhì)異構(gòu)的重要前提。

2023-06-26 17:14:57 600

600 Chiplet俗稱“芯粒”或“小芯片組”,通過(guò)將原來(lái)集成于同一 SoC 中的各個(gè)元件分拆,獨(dú)立 為多個(gè)具特定功能的 Chiplet,分開(kāi)制造后再通過(guò)先進(jìn)封裝技術(shù)將彼此互聯(lián),最終集成封裝 為一個(gè)系統(tǒng)芯片。

2023-06-25 15:12:20 1342

1342

Brewer Science, Inc. 和 PulseForge, Inc. 通過(guò)對(duì)半導(dǎo)體先進(jìn)封裝進(jìn)行光子解鍵合(Photonic debonding),帶來(lái)了顯著的成本節(jié)約、更高的產(chǎn)量和其他優(yōu)勢(shì)。此次合作將制造下一代材料和工藝的全球領(lǐng)導(dǎo)者與獨(dú)特的技術(shù)提供商結(jié)合在一起。

2023-06-25 14:12:44 364

364 先進(jìn)的半導(dǎo)體封裝既不是常規(guī)操作,目前成本也是相當(dāng)高的。但如果可以實(shí)現(xiàn)規(guī)模化,那么該行業(yè)可能會(huì)觸發(fā)一場(chǎng)chiplet革命,使IP供應(yīng)商可以銷(xiāo)售芯片,顛覆半導(dǎo)體供應(yīng)鏈。

2023-06-21 08:56:39 190

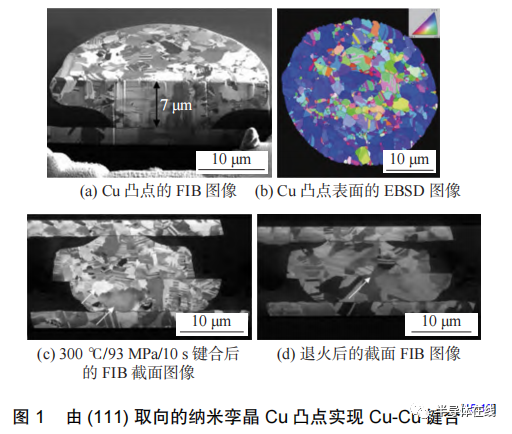

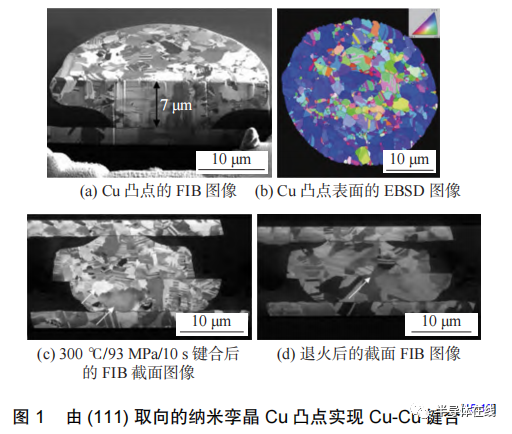

190 Cu-Cu 低溫鍵合技術(shù)是先進(jìn)封裝的核心技術(shù),相較于目前主流應(yīng)用的 Sn 基軟釬焊工藝,其互連節(jié)距更窄、導(dǎo) 電導(dǎo)熱能力更強(qiáng)、可靠性更優(yōu). 文中對(duì)應(yīng)用于先進(jìn)封裝領(lǐng)域的 Cu-Cu 低溫鍵合技術(shù)進(jìn)行了

2023-06-20 10:58:48 1545

1545

Fab 6 是臺(tái)積電首個(gè)一體式先進(jìn)封裝測(cè)試工廠,是臺(tái)積電不斷增加的封裝投資的一部分。該晶圓廠已準(zhǔn)備好量產(chǎn)臺(tái)積電 SoIC 封裝技術(shù)。請(qǐng)記住,當(dāng)臺(tái)積電說(shuō)量產(chǎn)時(shí),他們指的是 Apple iPhone 尺寸的量產(chǎn),而不是工程樣品或內(nèi)部產(chǎn)品。

2023-06-19 11:25:56 219

219

隨著摩爾定律的放緩以及前沿節(jié)點(diǎn)復(fù)雜性和成本的增加,先進(jìn)封裝正在成為將多個(gè)裸片集成到單個(gè)封裝中的關(guān)鍵解決方案,并有可能結(jié)合成熟和先進(jìn)的節(jié)點(diǎn)。

2023-06-16 17:50:09 340

340

一、核心結(jié)論 ?1、先進(jìn)制程受限,先進(jìn)封裝/Chiplet提升算力,必有取舍。在技術(shù)可獲得的前提下,提升芯片性能,先進(jìn)制程升級(jí)是首選,先進(jìn)封裝則錦上添花。 2、大功耗、高算力的場(chǎng)景,先進(jìn)封裝

2023-06-13 11:38:05 747

747

先進(jìn)封裝是對(duì)應(yīng)于先進(jìn)圓晶制程而衍生出來(lái)的概念,一般指將不同系統(tǒng)集成到同一封裝內(nèi)以實(shí)現(xiàn)更高效系統(tǒng)效率的封裝技術(shù)。

2023-06-13 11:33:24 282

282

我國(guó)大大小小的封測(cè)廠超過(guò)千家,除了頭部幾家企業(yè)外,大部分都處于同質(zhì)化競(jìng)爭(zhēng),研發(fā)投入較少,利潤(rùn)率低,受市場(chǎng)波動(dòng)影響較大。近年,隨著臺(tái)積電、英特爾、三星等巨頭不斷在先進(jìn)封裝領(lǐng)域的投入,封裝的工藝向晶圓工藝靠近,復(fù)雜度變得越高,封裝的利潤(rùn)率也必將隨之而增加。

2023-06-08 14:22:56 4281

4281

隨著晶圓代工制程不斷縮小,摩爾定律逼近極限,先進(jìn)封裝是后摩爾時(shí)代的必然選擇。其中,利用高端封裝融合最新和成熟節(jié)點(diǎn),采用系統(tǒng)封裝(SiP)和基于小芯片的方法,設(shè)計(jì)和制造最新的SoC產(chǎn)品已經(jīng)成為

2023-05-23 12:29:11 2874

2874

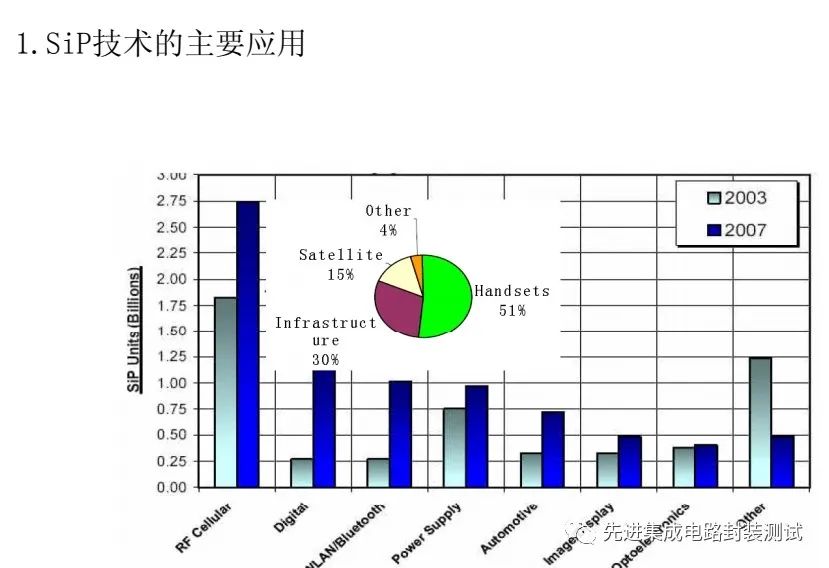

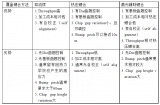

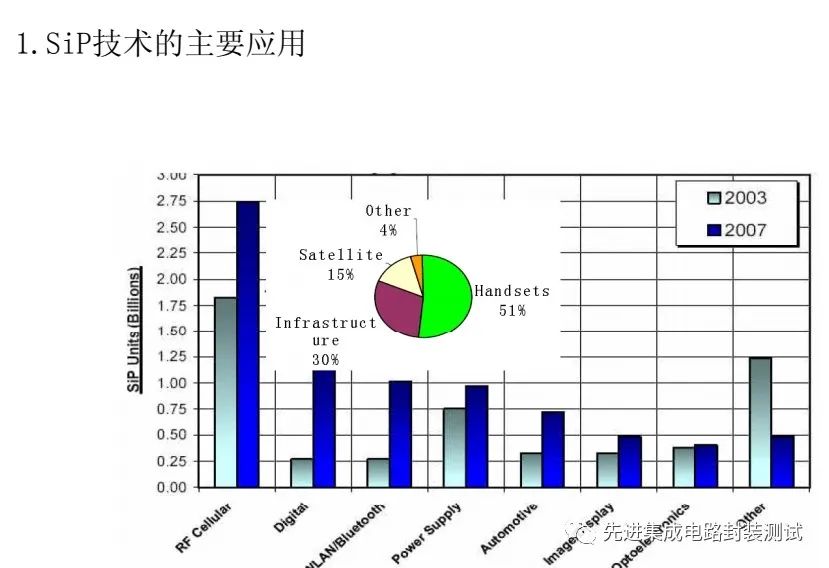

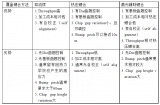

1 SiP技術(shù)的主要應(yīng)用和發(fā)展趨勢(shì) 1. SiP技術(shù)的主要應(yīng)用和發(fā)展趨勢(shì)

2.自主設(shè)計(jì)SiP產(chǎn)品介紹

3.高密度SiP封裝主要技術(shù)挑戰(zhàn)

4. SiP技術(shù)帶動(dòng)MCP封裝工藝技術(shù)的發(fā)展

5. SiP技術(shù)促進(jìn)BGA封裝技術(shù)的發(fā)展

6. SiP催生新的先進(jìn)封裝技術(shù)的發(fā)展

2023-05-19 11:34:27 1207

1207

SiP系統(tǒng)級(jí)封裝(System in Package),先進(jìn)封裝HDAP(High Density Advanced Package),兩者都是當(dāng)今芯片封裝技術(shù)的熱點(diǎn),受到整個(gè)半導(dǎo)體產(chǎn)業(yè)鏈的高度關(guān)注

2023-05-19 09:54:26 1326

1326

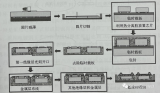

自從Fan-Out封裝問(wèn)世以來(lái),經(jīng)過(guò)多年的技術(shù)發(fā)展,扇出式封裝已經(jīng)形成了多種封裝流程、封裝結(jié)構(gòu)以適應(yīng)不同產(chǎn)品需要,根據(jù)工藝流程,可以分為**先貼芯片后加工RDL的Chip First工藝

2023-05-19 09:39:15 773

773

隨著電子產(chǎn)品趨向于功能化、輕型化、小型化、低功耗和異質(zhì)集成,以系統(tǒng)級(jí)封裝(System in Package, siP)、圓片級(jí)封裝( Wafer Level Package.WLP)、2.5D/3D 封裝等為代表的先進(jìn)封裝技術(shù)越來(lái)越多地應(yīng)用到電子產(chǎn)品中。

2023-05-11 14:39:38 451

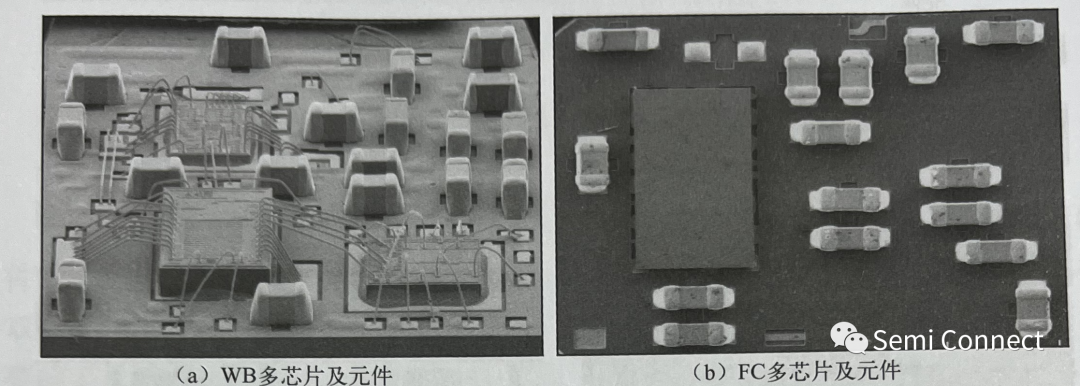

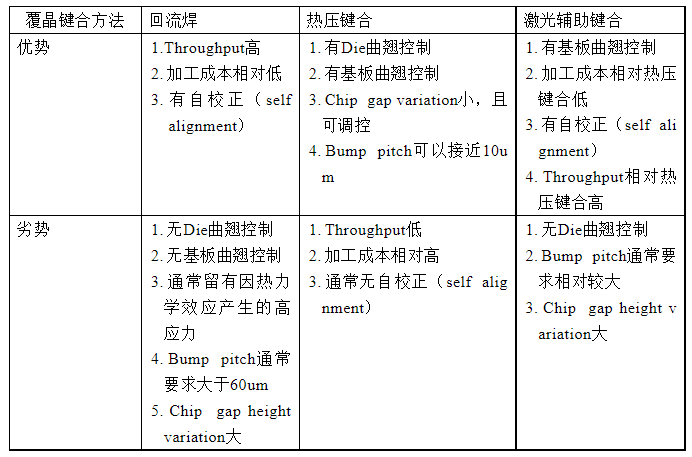

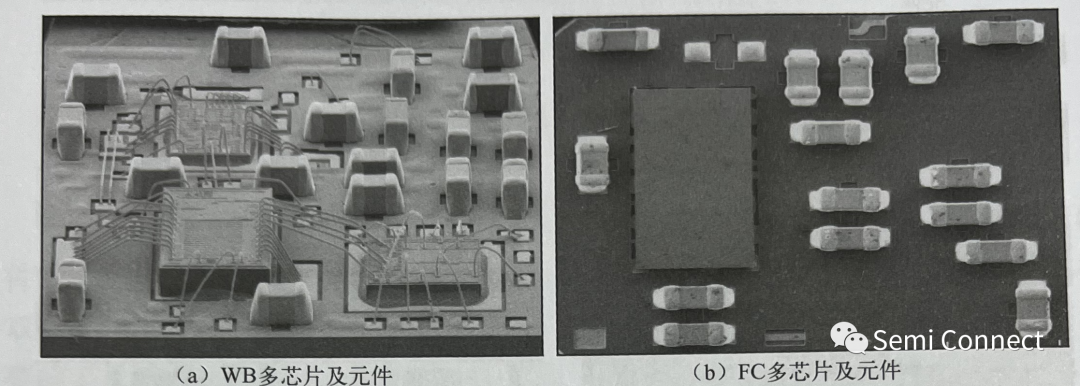

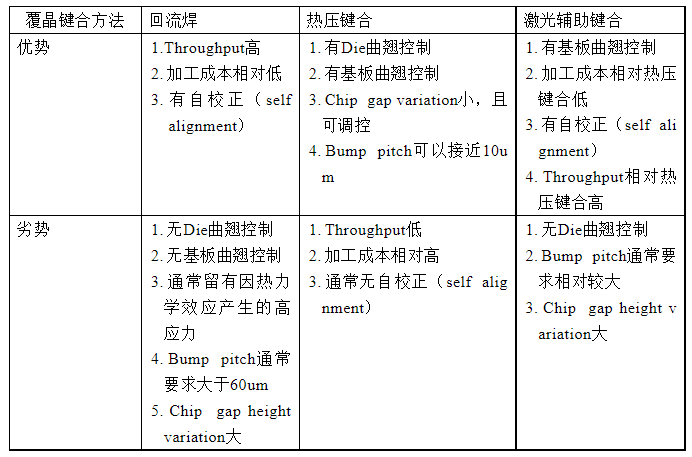

451 (858mm2)以及制程的縮小也變得非常艱難且性價(jià)比遇到挑戰(zhàn), 多芯片封裝技術(shù)來(lái)到了舞臺(tái)的中心成為進(jìn)一步提升芯片性能的關(guān)鍵。覆晶鍵合技術(shù)已然成為先進(jìn)多芯片封裝最重要的技術(shù)之一。

2023-05-11 10:24:38 615

615

系統(tǒng)級(jí)封裝 (System in Package, SiP)是指將單個(gè)或多個(gè)芯片與各類(lèi)元件通過(guò)系統(tǒng)設(shè)計(jì)及特定的封裝工藝集成于單一封裝體或模塊,從而實(shí)現(xiàn)具完整功能的電路集成,如圖 7-115 所示

2023-05-10 16:54:32 828

828

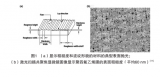

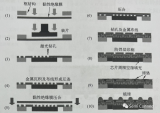

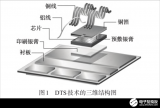

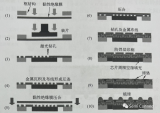

板級(jí)埋人式封裝是一種在基板制造工藝的基礎(chǔ)上融合芯片封裝工藝及 SMT工藝的集成封裝技術(shù),既可以是單芯片封裝、多芯片封裝,也可以是模組封裝、堆疊封裝。與傳統(tǒng)封裝中在基板表面貼裝芯片或元件不同,板級(jí)埋人式封裝直接將芯片或元件嵌人基板中間,因此它具有更短的互連路徑、更小的體積、更優(yōu)的電熱性能及更高的集成度。

2023-05-09 10:21:53 833

833

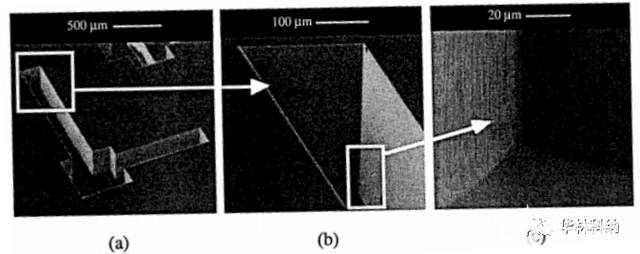

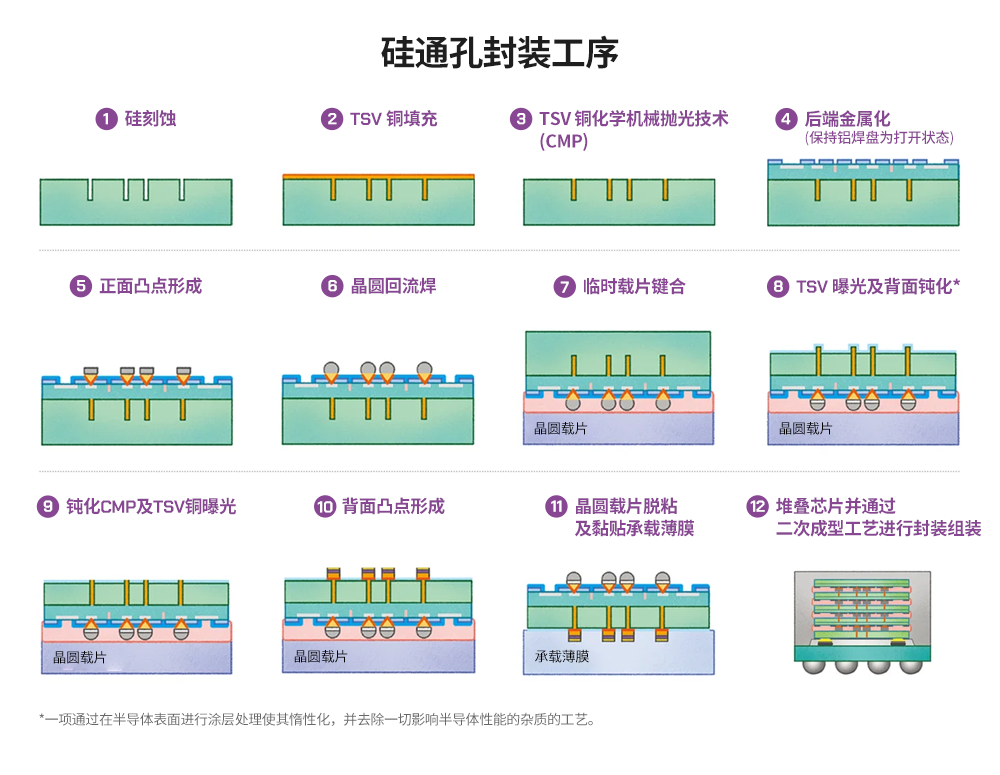

硅通孔(TSV) 是當(dāng)前技術(shù)先進(jìn)性最高的封裝互連技術(shù)之一。基于 TSV 封裝的核心工藝包括 TSV 制造、RDL/微凸點(diǎn)加工、襯底減薄、圓片鍵合與薄圓片拿持等。

2023-05-08 10:35:24 2024

2024

進(jìn)人芯片的線路更短,也具有更好的電性能。圓片級(jí)封裝可以通過(guò)采用比傳統(tǒng)封裝更細(xì)的線路實(shí)現(xiàn)高密度的封裝再布線,因此能夠在實(shí)現(xiàn)封裝小型化的同時(shí),提供更高的帶寬,從而更加適應(yīng)先進(jìn)技術(shù)節(jié)點(diǎn)芯片的封裝。

2023-05-08 10:33:17 1071

1071

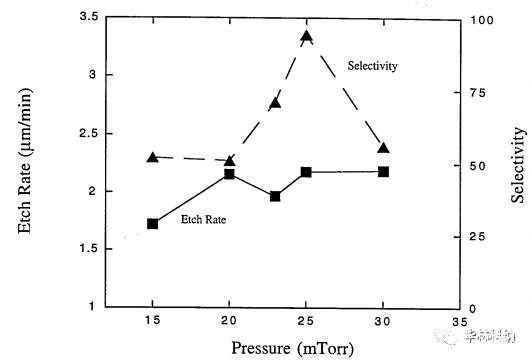

熱壓鍵合工藝的基本原理與傳統(tǒng)擴(kuò)散焊工藝相同,即上下芯片的Cu 凸點(diǎn)對(duì)中后直接接觸,其實(shí)現(xiàn)原子擴(kuò)散鍵合的主要影響參數(shù)是溫度、壓力、時(shí)間. 由于電鍍后的Cu 凸點(diǎn)表面粗糙并存在一定的高度差。

2023-05-05 11:30:17 1380

1380

來(lái)源:Cadence楷登 2023年4月26日,楷登電子近日宣布基于臺(tái)積電 3nm(N3E)工藝技術(shù)的 Cadence? 16G UCIe? 2.5D 先進(jìn)封裝 IP 成功流片。該 IP 采用

2023-04-27 16:35:40 452

452

據(jù)知名半導(dǎo)體分析機(jī)構(gòu)Yole分析,先進(jìn)封裝極大地推動(dòng)了內(nèi)存封裝行業(yè),推動(dòng)了增長(zhǎng)和創(chuàng)新。

2023-04-20 10:15:52 784

784 來(lái)源:上海寶山 據(jù)上海寶山官微消息,上海唯一、全國(guó)一流的易卜半導(dǎo)體12吋全自動(dòng)先進(jìn)封裝中試線和量產(chǎn)廠房啟用暨首臺(tái)設(shè)備搬入儀式舉行,標(biāo)志著易卜將具備完整的先進(jìn)封裝自主技術(shù)、設(shè)計(jì)、研發(fā)和生產(chǎn)的綜合能力

2023-04-19 16:30:45 388

388 (858mm2)以及制程的縮小也變得非常艱難且性價(jià)比遇到挑戰(zhàn), 多芯片封裝技術(shù)來(lái)到了舞臺(tái)的中心成為進(jìn)一步提升芯片性能的關(guān)鍵。 覆晶鍵合技術(shù)已然成為先進(jìn)多芯片封裝最重要的技術(shù)之一。

2023-04-19 09:42:52 1011

1011

芯片升級(jí)的兩個(gè)永恒主題:性能、體積/面積。芯片技術(shù)的發(fā)展,推動(dòng)著芯片朝著高性能和輕薄化兩個(gè)方向提升。而先進(jìn)制程和先進(jìn)封裝的進(jìn)步,均能夠使得芯片向著高性能和輕薄化前進(jìn)。面對(duì)美國(guó)的技術(shù)封裝,華為

2023-04-15 09:48:56 1952

1952 BGA封裝技術(shù)是一種先進(jìn)的集成電路封裝技術(shù),主要用于現(xiàn)代計(jì)算機(jī)和移動(dòng)設(shè)備的內(nèi)存和處理器等集成電路的封裝。與傳統(tǒng)的封裝方式相比,BGA封裝具有更小的體積,更好的散熱性能和電性能,可在相同體積下提高

2023-04-11 15:52:37

電子發(fā)燒友App

電子發(fā)燒友App

評(píng)論