嗨,我有一個4時鐘域的原始設計。在添加第5個時鐘域并將設計加載到芯片中后,該設計在硬件中不再起作用。我正在使用斯巴達3E 1600這是一個很大的設計,但作為一個例子,我有一個簡單的計數器,如下所示

2019-06-17 14:32:33

文章目錄前言時鐘及時鐘域時鐘,時序邏輯的心跳時鐘信...

2021-07-29 07:43:44

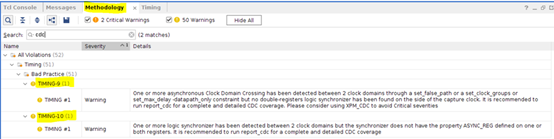

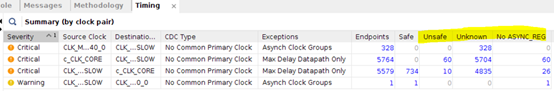

1、跨時鐘域信號的約束寫法 問題一:沒有對設計進行全面的約束導致綜合結果異常,比如沒有設置異步時鐘分組,綜合器對異步時鐘路徑進行靜態時序分析導致誤報時序違例。 約束文件包括三類,建議用戶應該將

2022-11-15 14:47:59

程序,并檢查寄存器的內容。我在rx和tx管腳上連接了作用域,用RS232解碼器在作用域上告訴我接收和發送什么。當它工作時,我可以看到字節被發送和接收,當我在RX中斷中設置斷點時,我可以停止程序。我確認

2020-03-23 07:04:37

ATK-HSWLDBG無線調試器-帶小接收端 BURNER 5V

2023-03-28 13:05:52

有線束工程師的學員反饋,在CHS的項目管理模塊中新建項目后,無法進行域的選擇。而他明明在Capital User模塊中新建了域。這種情況該如何解決呢?問題描述:1.Captial User中已經

2021-01-12 17:06:22

的數據(多bit)。在這種類似的場景中,我們便可以使用異步雙口RAM來做跨時鐘域處理。先利用ADC芯片提供的60MHz時鐘將ADC 輸出的數據寫入異步雙口RAM,然后使用100MHz的時鐘從RAM中讀出

2021-03-04 09:22:51

FPGA設計中有多個時鐘域時如何處理?跨時鐘域的基本設計方法是:(1)對于單個信號,使用雙D觸發器在不同時鐘域間同步。來源于時鐘域1的信號對于時鐘域2來說是一個異步信號。異步信號進入時鐘域2后,首先

2012-02-24 15:47:57

[size=11.818181991577148px]FPGA開發中,遇到的最多的就是異步時鐘域了。[size=11.818181991577148px]檢查初學者的代碼,發現最多的就是這類

2014-08-13 15:36:55

(10)FPGA跨時鐘域處理1.1 目錄1)目錄2)FPGA簡介3)Verilog HDL簡介4)FPGA跨時鐘域處理5)結語1.2 FPGA簡介FPGA(Field Programmable

2022-02-23 07:47:50

1、IC設計中的多時鐘域處理方法簡析我們在ASIC或FPGA系統設計中,常常會遇到需要在多個時鐘域下交互傳輸的問題,時序問題也隨著系統越復雜而變得更為嚴重。跨時鐘域處理技術是IC設計中非常重要的一個

2022-06-24 16:54:26

MCU中怎么確定一個變量的作用域

2023-10-09 06:46:34

“跨域”、“混合域”分析、讓工程師可以同時檢測任何時間點上模擬、數字、總線與射頻信號之間的交互作用,是當今的最佳系統級調試工具,它也將要大大改變你測試的方法。要知道MDO4000混合域示波器怎樣有異于頻譜分析儀加示波器,或怎樣有異于示波器的FFT運算,我們首先從它的結構上闡述它的技術基礎。

2019-06-06 06:51:35

的特色之一,但MDO4000 絕不是以上羅列的五種測試工具的簡單組合,這五種功能工作在同一時鐘、同一觸發機制下,使得MDO4000 具有創新的時域、頻域、調制域時間相關的跨域分析功能。為此,我們將

2019-07-19 07:02:07

系統,是MDO4000 系列混合域分析儀的特色之一,但MDO4000 絕不是以上羅列的五種測試工具的簡單組合,這五種功能工作在同一時鐘、同一觸發機制下,使得MDO4000 具有創新的時域、頻域、調制域時間

2019-07-19 06:43:08

STM32時鐘樹學習筆記六:有三種不同的時鐘源可以用來驅動系統時鐘(SYSCLK)1:HSI振蕩時鐘2:HSE振蕩時鐘3:PLL時鐘用戶可以通過配置多個域分頻器配置AHB、高速APB(APB2

2021-08-02 07:39:44

SystemClock_Config(),其中配置了所有時鐘。那里:啟用備份訪問(在 PWR->CR 中設置 DBP)重置備份域(在 RCC->BDCR 中設置然后清除 BDRST)將時鐘源設置為HSI(BDCR

2023-01-13 06:04:15

1.當HSI被用于作為PLL時鐘的輸入時,系統時鐘能得到的最大頻率是64MHz。2.對于內部和外部時鐘源的特性,請參考相應產品數據手冊中“電氣特性”章節。用戶可通過多個預分頻器配置AHB、高速APB

2021-08-19 08:56:15

,無需計算校驗和,不要產生順序號,無需發送確認報文。下圖所示程序,main函數中創建了一些消息隊列和UNIX域套接字,并為每個消息隊列開啟了一個新線程。然后它在一個無限循環中用poll來輪詢選擇一個

2016-09-02 11:59:01

在看u***,書上說u***數據包的同步域可以同步主機端和從機端的時鐘,這個怎么理解u***接口沒有時鐘線,我又想到了單片機串口的波特率,不知道有沒有關系,向大家請教了這個簡單的問題,很想知道答案

2019-07-02 18:06:13

XP退域后怎么才能加回以前的域是這樣一件事情,我的XP電腦是不連接網絡的,但是它之前的用戶一直連接那域, 這次我修改的工作組,結果那域不見了,用戶也進不去了;請問還能加回以前的域嗎?

2012-06-09 16:41:55

在matlab中對二值圖像不同的連通域進行標寫序號該用什么語句函數啊?

2016-10-13 20:26:21

python變量的作用域1. 作用域Python的作用域可以分為四種:L (Local) 局部作用域E (Enclosing) 閉包函數外的函數中G (Global) 全局作用域B

2022-03-03 16:50:37

雙口RAM如何實現跨時鐘域通信啊?怎么在quartus ii仿真???

2017-05-02 21:51:39

跨越時鐘域FPGA設計中可以使用多個時鐘。每個時鐘形成一個FPGA內部時鐘域“,如果需要在另一個時鐘域的時鐘域產生一個信號,需要特別小心。隧道四部分第1部分:過路處。第2部分:道口標志第3部分:穿越

2012-03-19 15:16:20

在調試是DS1302里面的時間時鐘讀不到LCD中,請各位看看

2012-07-18 09:55:04

的數據(多bit)。在這種類似的場景中,我們便可以使用異步雙口RAM來做跨時鐘域處理。先利用ADC芯片提供的60MHz時鐘將ADC 輸出的數據寫入異步雙口RAM,然后使用100MHz的時鐘從RAM中讀出

2021-02-21 07:00:00

60MHz的時鐘上升沿變化,而FPGA內部需要使用100MHz的時鐘來處理ADC采集到的數據(多bit)。在這種類似的場景中,我們便可以使用異步雙口RAM來做跨時鐘域處理。 先利用ADC芯片提供的60MHz

2021-01-08 16:55:23

的主要目標是將該板與模擬器件AD9229 ADC接口,ADC具有串行LVDS接口,傳輸速率為480 Mbps。生成DDR數據時鐘和幀時鐘用于數據捕獲。 ZESTET1板運行頻率為125 MHz,但

2019-06-12 13:30:44

異步bus交互(一)— 兩級DFF同步器跨時鐘域處理 & 亞穩態處理1.問題產生現在的芯片(比如SOC,片上系統)集成度和復雜度越來越高,通常一顆芯片上會有許多不同的信號工作在不同的時鐘頻率

2022-02-17 06:34:09

有誰知道為什么transcieverwizard會建立一個7位移位寄存器來跨越時鐘域?此代碼位于示例設計重置狀態機* _sync.v塊中。這是針對V7的嗎?謝謝,Roopa

2020-07-29 10:52:06

目錄一、什么是IO電源域配置?二、IO電源域配置方法三、RK809電源芯片dts配置一、什么是IO電源域配置?其實就是管理IO輸出的電平;假如硬件上IO電源域配置為3.3V,則IO輸出最大電平為

2021-12-27 06:44:14

什么是UPF功率域和域邊界?

2021-09-29 06:08:09

ISE中編譯為.bit文件。系統被設計為多重鎖定域,其中第一個域只是獲取數據并負責寫入和重置共享FIFO,并且從相機計時(因此也以相同的時鐘速度運行 - 大約8MHz) - 此信號用于Sys.gen。具有

2019-08-27 06:28:47

如何測量系統中時間相關的時域和頻域信號?以RFID讀寫器系統為例,介紹MDO4000的跨域調試應用

2021-04-09 06:18:12

在支持位操作的單片機中,如C51,使用位域定義變量或者寄存器,操作方便并且節約空間。 問題1:但是很多單片機不支持位操作,仍然使用位域,那么匯編語言將如何執行?我理解的是,匯編間接實現位操作,但是

2016-09-16 22:25:32

c語言里規定的位域的方式進行比特位操作,可以對某一位進行操作;一般情況下,比如普通的存儲數據的區域,位域沒有任何意義。通常,位域可以用來進行對一些要進行比特位操作的場合,比如標志寄存器的標志位清零

2017-08-03 09:54:32

一、位域描述存放一個開關量或者其他開關狀態時,用一位二進位即可。為了減少嵌入式內存資源的開銷,可以使用位域進行定義,位域是C語言支持的一種數據結構,稱為“位域”或“位段”。“位域”是把一個字節中

2021-12-15 07:47:52

#hello,JS:04作用域和作用域鏈

2019-09-10 10:21:18

關于cdc跨時鐘域處理的知識點,不看肯定后悔

2021-06-21 07:44:12

關于異步時鐘域的理解的問題: 這里面的count[25]、和count[14]和count[1]算是多時鐘域吧?大俠幫解決下我的心結呀,我這樣的理解對嗎?

2012-02-27 15:50:12

解決了調試系統軟/硬件協同驗證中JTAG信號交互時的時序匹配問題。1 自適應時鐘技術1.1 基本概念自適應時鐘(Adaptive Clocking)是一種信號同步技術,其基本原理來源于異步電路設計中的自動

2019-05-21 05:00:22

你好,我在Viv 2016.4上使用AC701板。我需要同步從一個時鐘域到另一個時鐘域的多位信號(33位)。對我來說,這個多位信號的3階段流水線應該足夠了。如果將所有觸發器放在同一個相同的切片

2020-08-17 07:48:54

在調試GD32芯片時遇到了時鐘配置錯誤的問題,仔細研究文檔和網上資料,認真調試之后做了以下總結,希望能幫到同樣有類似困惑的你。**1.認識時鐘HXTAL:高速外部時鐘;LXTAL:低速外部時鐘

2021-07-23 10:06:14

綜合試驗基地,主要從事雷電干擾防護和城市軌道交通安全的研究。客戶研發方向為智能家居產品,使用無線傳輸數據,其中RF模塊外購。要驗證射頻模塊的功能和指標,以及聯合調試在實際工作中的問題。射頻模塊于系統之間

2019-06-06 07:18:26

1、基于RK3399的Linux kernel中CPU時鐘管理介紹絕大多數的電子器件都是由時鐘驅動其工作的。而SoC芯片或電路板中的時鐘以樹狀結構呈現,按時鐘域進行劃分,按照不同的時鐘需求

2022-06-21 16:00:23

時鐘域電路設計中由于不存在時鐘之間的延遲和錯位,所以建立條件和保持條件的時間約束容易滿足。而在多時鐘域里由于各個模塊的非同步性,則必須考慮亞穩態的發生,如圖1所示。 2 多時鐘域數據傳遞方案 多時鐘

2011-09-07 09:16:40

時鐘)的邏輯。在真正的ASIC設計領域,單時鐘設計非常少。2、控制信號從快時鐘域同步到慢時鐘域與同步器相關的一個問題是來自發送時鐘域的信號可能在被慢時鐘域采樣之前變化。將慢時鐘域的控制信號同步到快時鐘域

2022-04-11 17:06:57

。為了獲得更多,我使用時鐘向導添加了較慢的時鐘,以便在調試設置中使用它們,直到比特流生成一切正常,但是當涉及到調試時,我收到此警告:open_hw_targetINFO:[Labtoolstcl

2020-08-17 10:04:52

時鐘域處理。先利用 ADC 芯片提供的 60MHz 時鐘將 ADC 輸出的數據寫入異步雙口 RAM,然后使用 100MHz 的時鐘從 RAM 中讀出。對于使用異步雙口 RAM 來處理多 bit 數據

2020-09-22 10:24:55

跨時鐘域處理是FPGA設計中經常遇到的問題,而如何處理好跨時鐘域間的數據,可以說是每個FPGA初學者的必修課。如果是還是在校的學生,跨時鐘域處理也是面試中經常常被問到的一個問題。在本篇文章中,主要

2021-07-29 06:19:11

跨時鐘域處理是什么意思?如何處理好跨時鐘域間的數據呢?有哪幾種跨時鐘域處理的方法呢?

2021-11-01 07:44:59

你好,我很難理解如何正確設計一個時鐘使能信號,以促進兩個同步時鐘之間的時鐘域交叉,其中一個是慢速,一個是快速。我所擁有的情況與下圖所示的情況非常相似(取自UG903圖5-18)。如何確保CLK2產

2019-04-15 08:36:30

如何通過Mstar平臺對RTC時鐘進行調試?

2021-10-13 07:34:03

對于仿真而言,與DUT打交道的無非是接口信號的驅動,而我們的設計往往是同步的,這就與避免不了與時鐘信號打交道。時鐘域在SpinalHDL中,時鐘域的概念包含了時鐘、復位、軟復位、時鐘使能等系列信號

2022-07-26 17:07:53

親愛的朋友們, 我有一個多鎖設計。時鐘為50MHz,200MHz和400Mhz。如果僅使用400MHz時鐘并使用時鐘使能產生200Mhz和50Mhz時鐘域。現在我需要將信號從一個時鐘域傳遞到另一個

2019-03-11 08:55:24

把時鐘變慢可以有效增加DFF的setup時間嗎?時鐘域A的多bit信號一定要經過同步才能被時鐘域B采用嗎?

2021-11-02 08:26:02

時鐘域處理。先利用 ADC 芯片提供的 60MHz 時鐘將 ADC 輸出的數據寫入異步雙口 RAM,然后使用 100MHz 的時鐘從 RAM 中讀出。對于使用異步雙口 RAM 來處理多 bit 數據

2020-10-20 09:27:37

理解UPF功率域和域邊界一、介紹 在先進工藝技術的低功耗之爭中,統一功率格式(UPF)在降低動態和靜態功率方面起著核心作用。較高的流程節點絕對具有吸引力,因為在較小的die區域中可以以較低的成本

2021-07-26 06:23:19

上完成復雜的測量。 對嵌入式無線電,如圖16所示的Zigbee設計.您可以觸發 RF事件啟動,觀察微處理器控制器解碼的SPI控制線的命 令行時延、啟動過程中的漏極電流和電壓以及發生的任何 頻譜事件。您現在可以在一個畫面中,以時間相關的方式 觀察無線電的所有域:協議(數宇)、模擬和RF。

2017-08-31 08:55:59

電源域隔離是電壓監控ADC系統的一個重要設計要點,不合理的電源域隔離可能導致芯片關不掉,芯片發生閂鎖,甚至芯片損壞的后果。這些問題主要是由于芯片內部ESD保護二極管的限制,那么如何更好處理電源域隔離設計呢?

2019-02-25 09:08:09

電源域是什么?

2017-08-07 18:59:27

相同的IO域VDDPST和VDD的電壓輸入是一樣的嗎?RK3399中的IO域電壓該怎樣去選擇呢?

2022-03-07 07:10:14

邏輯出身的農民工兄弟在面試時總難以避免“跨時鐘域”的拷問,在諸多跨時鐘域的方法里,握手是一種常見的方式,而Stream作為一種天然的握手信號,不妨看看它里面是如做跨時鐘域的握手

2022-07-07 17:25:02

和發送數據,處理異步信號,以及為帶門控時鐘的低功耗ASIC進行原型驗證。 這里以及后面章節提到的時鐘域,是指一組邏輯,這組邏輯中的所有同步單元(觸發器、同步RAM塊以及流水乘法器等)都使用同一個網絡

2022-10-14 15:43:00

型的問題,并且這些問題的解決方案也有所不同。本文討論了不同類型的跨時鐘域,以及每種類型中可能遇到的問題及其解決方案。在接下來的所有部分中,都直接使用了上圖所示的信號名稱。例如,C1和C2分別表示源時鐘

2022-06-23 15:34:45

bq1_dat穩定在1,bq2_dat也輸出穩定的1。最后,從特權同學的經驗和實踐的角度聊一下。跨時鐘域的信號同步到底需要1級還是2級,完全取決于具體的應用。如果設計中這類跨時鐘域信號特別多,增加1級

2020-08-20 11:32:06

] set_false_paths –from [get_clocks clk_66] –to [get_clocks clk_100]設計中fifo前端時鐘域是cmos_pclk在TimeQuest

2018-07-03 11:59:59

,以及為帶門控時鐘的低功耗ASIC進行原型驗證。本章討論一下在FPGA設計中多時鐘域和異步信號處理有關的問題和解決方案,并提供實踐指導。

這里以及后面章節提到的時鐘域,是指一組邏輯,這組邏輯中的所有同步

2023-06-02 14:26:23

高速無線調試器HSWLDBG BURNER 3.3,5

2023-03-28 13:06:20

目標的運動速度、加速度,是估計目標后續空間位置必需的重要參數,對光電設備持續捕獲目標具有重要現實意義。在分析經緯儀交匯跟蹤目標原理的基礎上,將目標的運動分解

2010-01-11 11:10:12 10

10 將空間飛行器分為目標和射彈兩類,對二者撞擊過程中的彈目交匯模型進行研究。在目標構型分析的基礎上,基于基本幾何形體建立目標等效模型,實現了典型目標的數學描述。考慮彈

2011-05-03 17:18:00 0

0 針對室內CCD交匯測量的試驗環境,通過添加輔助光源照明,在基于CCD立靶測量原理的條件下,分析了室內立靶影響捕獲率的原因,并建立了室內立靶的捕獲率模型。該模型能夠為室內立

2012-04-05 16:21:35 44

44 時鐘芯片DS1302目前得到廣泛的應用,但是DS1302的調試還是很有難度的。這篇文章就來說說DS1302時鐘芯片的調試驚艷,奉上時鐘芯片調試程序貼,是網上下的,我已經通過硬件測試,絕對沒有問題。

2017-10-19 11:12:24 10225

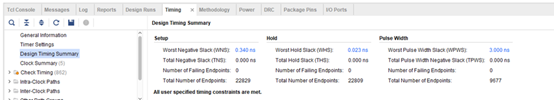

10225 博文介紹了如何調試設計中的時鐘域交匯問題。 問題說明: 在此設計中,用戶生成了比特流并將其用于器件編程,在硬件上進行測試時,用戶發現少量時鐘域上無法獲得期望的功能。 用戶對行為仿真和實現后仿真進行了測試,發現信號上可得到正確的結果。 同時,這些用

2021-08-20 09:32:21 5152

5152

本篇博文中的分析是根據真實客戶問題撰寫的,該客戶發現在現場出現罕見的比特翻轉, 本篇博文旨在演示用于縮小根本原因范圍以及修復此問題的部分調試技巧。 最終發現,此問題是由于時鐘域交匯 (CDC) 處理

2021-09-10 09:44:55 1172

1172 S32K14x系列MCU時鐘調試筆記

2021-11-18 16:51:02 45

45 第二章 電機調試和時鐘配置上一章我們移植好了單片機,于是在我們興奮地看到自己點亮了LED之后,開始著手準備驅動的設置,那么這里面又會有什么問題呢?我把我遇到的困難和問題記錄在此,同時也為你們答疑解惑。電機介紹can通信回顧時鐘設置在線調試...

2021-12-04 18:06:05 7

7 SWD是STM32單片機常用的調試模式之一。它通過單一的調試引腳(SWDIO)和時鐘引腳(SWCLK)來進行調試和編程操作。使用SWD調試模式,可以進行單步調試、斷點調試、查看寄存器狀態等操作。

2023-12-02 17:14:03 1322

1322

電子發燒友App

電子發燒友App

評論