運算放大器構(gòu)成加法器 可以分為同相加法器和反相加法器

2022-08-05 17:17:38 22392

22392

加法器(Adder)** 是非常重要的,它不僅是其它復雜算術(shù)運算的基礎(chǔ),也是** CPU **中** ALU **的核心部件(全加器)。

2023-10-09 11:14:14 733

733

求助誰幫我設(shè)計一個32位浮點加法器,求助啊,謝謝啊 新搜剛學verilog,不會做{:4_106:}

2013-10-20 20:07:16

描述4位加法器四位加法器將兩個 4 位二進制數(shù)相加(十進制表示法中的一個數(shù)字 0-15)適用于晶體管邏輯。數(shù)字是用一個8針撥碼開關(guān)輸入的,前4個開關(guān)是第一個數(shù)字,下一個到最后一個是第二個數(shù)字。電路板

2022-07-07 06:08:47

加法器的芯片如何選擇?常用的有哪些?

2017-08-09 14:39:13

請問下大家,,進位選擇加法器和進位跳躍加法器的區(qū)別是啥啊?我用Verilog實現(xiàn)16位他們的加法器有什么樣的不同啊?還請知道的大神告訴我一下。。

2016-10-20 20:23:54

的邏輯狀態(tài)表自行分析。 這種全加器的任意一位的加法運算,都必須等到低位加法完成送來進位時才能進行。這種進位方式稱為串行進位,它的缺點是運算速度慢,但其電路比較簡單,因此在對運算速度要求不高的設(shè)備中,仍不失為一種可取的全加器。T692集成加法器就是這種串行加法器。 圖3 例1的邏輯圖

2018-10-11 16:33:47

IP核加法器

2019-08-14 14:24:38

使用加法器把信號提高2.5V,開始使用op37,帶寬不夠,換成opa847。結(jié)果換成opa847后,在輸入端信號已經(jīng)出現(xiàn)問題,波形如圖0所示,附上op37輸入端觀察到的波形圖1。請問一下 ,加法器各電阻阻值選取在什么范圍?除了R1=R2,Rf=2Rg

2016-07-15 09:24:21

小弟是初學者,剛把verilog基本語法看完,只會寫簡單的四位或者八位的加法器,但是兩個4位加法器級聯(lián)構(gòu)成一個8位加法器不會寫啊,應該是頂層調(diào)用兩個四位的,但不知道具體怎么寫,求大神指點!不勝感激!

2013-12-03 11:51:06

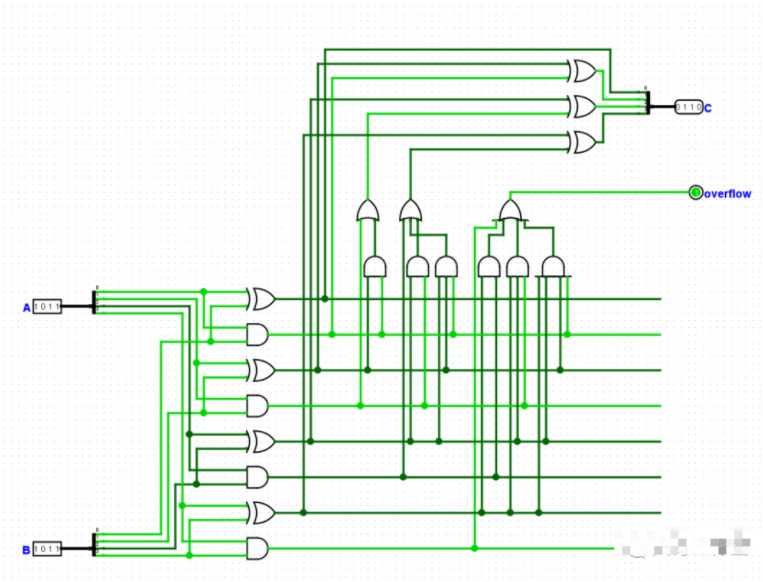

Verilog數(shù)字系統(tǒng)設(shè)計四復雜組合邏輯實驗2文章目錄Verilog數(shù)字系統(tǒng)設(shè)計四前言一、什么是8位全加器和8為帶超前進位的全加器?二、編程1.要求:2.門級原語實現(xiàn)8位全加器:3.門級原語實現(xiàn)帶

2022-02-09 07:49:48

什么是加法器?加法器的原理是什么 反相加法器等效原理圖解析

2021-03-11 06:30:35

嗨,對于下面的代碼片段,合成后會得到哪種類型的加法器?例如:半加法器,全加器,CLA,Ripple加法器?模塊ee(輸入a,e,輸出reg c);總是@(*)c = a + e;endmodule

2020-03-19 09:49:31

只是想知道,如果我做一個大加法器,我可以說128位加法器。從LUT的角度來看,加法器的外觀如何,因為我看到Spartan 6器件的片M具有與其他塊連接的進位邏輯。如果可能,有人可以為加法器提供LUT透視框圖,只需2 LUT之間的連接就可以理解這個想法。謝謝,

2019-08-08 07:13:38

大家好!我在vhdl中設(shè)計了一個加法器波紋進位和加法器查找頭。我已經(jīng)模擬它并合成它一切正常。但我想比較加法器的性能(面積利用率和速度)。我可以在設(shè)計摘要中看到ISE的區(qū)域利用率,但我不知道

2019-01-22 09:37:17

請問Quartus中自帶的加法器,和平時我們在module中寫的“+”有什么區(qū)別呢?還有就是加法涉及到數(shù)據(jù)已出的問題,我想如果,我把輸出的位寬設(shè)置的很大,足以滿足兩個數(shù)相加之后的位寬,這時候是不是不需要考慮溢出的問題了呢?

2015-01-11 10:53:33

反比例加法器如何計算平衡電阻?

2020-06-11 18:34:00

嗨,我正在嘗試在Zynq設(shè)備上實現(xiàn)一些簡單的加法器,但是當我玩不同的代碼時,我注意到并不總是推斷進位鏈,例如:分配{cout,c} = a + b;其中a,b,c是相同寬度的信號。但是,如果聲明c要

2020-03-13 09:42:21

放大電路和加法器電路各自測試時都對,但放大器輸出之后接加法器的時候輸出不對!新手求助

2016-04-28 08:41:31

需要設(shè)計一個模加法器,書上沒有詳細的講解,只說是用端回進位加法器實現(xiàn)模2^n-1,可是具體應該怎么設(shè)計啊~~~~

2016-07-07 14:48:36

的加法器估算4個LUT,但無論我使用優(yōu)化等多少(設(shè)計目標等),每個加法器都會結(jié)束使用8LUT。有沒有我遺漏的東西或4 LUT估計不可能?根據(jù)我自己的實現(xiàn),我可以使用5LUT(10 LUT5)進行8位

2019-04-03 15:55:35

蜂鳥e203在實現(xiàn)多周期乘法的時候,復用了ALU共享數(shù)據(jù)通路的加法器。如果乘法的后級指令(下一指令)也需要用到ALU中的加法器。這個地方如何解決它們的資源沖突?暫時沒想通這個地方,希望有人解答一下,謝謝。

2023-08-11 12:05:10

請問一下高速流水線浮點加法器的FPGA怎么實現(xiàn)?

2021-05-07 06:44:26

加法運算是最重要最基本的運算, 所有的其他基本算術(shù)運算, 減、 乘、 除、 模乘運算最終都能歸結(jié)為加法運算。 在不同的場合使用的加法器對其要求也不同, 有的要求

2009-04-08 15:15:12 41

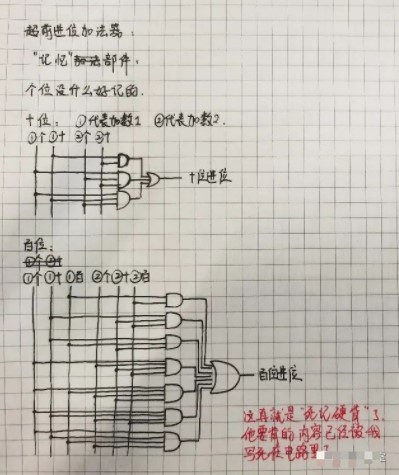

41 摘要:加法運算在計算機中是最基本的,也是最重要的運算。傳統(tǒng)的快速加法器是使用超前進位加法器,但其存在著電路不規(guī)整,需要長線驅(qū)動等缺點。文章提出了采用二叉樹法設(shè)

2010-05-19 09:57:06 62

62 摘要:應用CMOS電路開關(guān)級設(shè)計技術(shù)對超前進位全加器進行了設(shè)計,并用PSPICE模擬進行了功能驗證.與傳統(tǒng)門級設(shè)計電路相比,本文設(shè)計的超前進位電路使用了較少的MOS管,并能保持

2010-05-28 08:18:20 25

25

圖二所示為4位并行的BCD加法器電路。其中上面加法器的輸入來自低一級的BCD數(shù)字。下

2009-03-28 16:35:54 11906

11906

第二十講 加法器和數(shù)值比較器

6.6.1 加法器一、半加器1.含義 輸入信號:加數(shù)Ai,被加數(shù)Bi 輸出信號:本位和Si,向高位

2009-03-30 16:24:54 5501

5501

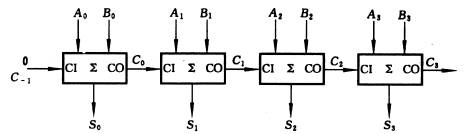

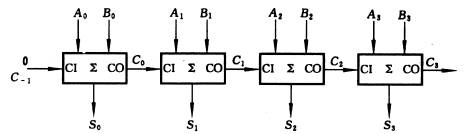

串行進位加法器

若有多位數(shù)相加,則可采用并行相加串行進位的方式來完成。例如,有兩個4位二進制數(shù)A3A2A1A0和B3B2B

2009-04-07 10:35:30 16250

16250

超前進位集成4位加法器74LS283

由于串行進位加法器的速度受到進位信號的限制,人們又設(shè)計了一種多位數(shù)超前進位

2009-04-07 10:36:35 27131

27131

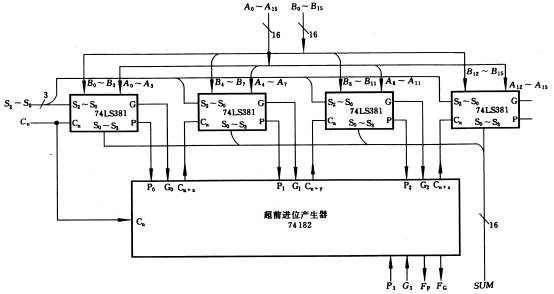

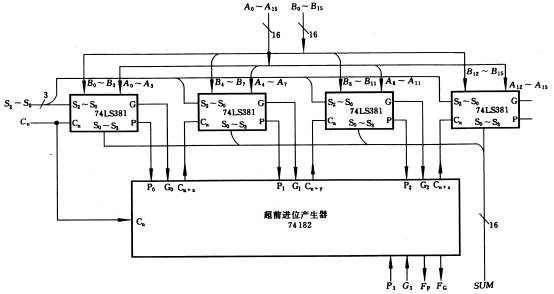

超前進位產(chǎn)生器74182

多位數(shù)的超前進位加法器的進位是并行產(chǎn)生的,大大提高了一算速度。但是隨著位數(shù)的增加,超前進位邏輯電路越來越復雜。為了解決這一矛盾,設(shè)計

2009-04-07 10:37:14 14929

14929

用四位全加器構(gòu)成二一十進制加法器

2009-04-09 10:34:43 5655

5655

加法器:Summing Amplifier

The summing amplifier, a special case of the inverting amplifier, is shown in Figure 4. The circuit gives an

2009-05-16 12:38:34 2626

2626

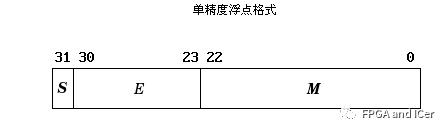

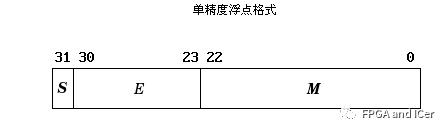

高速流水線浮點加法器的FPGA實現(xiàn)

0 引言現(xiàn)代信號處理技術(shù)通常都需要進行大量高速浮點運算。由于浮點數(shù)系統(tǒng)操作比較復雜,需要專用硬件來完成相關(guān)的操

2010-02-04 10:50:23 2042

2042

加法器,加法器是什么意思

加法器 : 加法器是為了實現(xiàn)加法的。 即是產(chǎn)生數(shù)的和的裝置。加數(shù)和被加數(shù)為輸入,和數(shù)與

2010-03-08 16:48:58 5106

5106 加法器原理(16位先行進位)

這個加法器寫的是一波三折啊,昨天晚上花了兩三個小時好不容易寫完編譯通過了,之后modelsim莫

2010-03-08 16:52:27 10942

10942 十進制加法器,十進制加法器工作原理是什么?

十進制加法器可由BCD碼(二-十進制碼)來設(shè)計,它可以在二進制加法器的基礎(chǔ)上加上適當?shù)摹靶U边壿媮?b class="flag-6" style="color: red">實現(xiàn),該校正邏

2010-04-13 10:58:41 12738

12738 計算機常用的組合邏輯電路:加法器

一、加法器

1.半加器: 不考慮進位輸入時,兩個數(shù)碼X n和Y n相加稱為半加。設(shè)半加和為H n ,則H n 的

2010-04-15 13:48:11 6204

6204 電子發(fā)燒友為您提供了運算放大加法器電路圖!

2011-06-27 09:28:50 7732

7732

2012-04-19 17:03:21 56

56 浮點運算器的核心運算部件是浮點加法器,它是實現(xiàn)浮點指令各種運算的基礎(chǔ),其設(shè)計優(yōu)化對于提高浮點運算的速度和精度相當關(guān)鍵。文章從浮點加法器算法和電路實現(xiàn)的角度給出設(shè)計

2012-07-06 15:05:42 47

47 8位加法器和減法器設(shè)計實習報告

2013-09-04 14:53:33 133

133 為了縮短加法電路運行時間,提高FPGA運行效率,利用選擇進位算法和差額分組算法用硬件電路實現(xiàn)32位加法器,差額分組中的加法單元是利用一種改進的超前進位算法實現(xiàn),選擇進位算

2013-09-18 14:32:05 33

33 Xilinx FPGA工程例子源碼:Xilinx 公司的加法器核

2016-06-07 15:07:45 12

12 同相加法器輸入阻抗高,輸出阻抗低 反相加法器輸入阻抗低,輸出阻抗高.加法器是一種數(shù)位電路,其可進行數(shù)字的加法計算。當選用同相加法器時,如A輸入信號時,因為是同相加法器,輸入阻抗高,這樣信號不太容易流入加法器,反而更容易流入B端。

2016-09-13 17:23:33 55183

55183

加法器VHDL程序,感興趣的小伙伴們可以瞧一瞧。

2016-11-11 15:51:00 5

5 基于Skewtolerant Domino的新型高速加法器

2017-01-22 20:29:21 8

8 構(gòu)造完整的MC14008B 4比特加法器與MOS p溝道和n溝道增強型設(shè)備在一個單一的整體結(jié)構(gòu)。 這個設(shè)備由四個完整的蛇與快速內(nèi)部先行的輸出。 它是有用的在二進制加法和其他算法的應用程序。 快速并行進位輸出位允許高速與其他毒蛇在系統(tǒng)操作使用時。

2017-04-06 08:56:16 11

11 加法器是為了實現(xiàn)加法的。即是產(chǎn)生數(shù)的和的裝置。加數(shù)和被加數(shù)為輸入,和數(shù)與進位為輸出的裝置為半加器。若加數(shù)、被加數(shù)與低位的進位數(shù)為輸入,而和數(shù)與進位為輸出則為全加器。

2017-06-06 08:45:01 22719

22719

,影響整個CPU的性能,為了減小這種延遲,遂采用超前進位加法器(也叫先行進位加法器),下面來介紹一下設(shè)計的原理。

2018-07-09 10:42:00 19433

19433

加法器是產(chǎn)生數(shù)的和的裝置。加數(shù)和被加數(shù)為輸入,和數(shù)與進位為輸出的裝置為半加器。

2017-08-16 09:39:34 21933

21933

在電子學中,加法器是一種數(shù)位電路,其可進行數(shù)字的加法計算。加法器是產(chǎn)生數(shù)的和的裝置。加數(shù)和被加數(shù)為輸入,和數(shù)與進位為輸出的裝置為半加器。若加數(shù)、被加數(shù)與低位的進位數(shù)為輸入,而和數(shù)與進位為輸出則為全加器。常用作計算機算術(shù)邏輯部件,執(zhí)行邏輯操作、移位與指令調(diào)用。

2017-08-16 10:21:31 145618

145618

加法器是產(chǎn)生數(shù)的和的裝置。加數(shù)和被加數(shù)為輸入,和數(shù)與進位為輸出的裝置為半加器。減法電路是基本集成運放電路的一種,減法電路可以由反相加法電路構(gòu)成,也可以由差分電路構(gòu)成。基本集成運放電路有加、減、積分和微分等四種運算。一般是由集成運放外加反饋網(wǎng)絡所構(gòu)成的運算電路來實現(xiàn)。

2017-08-16 11:09:48 159694

159694

在電子學中,加法器是一種數(shù)位電路,其可進行數(shù)字的加法計算。加法器是產(chǎn)生數(shù)的和的裝置。加數(shù)和被加數(shù)為輸入,和數(shù)與進位為輸出的裝置為半加器。若加數(shù)、被加數(shù)與低位的進位數(shù)為輸入,而和數(shù)與進位為輸出則為全加器。常用作計算機算術(shù)邏輯部件,執(zhí)行邏輯操作、移位與指令調(diào)用。

2017-08-16 12:06:45 17817

17817

8位全加器可由2個4位的全加器串聯(lián)組成,因此,先由一個半加器構(gòu)成一個全加器,再由4個1位全加器構(gòu)成一個4位全加器并封裝成元器件。加法器間的進位可以串行方式實現(xiàn),即將低位加法器的進位輸出cout與相臨的高位加法器的最低進位輸入信號cin相接最高位的輸出即為兩數(shù)之和。

2017-11-24 10:01:45 28520

28520

加法器是產(chǎn)生數(shù)的和的裝置。加數(shù)和被加數(shù)為輸入,和數(shù)與進位為輸出的裝置為半加器。若加數(shù)、被加數(shù)與低位的進位數(shù)為輸入,而和數(shù)與進位為輸出則為全加器。常用作計算機算術(shù)邏輯部件,執(zhí)行邏輯操作、移位與指令調(diào)用。在電子學中,加法器是一種數(shù)位電路,其可進行數(shù)字的加法計算。

2018-01-17 10:42:03 138273

138273

摘要: 數(shù)字相關(guān)器在數(shù)字擴頻通信系統(tǒng)中應用廣泛,受數(shù)字信號處理器件速度限制,無法應用于高速寬帶通信系統(tǒng),在此提出了一種基于流水線加法器的數(shù)字相關(guān)處理算法。該算法最大限度地減少了加法器進位操作

2018-01-18 03:49:01 324

324 加法器是為了實現(xiàn)加法的。即是產(chǎn)生數(shù)的和的裝置。加數(shù)和被加數(shù)為輸入,和數(shù)與進位為輸出的裝置為半加器。若加數(shù)、被加數(shù)與低位的進位數(shù)為輸入,而和數(shù)與進位為輸出則為全加器。常用作計算機算術(shù)邏輯部件,執(zhí)行邏輯操作、移位與指令調(diào)用。

2018-01-29 10:49:50 31304

31304

加法器是產(chǎn)生數(shù)的和的裝置。加數(shù)和被加數(shù)為輸入,和數(shù)與進位為輸出的裝置為半加器。若加數(shù)、被加數(shù)與低位的進位數(shù)為輸入,而和數(shù)與進位為輸出則為全加器。常用作計算機算術(shù)邏輯部件,執(zhí)行邏輯操作、移位與指令調(diào)用。

2018-01-29 11:28:26 82254

82254

一、什么是加法器加法器是為了實現(xiàn)加法的。即是產(chǎn)生數(shù)的和的裝置。加數(shù)和被加數(shù)為輸入,和數(shù)與進位為輸出的裝置為半

2018-03-16 15:57:19 20710

20710

利用4個dsp48e1模塊,實現(xiàn)四路加法器,dsp48e1模塊在手冊中表示比較復雜,找了兩個圖,可以大致看懂他的基本功能。

2018-06-27 09:52:00 2813

2813

加法器是數(shù)字系統(tǒng)中的基本邏輯器件。例如:為了節(jié)省資源,減法器和硬件乘法器都可由加法器來構(gòu)成。但寬位加法器的設(shè)計是很耗費資源的,因此在實際的設(shè)計和相關(guān)系統(tǒng)的開發(fā)中需要注意資源的利用率和進位速度等兩方面的問題。

2019-04-15 08:00:00 4

4 二進制加法器是半加器和全加法器形式的運算電路,用于將兩個二進制數(shù)字加在一起.

2019-06-22 10:56:38 24314

24314

加法器是產(chǎn)生數(shù)的和的裝置。加數(shù)和被加數(shù)為輸入,和數(shù)與進位為輸出的裝置為半加器。若加數(shù)、被加數(shù)與低位的進位數(shù)為輸入,而和數(shù)與進位為輸出則為全加器。

2019-06-19 14:19:17 7423

7423 加法器是產(chǎn)生數(shù)的和的裝置。加數(shù)和被加數(shù)為輸入,和數(shù)與進位為輸出的裝置為半加器。若加數(shù)、被加數(shù)與低位的進位數(shù)為輸入,而和數(shù)與進位為輸出則為全加器。常用作計算機算術(shù)邏輯部件,執(zhí)行邏輯操作、移位與指令調(diào)用

2019-06-19 14:20:39 24786

24786

了ripple進位實現(xiàn)的包數(shù)。加法器邏輯,包括進位,以其真正的形式實現(xiàn),這意味著端部進位可以在不需要邏輯或電平倒置的情況下完成。

2020-05-26 08:00:00 1

1 昨天后仿真四位加法器的時候,想比較一下,超前進位加法器和串行加法器的時候,特意比較了一下那個的延時少一些,居然發(fā)現(xiàn)超前進位加法器延時比串行加法器多,不知道為什么,于是做么一下是不是優(yōu)化的問題。

2020-10-14 16:00:00 13

13 加法器是產(chǎn)生數(shù)的和的裝置。加數(shù)和被加數(shù)為輸入,和數(shù)與進位為輸出的裝置為半加器。若加數(shù)、被加數(shù)與低位的進位數(shù)為輸入,而和數(shù)與進位為輸出則為全加器。常用作計算機算術(shù)邏輯部件,執(zhí)行邏輯操作、移位與指令調(diào)用

2021-02-18 14:40:31 30938

30938

verilog實現(xiàn)加法器,從底層的門級電路級到行為級,本文對其做出了相應的闡述。

2021-02-18 14:53:52 5585

5585

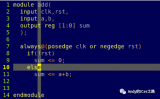

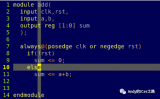

RTL就是一個帶時序的1bit加法器,然后驗證是否功能正確。理論上的正確功能應該是輸入數(shù)據(jù)a和數(shù)據(jù)b之后的下個周期輸出結(jié)果sum等于a+b。

2021-04-15 14:10:10 5254

5254

介紹各種加法器的Verilog代碼和testbench。

2021-05-31 09:23:42 19

19 。二、半加法器的實現(xiàn)在解釋這個半加法器之前,要明白計算機其實就是靠簡單電路集成起來的復雜電路而已,而構(gòu)成這些復雜電路最簡單的邏輯電路就是“與”、“或”、“非”。而在他們的基礎(chǔ)之上進行組合,...

2021-11-11 12:06:03 20

20 電子發(fā)燒友網(wǎng)站提供《4位加法器開源分享.zip》資料免費下載

2022-07-08 09:33:21 3

3 方案介紹四位加法器四位加法器將兩個 4 位二進制數(shù)(十進制表示法中的一個數(shù)字 0-15)相加,適用于晶體管邏輯。數(shù)字通過使用 8 針 DIP 開關(guān)輸入,前 4 個開關(guān)是第一個數(shù)字,下一個直到

2022-12-23 11:53:12 1

1 設(shè)計一個32bit浮點的加法器,out = A + B,假設(shè)AB均為無符號位,或者換個說法都為正數(shù)。

2023-06-02 16:13:19 590

590

有關(guān)加法器的知識,加法器是用來做什么的,故名思義,加法器是為了實現(xiàn)加法的,它是一種產(chǎn)生數(shù)的和的裝置,那么加法器的工作原理是什么,為什么要采用加法器,下面具體來看下。

2023-06-09 18:04:17 3472

3472 加法器可以是半加法器或全加法器。不同之處在于半加法器僅用于將兩個 1 位二進制數(shù)相加,因此其總和只能從 0 到 2。為了提高這種性能,開發(fā)了FullAdder。它能夠添加三個 1 位二進制數(shù),實現(xiàn)從 0 到 3 的總和范圍,可以用兩個輸出位 (“11”) 表示。

2023-06-29 14:27:35 5470

5470

半加法器是一種執(zhí)行二進制數(shù)相加的數(shù)字電路。它是最簡單的數(shù)字加法器,您只需使用兩個邏輯門即可構(gòu)建一個;一個異或門和一個 AND 門。

2023-06-29 14:35:25 4645

4645

電子發(fā)燒友網(wǎng)站提供《4位加法器的構(gòu)建.zip》資料免費下載

2023-07-04 11:20:07 0

0 鏡像加法器是一個經(jīng)過改進的加法器電路,首先,它取消了進位反相門;

2023-07-07 14:20:50 1189

1189

前段時間和幾個人閑談,看看在FPGA里面實現(xiàn)一個Mem加法器怎么玩兒

2023-10-17 10:22:25 279

279

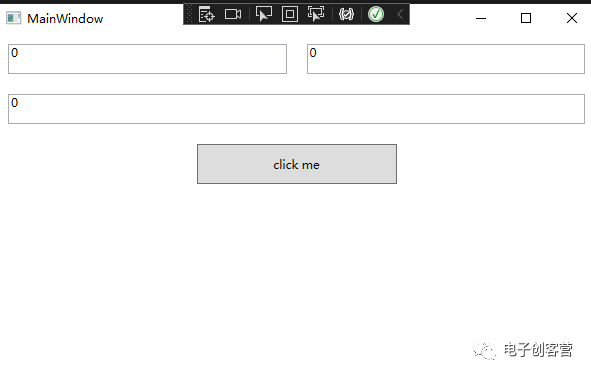

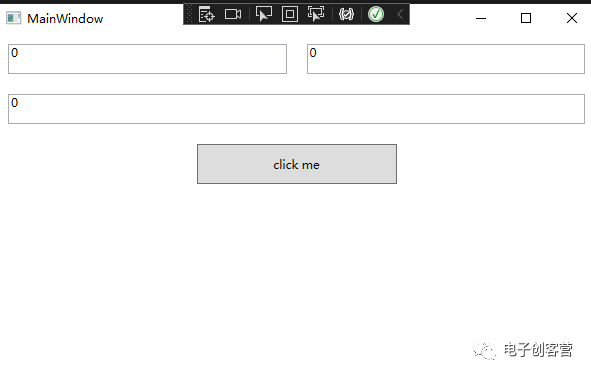

使用MVVM框架來實現(xiàn)一個簡單加法器。最終效果如下,點擊按鈕可以對上面兩個文本框中的數(shù)字進行相加得出結(jié)果顯示在第三個文本框中。重點在于看mvvm框架下程序該怎么寫。使用CommunityToolkit.Mvvm框架,通過nuget進行安裝。

2023-10-24 14:23:01 194

194

電子發(fā)燒友App

電子發(fā)燒友App

評論