隨著5G 國際標準的出爐,Polar碼順利入選控制信道編碼方案,世界上各大通信設備生產商便開始基于標準設計基站和終端產品。

我們明白,從純算法到實現工程化,中間還有很長一段路要走。一方面,我們需要保證算法的性能良好;另一方面,便于硬件實現。本文將從Polar碼編碼角度,介紹Xilinx的Polar Encoder/Decoder IP核的使用方法。

按理說,我們應該分析Polar碼的編碼原理和算法構造,然而,專業性實在太強,定義、定理和公式及推導,以及算法性能比較及硬件實現方案,足夠寫出一篇碩士論文,甚至博士論文。因此,筆者不打算詳細講,包括里面的詳細推導也需要花很長的時間,有興趣研究這個方向的同學,可以多找幾篇質量較好的論文研讀。

目前也有一些碩博論文在研究和實現Polar編、譯碼,相信今后一段時期,還會有相關的研究成果問世。因此,若你還未走出象牙塔,擁有足夠的時間去探索,去發現不一樣的東西。若已經在工作崗位上,并正從事相關的研究設計工作,那么,筆者很樂意請教交流。比如,在開發過程中,會遇到哪些坑,有哪些需要注意,提高工作效率和縮短開發周期。

本文是筆者的一個學習筆記,主要是利用Xilinx公司的Polar IP核進行應用開發,并介紹MATLAB軟件中的關于Polar編碼的函數。

由于所用的IP手冊通常是需要購買了Xilinx公司或第三方廠家的IP 核才會提供相關的文件資料,因此,想獲取公開的關于5G信道編碼的IP核資料比較難。

先介紹干貨,關于資料的問題,在后面談。

Polar IP介紹

Xilinx提供的Polar Encoder/Decoder IP v1.0支持Polar編碼和譯碼。Polar碼可配置,基于逐塊使用。關于該IP的詳細介紹,可參考文獻[1]-[2],本節做簡要介紹。該IP支持的器件:UltraScale、UltraScale+和7系列。注意,在本文中,塊是由編碼器或解碼器處理的數據基元單元的通稱。碼字是已編碼塊的特定形式,在討論用于生成它的代碼參數時使用。

根據IP產品指南,Polar Enocder/Decoder IP核,在400MHz時鐘頻率下,最高吞吐量如下:

Polar解碼器:>80Mb/s(N=1024,K=200)

Polar編碼器:>700Mb/s( N=1024,K=200)

這里,K是輸入信息bit長度,N是輸出碼字長度。

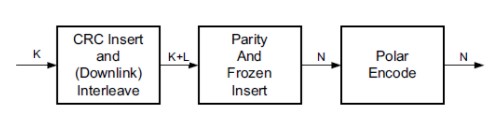

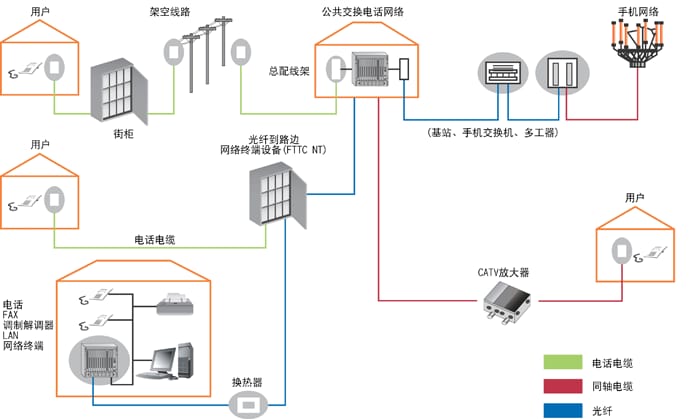

前向糾錯(FEC)碼(例如Polar碼)提供了一種方法去檢測核識別糾正不可靠或嘈雜通信信道上的數據傳輸錯誤。根據5G NR物理層協議,Polar碼的編碼過程,如圖所示。

前級的傳輸塊信息bit,插入CRC校驗,下行鏈路還需插入交織,奇偶校驗及凍結bit插入(非必須),再送入編碼器進行編碼。

特性總結:

Polar Encoder/Decoder IP核是一個高度靈活的軟判決實現為Polar碼提供以下特性。

Decoder執行列表大小為8的串行抵消列表(SCL)解碼,根據3GPP TS 38.212 V15.1.1,通過奇偶校驗和/或CRC比特來增加比特。

能夠基于逐塊或傳輸指定輸入和輸出數目。

?通過AXI-Lite接口最高支持配置128個代碼。

?逐塊選擇代碼。

碼字大小從N = 32到N = 1024,K從2到N,交織時Kmax為140。

作為編碼器,內核接受K?bit信息,并輸出N個編碼bit。作為一個解碼器,內核接受N個軟值對數似然比(LLR),并輸出K個硬判決bit。

解碼器接受8bit軟值LLR輸入,并假設飽和對稱。

僅支持按順序塊執行。

?輸入輸出寬數據接口。

單獨的輸入和輸出流允許提供控制參數和狀態逐塊地進行。

應用領域:

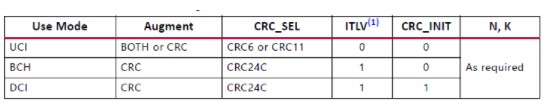

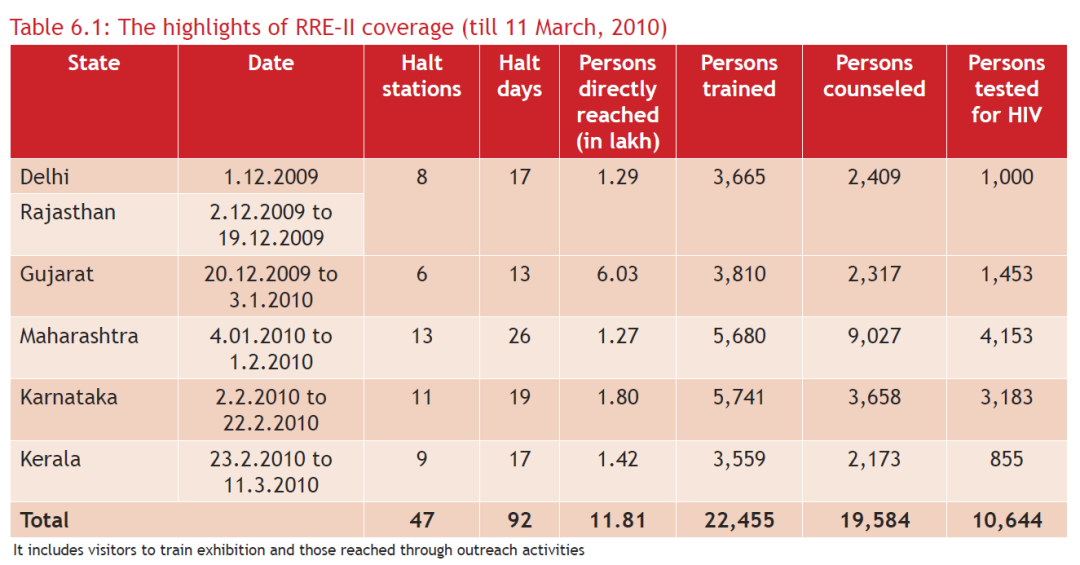

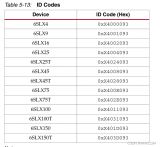

例如5G無線,參考3GPP TS 38.212 V15.1.1 Multiplexing and channel coding(Release 15),支持DCI、UCI、和BCH。Polar使用模式設置,如下表所示。

注意,這個表很重要,很重要,特別是對于使用該IP核進行應用開發的朋友而言。

產品規格

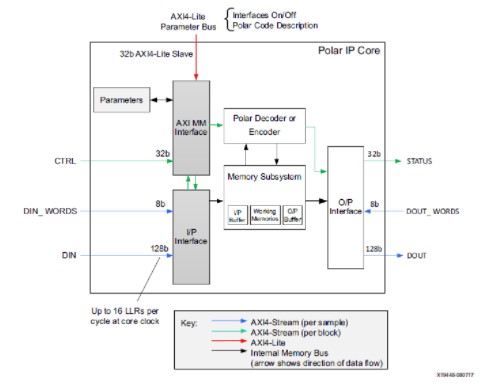

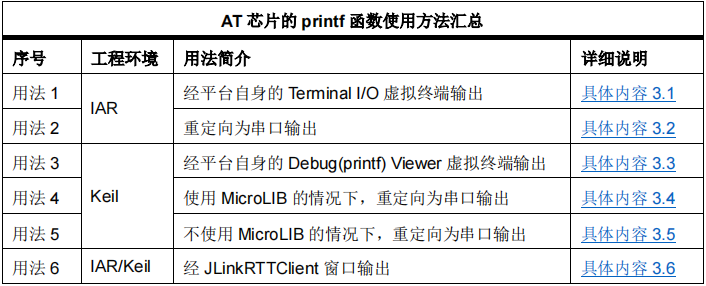

Polar編碼器/解碼器Core的框圖如圖所示:

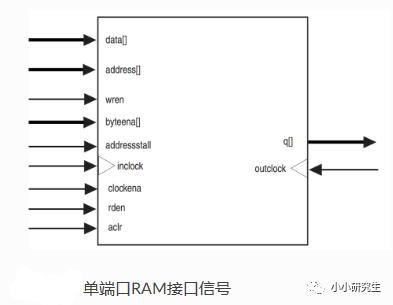

該Core使用AXI接口。AXI4-Lite存儲器映射總線用于參數(例如Polar碼定義)持續緩存多個塊,AXI4-Stream接口用于逐個樣本提供數據(例如,DIN)基于逐塊的配置(例如,CTRL)。這些接口處理提供數據外,還提供握手信號。

每個塊通過數據輸入接口(DIN)在多個周期內輸入。在每個周期中傳輸的數據率由一個單獨的數據流(DIN_WORDS)來設置,其中DIN上的每個事務都有一個值。輸出是以類似的方式在DOUT輸出流上生成,在輸入數據流DOUT_WORDS上指定了傳輸的數據量。

對于每個塊,在控制(CTRL)輸入流上需要一個輸入,指定要使用的代碼和用戶提供的ID字段。每個數據塊需要一個控制字,數據輸入暫停,直到相關的控制字可用為止。當解碼(或編碼)時,DOUT接口輸出數據伴隨著狀態(STATUS)輸出接口上的狀態字一起輸出。

該圖包含了非常豐富的信息,對于從事IC設計或FPGA開發的朋友來說,這樣的框圖看到過太多太多,我們在論文里或者設計報告里,經過要這樣畫一個框圖。

這里面包含了接口、內部功能單元及必要的圖注。通常,箭頭方向指明數據流向,左邊是輸入端口,右邊是輸出端口,但不是絕對。

為便于集成和操作,IP核通常采用業界標準接口,例如上圖中給出的AXI4-Stream、AXI4-Lite等。

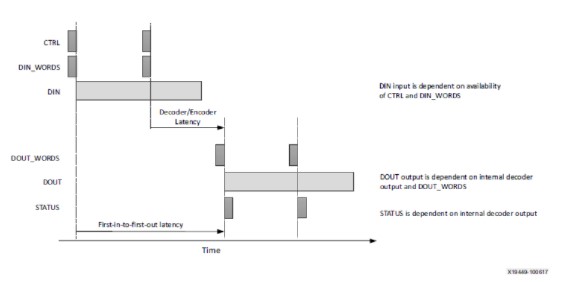

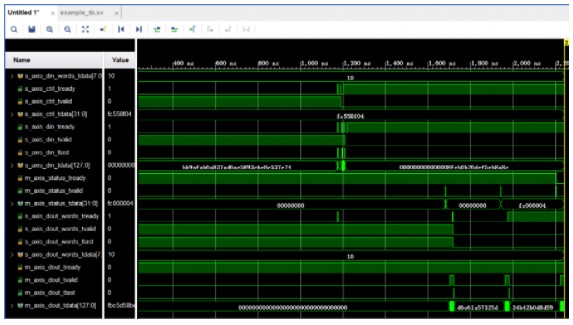

所有AXI4-Sream接口包含用于流控的valid 和ready握手。上圖中,數據依賴關系,如下圖所示。

根據圖示可知,輸入DIN上數據輸入依賴于CTRL和DIN_WORDS,DOUT輸出的數據依賴于內部解碼器輸出和DOUT_WORDS。CTRL的輸入與DIN_WORDS的相關輸入之間存在延時,并且DIN被接受,需要通過通道上的tready來斷言。同樣,DIN_WORDS與DIN也存在延時。如果要最小化DIN上的延時,那么CTRL和DIN_WORDS應該提前提供。同樣,在輸出端,為了避免輸出DOUT延遲,若有必要,應該盡早驅動DOUT_WORDS。接口有淺緩存,在CTRL上提供相關的塊控制之前,DIN和DIN_WORDS上在允許輸入少量數據。

當我們拿到這樣的IP指南時,首先就要先看看這個IP能夠實現什么功能,適用于哪種協議或標準,IP核端口及信號定義,以及重要的注釋信息。

對于通用的FIFO、RAM等,會用即可。難點在于根據某些標準協議或算法而有針對性開發的IP核,通常應用起來也要花一些時間去看文檔,并了解背后的協議和算法。例如,對于應用于5G信道編譯碼的Polar IP和LDPC IP,涉及標準協議和一系列參數配置,并不像使用一個FIFO那樣簡單。

更多關于端口描述和寄存器空間的內容,請參閱參考文獻[2]。這里不再占用篇幅和時間碼字了。

Polar Encoder IP應用

本節內容,是大家最為關心的,拿到資料后,我們初步了解了這個IP是干嘛的,有什么特性,有哪些端口,如何利用該IP進行設計,流程是什么,怎么仿真驗證。

這里,假設你已經看完了產品指南的資料,你已經迫不及待準備開始動手了。

然而,你卻迷惑了:我有Polar 編解碼 IP的license嗎?我該用哪個版本的Vivado設計套件?我如何去寫一個testbench來驗證,我的參考模型在哪里?

關于Polar IP license的問題,解決辦法有兩個:

(1)若你已經入職,那么找你項目組的負責人,他會想辦法去購買,買回來就可以用了;

(2)若你還在求學,然而導師想讓你研究Polar碼,要自己動手去進行硬件實現,你想找個參考和性能對比對象,然鵝沒有足夠的資金去購買一個IP,并且很不值得,那么你可以去Xilinx官網申請一個評估版的license進行試用。

然后進去申請一個免費的評估license,可以搜索你想申請的license。一般需要你注冊,并且提前準備好你主機的MAC地址,以備填寫信息所用。

關于Vivado設計套件版本的問題,看哪個版本支持5G等開發就用哪個,筆者用的是Vivado2018.3。

關于如何寫testbench的問題,這個問題確實很重要,也有很多參考書和博客在比較詳細的介紹。前面的文章《SystemVerilog與功能驗證方法學》提到過關于testbench驗證平臺的問題。我們要注意的是,測試激勵的產生以及對DUT輸出結果的檢測。首先為DUT提供輸入信號,用邏輯和存儲文件產生必要的信號;其次,要注意各端口測試激勵的時序關系,應根據DUT的需求進行設計;最后,對于DUT的輸出,我們可以進行寫文件操作,保留仿真產生的結果,便于數據分析。

對于參考模型,我們常用的就是MATLAB鏈路算法模型。例如對于Polar的編碼,MATLAB中提供了庫函數nrPolarEncode,該函數是根據5G NR標準協議編寫的,可直接調用。

萬事俱備,只欠東風。我們把申請好的license加入到license管理器中對應的路徑后,更新確認是否可用。

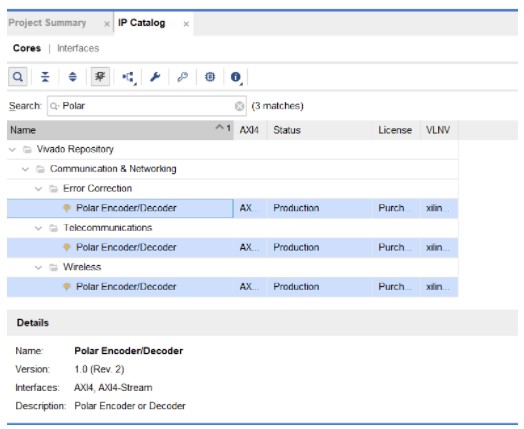

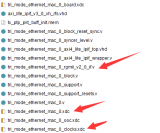

新建一個工程,通過Vivado的IP目錄,我們輕松找到Polar IP核:

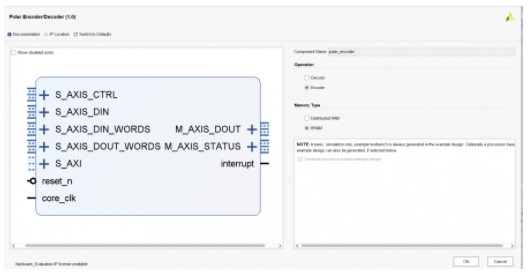

然后進行簡單的配置,例如選擇進行編碼,存儲資源類型可以選DRAM或BRAM。“OK”后導出IP核,綜合方式可以選全局或者OOC,默認是OOC方式。

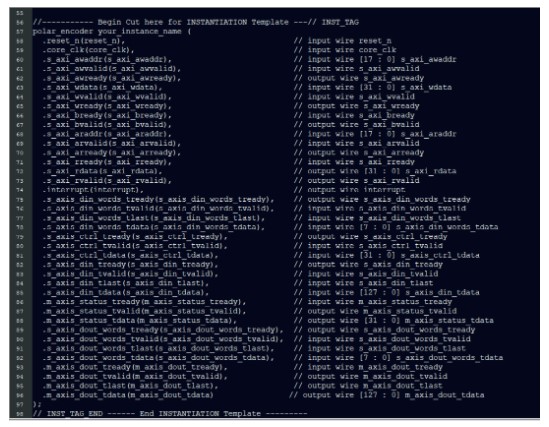

然后我們將IP的例化文件復制粘貼到工程的v文件中,并定義好集成的模塊名。

當我們例化好IP 核后,將必要的input和output 端口通過頂層文件進行定義。

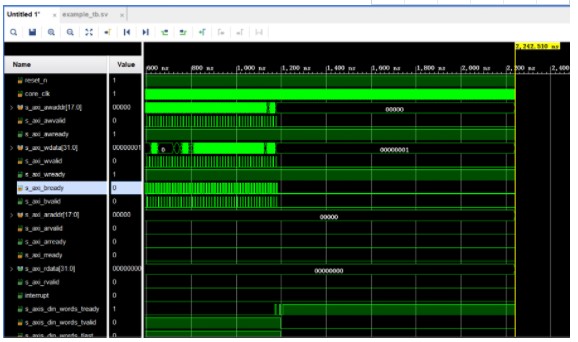

接下來,就著手編寫testbench了。當你不知道怎樣去寫一個令人滿意的驗證IP 的testbench時,你可以在IP sources欄,選擇該IP,右鍵去選擇“Open IP Example Design”打開IP的例程,查看例程的testbench是怎樣寫的,并且可以直接進行仿真。當然,你也可以自己編寫一個testbench。

?

跑個例程是很簡單,然鵝,你的目標可不是跑個例程就結束了。

這里在應用Polar 編解碼IP核時,最重要的是什么呢?其實是根據實際情況去配置參數寄存器。

當時筆者也是沒搞懂這個寄存器到底應該怎樣去配置,才能得到想要的結果,每次以為已經按照指南操作了,可是編碼結果就是和MATLAB中的結果對不上,對不上,你絕望嗎?

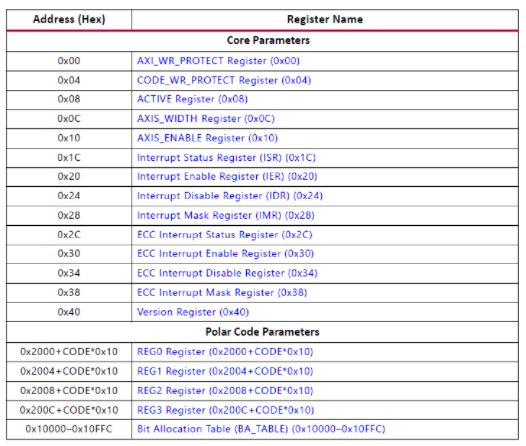

沒錯,筆者要說的就是下面這個寄存器空間。

當仔細看完IP指南后,筆者還是很懵的。直到嘗試了好幾天,才終于搞定了。期間,甚至去Xilinx論壇提問了,當我已解決后的某個周末,論壇回郵件了。當然我只是問了一個不是最重要的問題,而是一個非常普通的不算是問題的問題,因為指南里其實已經說了,只是當時已經懷疑自我了。

在指南里,上面這個表的每一個地址及對應的配置參數,都有說明,然鵝,當你看到上表的最后一行,你會很困惑:這個位分配表我哪里知道?!

當初筆者天真的以為,假如按照輸出的碼字全是信息bit,自己去造一個位分配表,然鵝,還是太年輕。

仿真過幾次,不對啊。

然后又去Xilinx官網找資料,找到了參考文獻[3],并且通過文中的連接,獲取了一份重要的C模型和MATLAB模型的代碼,這個文檔就是介紹如何去造位分配表。而C模型和MATLAB代碼,正是在下苦苦尋找的位分配表的產生來源。

要說,這個位分配表,是依據協議來產生的,IP核利用了寄存器映射,指明輸出碼字每一位的類型:凍結位、信息位、CRC位、奇偶校驗位。

依據這個MATLAB代碼,筆者根據實際參數進行配置,然后產生了位分配表,再把這個表寫入MIF文件,通過testbench讀取并寫入IP核的參數總線。最后,編碼輸出的結果終于和MATLAB對上了!

注意,MATLAB的版本最好是2019a/b及以上。

對比結果就不貼圖了,本來這篇水文是不能寫出來的,在不涉密的情況下,我只能這么水水的描述一下,以饗讀者。

在整個Polar Encoder/Decoder IP核的開發應用中,需要注意以下幾點:

(1)確定參數配置方式,最好采用可編程方式配置;

(2)對于DIN_WORDS、CTRL、STATUS、DOUT_WORDS端口輸入,要結合前文提到的數據接口依賴關系;

(3)對于不同的信道(如PBCH,PDCCH),IP核的配置不太一樣,仔細看IP指南和本文提到的很重要很重要的那個圖表。

如果你有足夠的時間,完全可以自己動手去開發一個Polar IP核,掛在網上,說不定可以賣出好價錢。

今天就到此為止,本文介紹得不是很詳細,但筆者遇到的那些坑,基本上指出來了,希望對讀者朋友有幫助。

審核編輯:劉清

?

電子發燒友App

電子發燒友App

評論