來自伊利諾伊大學(xué)厄巴納-香檳分校(UIUC)的 Grainger 工程學(xué)院的研究人員與柔性電子制造商?PragmatIC Semiconductor合作,獲得了首個商業(yè)上可行的柔性塑料微處理器。這些 FlexiCore 芯片只需不到一分錢,就能制造出低成本的智能消費產(chǎn)品。此外,靈活的技術(shù)使芯片能夠滿足這些應(yīng)用中的尺寸限制。

“你可以將處理器放在繃帶上以檢測傷口是否正在愈合,或者將它們添加到消費品包裝中以跟蹤供應(yīng)鏈的進展,”UIUC 協(xié)調(diào)科學(xué)實驗室的電氣和計算機工程教授兼研究員 Rakesh Kumar 說,在一份聲明中。“挑戰(zhàn)在于創(chuàng)造一種處理器,它既可以廉價生產(chǎn),又足夠靈活,即使在我們的身體、包裝或啤酒瓶的不平整表面上也能貼身貼合。”

研究人員不使用硅,而是決定使用塑料作為其芯片的基礎(chǔ)。FlexiCore 建立在由銦鎵鋅氧化物 (IGZO) 制成的薄膜晶體管 (TFT) 上,這種半導(dǎo)體材料即使在彎曲時也能工作,并且與塑料兼容。

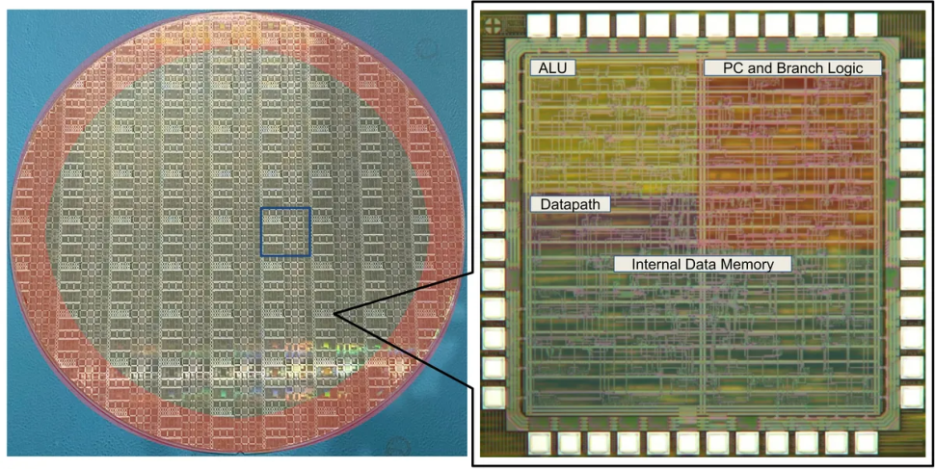

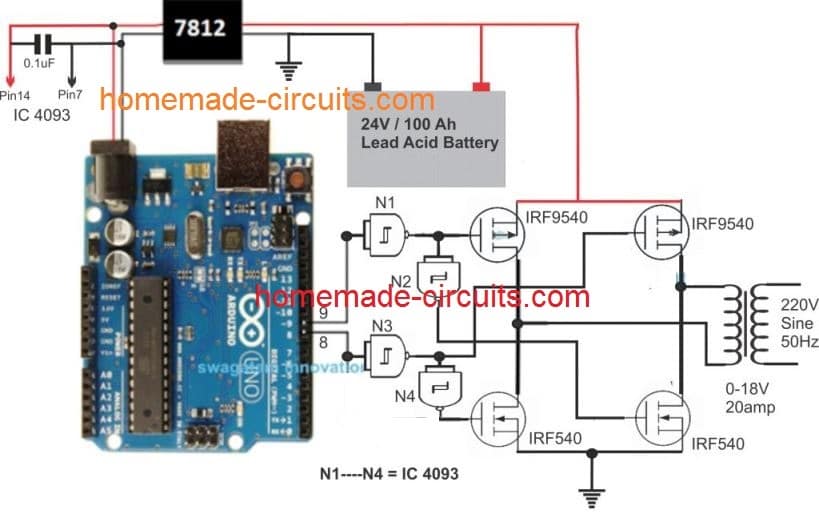

FlexiCore4 芯片采用 200 毫米晶圓。。(來源:伊利諾伊大學(xué)厄巴納-香檳分校)

聚酰亞胺已被證明是一種有彈性的柔性基材,該項目的電氣和計算機工程專業(yè)研究生 Nathaniel Bleier 說。“TFT是無機的——由銦、鎵、鋅和氧制成——沉積在包含四個金屬層的聚酰亞胺基板上。該工藝是一種光刻工藝,它使用一系列沉積、圖案化和蝕刻步驟。”

UIUC 團隊測試了 4 位和 8 位處理器,發(fā)現(xiàn) 4 位處理器產(chǎn)生了 81% 的良率,這足以讓芯片以不到一美分的價格制造出來。4 位處理器有 2,104 個器件(晶體管和電阻器),比去年宣布的名為 PlasticArm的塑料 Arm 處理器上的 56,000 多個器件要少得多。

研究人員在 3 V 和 4.5 V 下以 12.5 kHz 的頻率測試了內(nèi)核。內(nèi)核平均消耗 3.9/4.9 mW。FlexiCore4 和 FlexiCore8 內(nèi)核的尺寸分別為 5.56 mm 2和 6.05 mm 2。兩者都在晶圓上進行了測試并且未封裝。

Bleier 說,以 12.5 kHz 的頻率測試內(nèi)核是測試設(shè)備的一個限制。

“我們相信我們可以更快地運行內(nèi)核,并且提高時鐘速度對功耗的影響最小,而功耗絕大多數(shù)是靜態(tài)功耗,”他說。

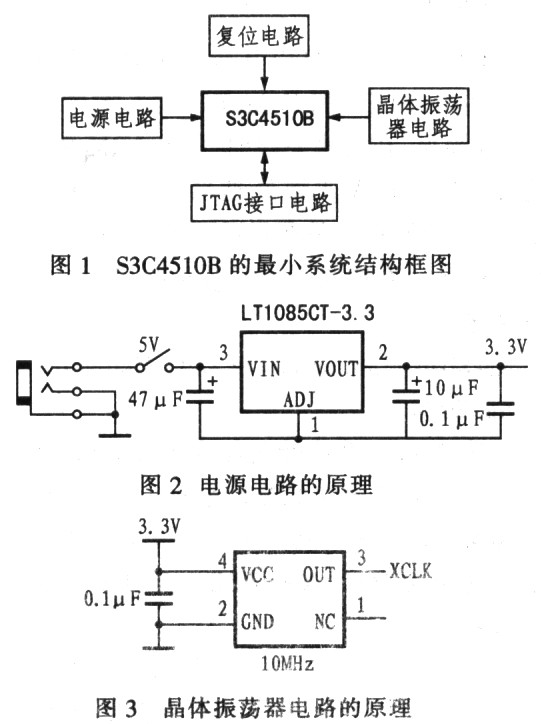

為什么選擇 4 位和 8 位處理器?“我們這項工作的目標(biāo)是表明,柔性電子產(chǎn)品能夠?qū)崿F(xiàn)低成本微處理器,這反過來又允許計算滲透到目前由于保形性、薄度和成本要求而尚未出現(xiàn)計算擴散的領(lǐng)域. 這些領(lǐng)域包括快速消費品的包裝;創(chuàng)可貼等低端保健品;一次性食品傳感器;以及用于森林、農(nóng)業(yè)和環(huán)境監(jiān)測的傳感器。

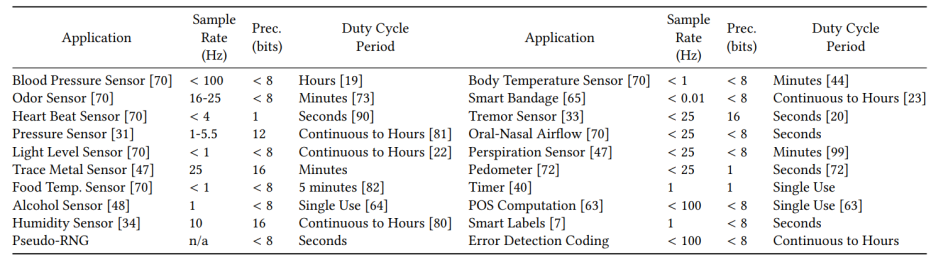

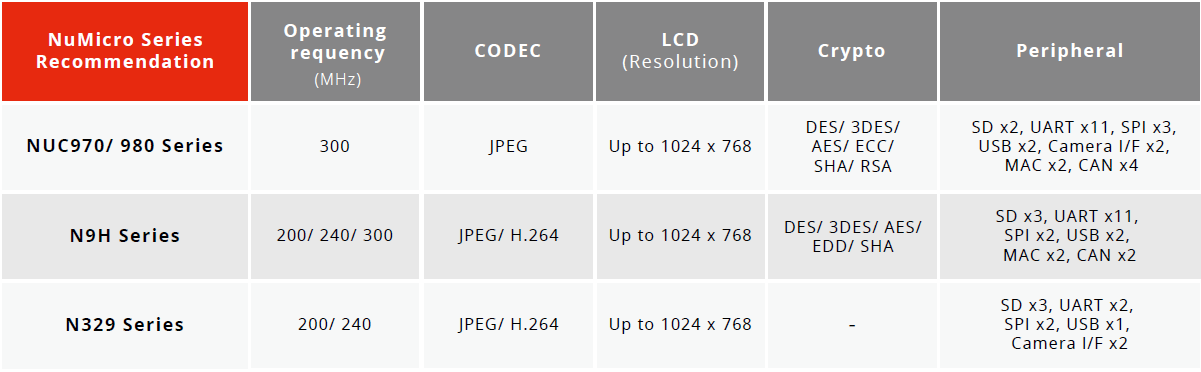

“能夠滿足這些領(lǐng)域要求的低成本、靈活的處理器需要一個小面積、高產(chǎn)量的微處理器,”Bleier 補充道。“此外,對域應(yīng)用程序的分析 [見下表] 表明,這些‘靈活應(yīng)用程序’中的大多數(shù)都需要不超過 8 位的數(shù)據(jù)精度,事實上,4 位對許多人來說甚至是多余的。”

FlexiCore 柔性塑料微處理器的示例應(yīng)用及其性能要求。。(來源:伊利諾伊大學(xué)厄巴納-香檳分校)

但也有很大的挑戰(zhàn)。Bleier 說,設(shè)計一個既足夠小又足夠強大的處理器“對真正的計算工作有用一直是開發(fā)低成本、靈活處理器的最大挑戰(zhàn)”。

他補充說,處理器的單位成本與處理器的尺寸成超線性比例,材料成本與處理器尺寸成正比。“因此,更大的處理器每個內(nèi)置處理器的成本更高,并且需要構(gòu)建更多的處理器來滿足生產(chǎn)目標(biāo)。這意味著要獲得超低價格,我們需要一個非常小的處理器,但處理器仍然需要能夠支持需要計算的靈活應(yīng)用程序。”

其他原型

去年發(fā)布了一些具有競爭力的柔性塑料微處理器,包括 Arm 的 PlasticArm 和imec 的 8 位 6052 塑料處理器。但是原型之間有幾個關(guān)鍵的區(qū)別。(有關(guān)其他比較,請參閱 UIUC/PragmatIC Semiconductor報告。)

Bleier 說 UIUC 的項目在幾個基本方面與 Arm 的工作不同:“首先,我們的項目真正是一個能夠執(zhí)行其 ISA 中編寫的任意程序的微處理器。我們在硅后測試和驗證中利用了這一事實,我們使用超過 100,000 條指令對每個芯片進行嚴(yán)格測試,這些指令來自對每條芯片路徑進行定向和隨機測試。因此,當(dāng)我們說核心有效時,我們相信它確實有效。

“另一方面,Arm 原型執(zhí)行單個程序;因此,測試包括檢查它是否正確執(zhí)行了該程序,”他補充道。

Bleier 說,就 imec 原型而言,它更像是 FlexiCore,“因為他們設(shè)計了一個可以執(zhí)行任意程序的處理器”。

然而,imec 和 Arm 項目都采用了為硅設(shè)計的現(xiàn)有架構(gòu),UIUC 的研究人員“認(rèn)為這是一個錯誤”。

Bleier 解釋說:“最初的 MOS 6502 建立在 8 微米技術(shù) [工藝] 節(jié)點上——即比這些靈活工作中使用的大 10 倍——但仍可以在低兆赫頻率范圍內(nèi)工作。此外,MOS 6502 可以尋址 64 KB 的內(nèi)存——ARMv6m 可以尋址 4 GB 的內(nèi)存。盡管如此,Arm 的 SoC 中僅包含大約 128 B 的內(nèi)存。在柔性電子產(chǎn)品中,目前不需要能夠處理大量(甚至微不足道)的內(nèi)存,因為此時只能構(gòu)建少量的柔性內(nèi)存。”

研究人員關(guān)注的另一個問題是支持設(shè)計的微架構(gòu)。他們質(zhì)疑他們的多周期設(shè)計方法,特別是對于電池或采集器供電的系統(tǒng)。

“雖然所有商業(yè) ARMv6m 內(nèi)核都是流水線的,但 PlasticArm 與 6502 一樣,使用多周期設(shè)計來最小化面積——多周期設(shè)計允許結(jié)構(gòu)的時間復(fù)用,”Bleier 說。“這意味著每條指令需要多個周期才能執(zhí)行。這是一種可接受的技術(shù)折衷,例如以動態(tài)功率為主的傳統(tǒng)硅技術(shù)。但這種靈活的技術(shù)以靜態(tài)功耗為主導(dǎo),這意味著增加每條指令的周期數(shù)相當(dāng)于將執(zhí)行一條指令所需的能量增加一倍、三倍、四倍等。”

UIUC 團隊仍在努力實現(xiàn)三個關(guān)鍵目標(biāo):Bleier 說,研究人員希望啟用完整的系統(tǒng),從而為靈活的應(yīng)用程序提供機密和經(jīng)過身份驗證的通信。他們還希望開發(fā)電路和微架構(gòu)功耗降低解決方案,并在柔性電子產(chǎn)品的背景下探索間歇性計算(即在出現(xiàn)電源故障的情況下進行計算)。

審核編輯 黃昊宇

電子發(fā)燒友App

電子發(fā)燒友App

評論