國產USB轉單串口CH9102,PIN替代CP2101/CP2102/CP2104/CP2109

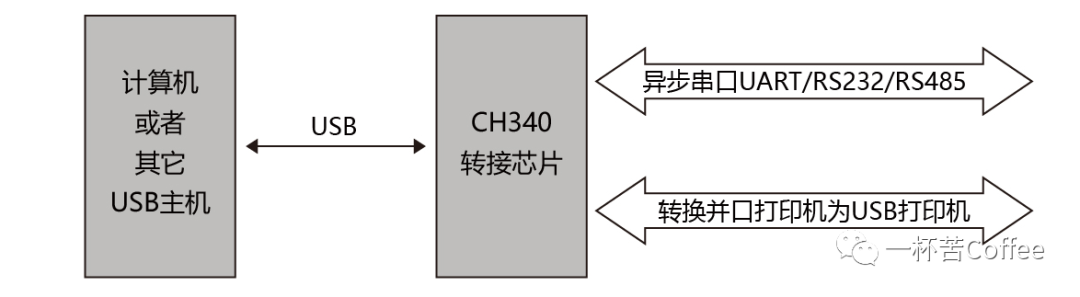

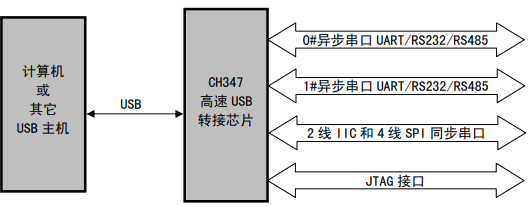

CH9102 是一個 USB 總線的轉接芯片,實現 USB 轉異步串口。提供了常用的 MODEM 聯絡信號,用

于為計算機擴展異步串口,或者將普通的串口設備或者 MCU 直接升級到 USB 總線。

特點;

全速 USB 設備接口,兼容 USB V2.0。

內置固件,仿真標準串口,用于升級原串口外圍設備,或者通過 USB 增加額外串口。

計算機端 Windows 操作系統下的串口應用程序完全兼容,無需修改。

支持免安裝的操作系統內置 CDC 類驅動程序或者多功能高速率的 VCP 廠商驅動程序。

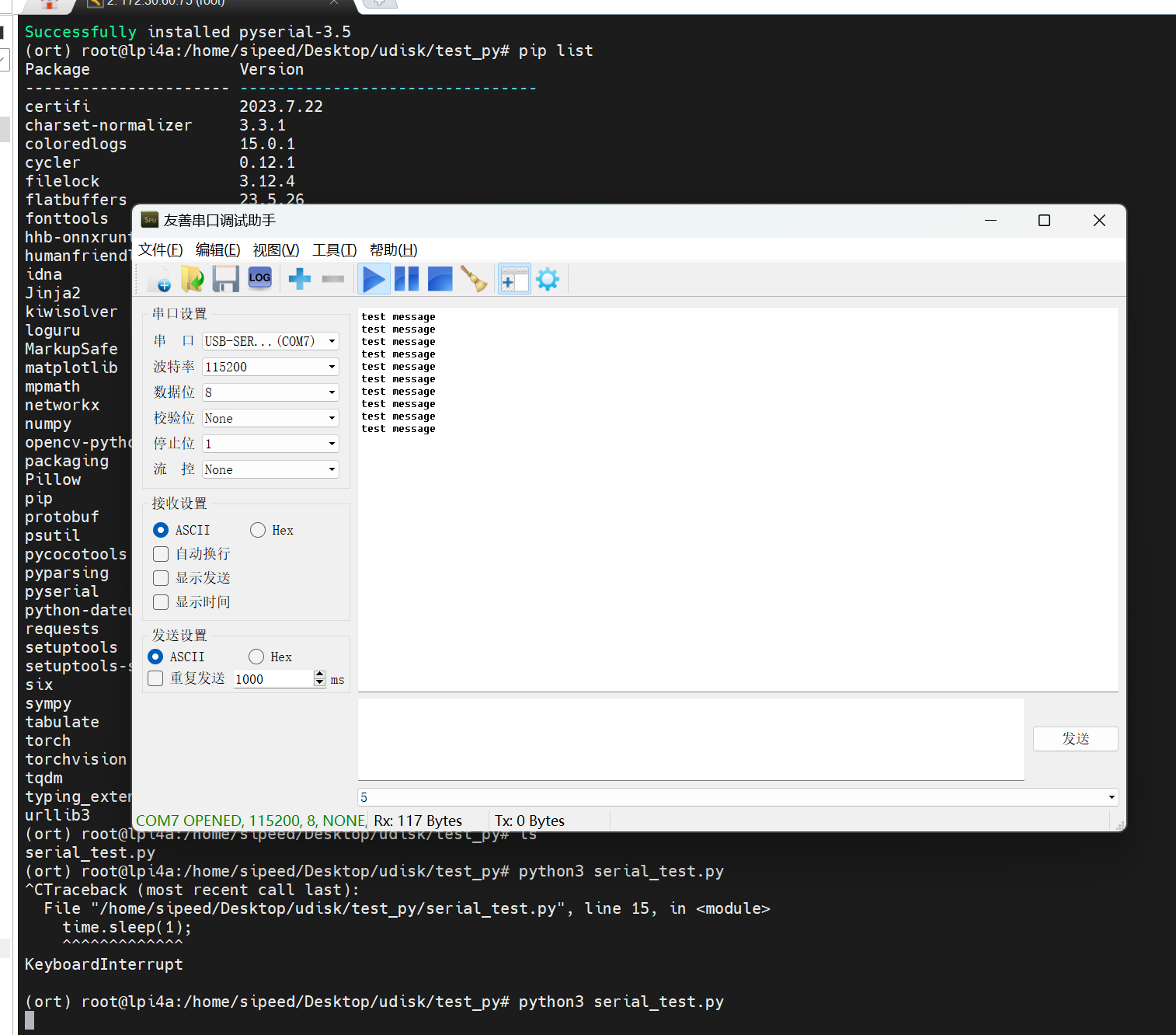

硬件全雙工串口,內置獨立的收發緩沖區,支持通訊波特率 50bps~4Mbps。

串口支持 5、6、7 或者 8 個數據位,支持奇校驗、偶校驗、空白、標志以及無校驗。

支持常用的 MODEM 聯絡信號 RTS、DTR、DCD、RI、DSR、CTS。

支持 CTS 和 RTS 硬件自動流控。

支持半雙工,提供正在發送狀態 TNOW 支持 RS485 切換。

USB 端支持 5V 電源電壓和 3.3V 電源電壓。

CH9102F 串口 I/O 獨立供電,支持 5V、3.3V、2.5V、1.8V 電源電壓。

CH9102X 串口 I/O 支持 3.3V 信號。

內置上電復位,內置時鐘,無需外部晶振。

CH9102F 內置 EEPROM,可配置芯片 VID、PID、最大電流值、廠商和產品信息字符串等參數。

芯片內置 Unique ID(USB Serial Number)。

提供 QFN24 和 QFN28 無鉛封裝,兼容 RoHS。

電源與功耗;

CH9102 芯片有 3 個電源端,內置了產生 3.3V 的電源調節器。VDD5 是電源調節器的輸入端,V3

是電源調節器的輸出端和 USB 收發器及內核電源輸入,VIO 是 I/O 引腳電源。

CH9102 芯片支持 5V 或者 3.3V 電源電壓,V3 引腳應該外接容量為 0.1uF 左右的電源退耦電容。

當使用 5V 工作電壓(大于 3.8V)時,VDD5 引腳輸入外部 5V 電源(例如 USB 總線電源),由內部電源

調節器于 V3 引腳產生 3.3V 電源,用于 USB 收發器。當使用 3.3V 或更低工作電壓(小于 3.6V)時,

V3 引腳應該與 VDD5 引腳相連接,同時輸入外部的 3.3V 電源,V3 引腳仍需外接電源退耦電容。

+

-CH9102 手冊

4

CH9102 芯片的 VIO 引腳用于為串口 I/O 和 RST 引腳提供 I/O 電源,支持 1.8V~5V 電源電壓,VIO

應該與 MCU 等外設使用同一電源。UD+和 UD-及 VBUS 引腳使用 V3 電源,不使用 VIO 電源。

CH9102 芯片自動支持 USB 設備掛起以節約功耗。在 USB 掛起狀態下,如果 I/O 輸出引腳沒有外

部負載,I/O 輸入引腳處于懸空(內部上拉)或者高電平狀態,那么 VIO 電源將不消耗電流。另外,

當 V3 和 VDD5 失去供電處于 0V 電壓時,VIO 消耗電流情況同上,VIO 不會向 VDD5 或者 V3 倒灌電流。

VBUS 引腳應該連接到 USB 總線的電源,當檢測到失去 USB 電源時,CH9102 芯片將關閉 USB 并睡

眠(掛起)。VBUS 引腳內置的下拉電阻可以由計算機端軟件通過設置串口 MCR 寄存器中的 OUT1 信號

控制(SERIAL_IOC_MCR_OUT1),OUT1 無效時開啟下拉電阻(默認狀態),OUT1 有效時關閉下拉電阻。

當 VBUS 引腳串接電阻后用于通過 PMOS 控制 VIO 電源時,CH9102 提供了 VIO 低壓保護機制。在

關閉 VBUS 下拉電阻期間,如果檢測到 VIO 電壓低于約 1.4V,那么 CH9102 將自動在 VBUS 引腳吸收約

300uA 放電電流,直到 VIO 電壓升高后結束該放電電流,并自動開啟下拉電阻。

注:CH9102F 和 CH9102X 的底板是 0#引腳 GND,是可選但建議的連接;其它 GND 是必要連接。

CH9102X 的 VIO 引腳與 V3 引腳已在內部短接。

CH9102 的 USB 收發器按 USB2.0 全內置設計,UD+和 UD-引腳不能串接電阻,否則影響信號質量。

審核編輯 黃昊宇

電子發燒友App

電子發燒友App

評論