)。該器件采用 8 線 15 Gbps JESD204B 數(shù)據(jù)輸入端口、高性能片內(nèi) DAC 時鐘倍頻器和數(shù)字信號處理功能,適用于單頻段和多頻段直接到射頻 (RF) 無

2024-02-27 19:19:55

。該子卡提供DDC I2C緩沖和CEC數(shù)字緩沖。HDMI子卡與Altera示例設(shè)計兼容。Intel FMC HDMI子卡設(shè)計用于搭配Bitec HDMI IP內(nèi)核

2024-02-27 11:58:21

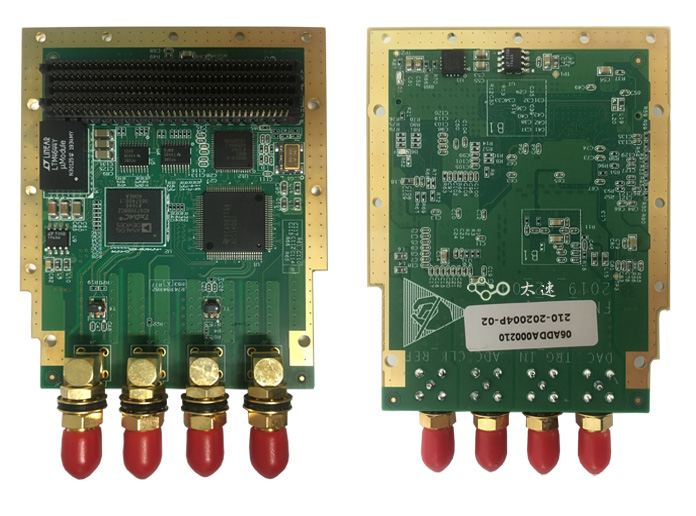

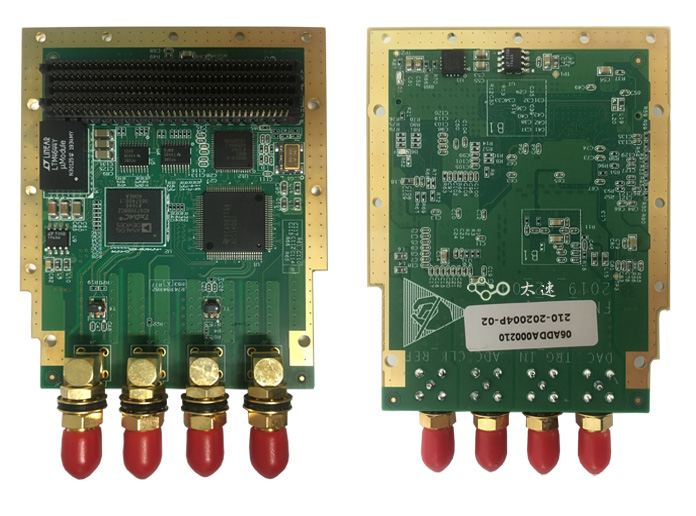

AD9162-FMC-EBZ:高性能、高精度的射頻收發(fā)器評估板AD9162-FMC-EBZ是一款高性能、高精度的射頻收發(fā)器評估板,用于評估AD9162收發(fā)器的性能。AD9162是一款高性能的直接

2024-02-16 17:56:52

信號的應(yīng)用。該套件具有 8 通道、24.75 Gbps JESD204C 或 15.5 Gbps JESD204B 數(shù)據(jù)接收器 (JRx) 端口、片內(nèi)時鐘乘法器和數(shù)

2024-02-16 17:16:40

數(shù)進行權(quán)衡。支持 8b/10b 和 64b/66b 數(shù)據(jù)編碼方案。64b/66b 編碼支持前向糾錯 (FEC),可改進誤碼率。此接口向后兼容 JESD204B 接收器。

無噪聲孔徑延遲調(diào)節(jié)

2024-01-31 15:22:55

VS018M1是一款雙路4K采集卡,兩路高清輸入,4K輸入環(huán)出,靈活的擴展能力,1080P高清采集,混音功能;零延遲環(huán)出4K/60游戲畫面,同時讓你順暢推流1080P/60Hz畫面,到

2024-01-23 11:11:07

APROM了?

2.P356頁流程圖D入口右邊,Page 0 is mapping to LDROM.與P348表格CBS=00時不符.

3.CBS=11或01與CBS=10或00時的區(qū)別。P355流程圖

2024-01-16 07:17:39

問:什么是8b/10b編碼,為什么JESD204B接口需使用這種編碼?

答:無法確保差分通道上的直流平衡信號不受隨機非編碼串行數(shù)據(jù)干擾,因為很有可能會傳輸大量相反的1或0數(shù)據(jù)。通過串行鏈路傳輸

2024-01-03 06:35:04

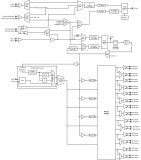

芯片上JESD204B協(xié)議對應(yīng)的引腳(SYSREF、SYNCINB和SERDOUT)與ZYNQ7015芯片中的JESD204 IP核的端口對應(yīng)相連。

2023-12-15 07:14:52

8位數(shù)用 lane0 傳輸,采樣點的低8位數(shù)用 lane1傳輸,如附件所示。但我在JESD204B的協(xié)議中并沒有找到這種映射方式。

請問您那里有沒有數(shù)據(jù)映射相關(guān)的詳細資料?我需要知道數(shù)據(jù)在串行通路上的確切映射信息,因為我需要寫接收端的程序。

2023-12-12 08:22:45

使用AD9680時遇到一個問題,AD9680采樣率為1Gsps,JESD204B IP核的GTX參考時鐘為250MHz,參數(shù)L=4,F(xiàn)=2,K=32,線速率為10Gbps,使用的為SYSREF

2023-12-12 08:03:49

我使用的是KC705板卡,調(diào)用了里面JESD204B的IP核,使用模式為interpolation值為4,4條鏈路,DAC頻率為2.5GHZ,通道速度為6.25GHZ,出現(xiàn)的問題是:

幀同步過程

2023-12-12 07:28:25

我現(xiàn)在需要一款FMC 子卡 ADC模塊用于測量低頻信號,F(xiàn)MCJESDADC1是否滿足我的需求?

2023-12-12 07:26:07

用單片AD9690采集數(shù)據(jù)給FPGA,不要求確定延遲,因此想要把AD9690配置在JESD204B sublcass 0 模式下。但是這種模式下,對于AD9690的SYSREF±的輸入管腳怎么處理?以及AD9690工作在subclass 0 模式下還有沒有其他要注意的地方?

2023-12-12 06:16:08

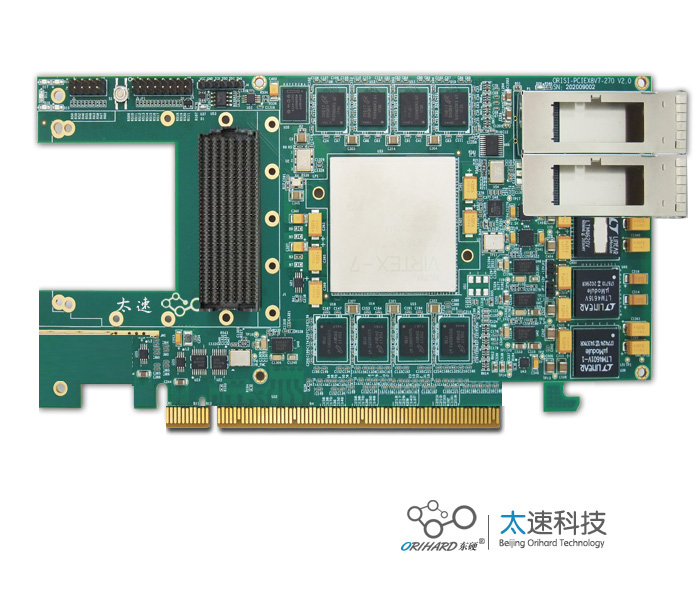

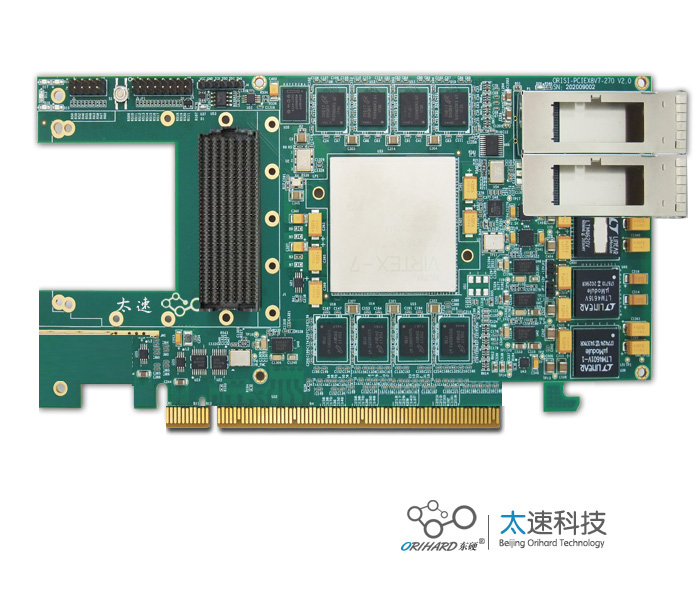

一、產(chǎn)品概述 基于PCIe的一款分布式高速數(shù)據(jù)采集系統(tǒng),實現(xiàn)多路AD的數(shù)據(jù)采集,并通過PCIe傳輸?shù)酱鎯τ嬎惴?wù)器,實現(xiàn)信號的分析、存儲。

產(chǎn)品固化FPGA邏輯,適配2路1Gsps/2路

2023-12-11 11:36:40

請問AD-FMCADC2-EBZ FMC Board 需要連接到VC707的哪個FMC接口?還是兩個FMC接口都可以

2023-12-11 06:46:56

模數(shù)轉(zhuǎn)換器AD9625的評估板AD-FMCADC3-EBZ能不能和賽靈思的Virtex7系列FPGA開發(fā)板連接,我看到他們都具備JESD204B接口,物理接口上能直接連嗎?還是說需要在使用轉(zhuǎn)換接口來連接?

2023-12-08 08:25:12

最近在使用AD9144芯片,調(diào)試JESD204B接口出現(xiàn)了一些問題,暫時沒有頭緒,期盼能得到各位的指點。

AD9144的主要配置如下:8條JESD204B鏈路,subclass1,速率為

2023-12-08 06:00:25

你好,因為項目需要,要做一塊數(shù)據(jù)采集和發(fā)生板,接口支持JESD204B,時鐘我選用了AD9523-1,電路我參考FMC-DAQ2開發(fā)板,舍棄了PLL1,直接在OSC_IN接入125M時鐘作參考,輸出

2023-12-06 07:48:32

的AD9162-FMX-EBZ板子,看到的現(xiàn)象是SYSREF信號一直為高,CGS測試信號不完全拉高,每次重新配置時拉高的lane通道數(shù)還不一樣。其界面設(shè)置如下圖所示。FPGA的使用是條用的xilinx的JESD204 IP核。

FPGA抓到的SYNC信號與SYSREF信號如下圖所示:

2023-12-05 08:23:30

使用內(nèi)部PLL,輸入?yún)⒖碱l率為100MHz。在采樣率時鐘設(shè)置為1GHz時,DAC的JESD204B鏈路能建立,但是當頻率改為1.5GHz時,SYNC一直為低。其他相關(guān)寄存器都已經(jīng)修改,serdes

2023-12-05 08:17:30

9680測試評估中遇到問題:

按照數(shù)據(jù)手冊中的配置步驟,關(guān)斷鏈路,通過0x570和0X56E寄存器快速配置JESD204B,鏈路上電后,電路鎖相環(huán)無法鎖定,204B無法正常輸出數(shù)據(jù)。

2023-12-05 08:04:26

復(fù)位,發(fā)出指令讓外部時鐘芯片產(chǎn)生一個sysref脈沖,脈寬是100ns,(實際示波器測到100ns)

此時鏈路建立,JESD204B接收核收到了有效采樣信號, 而且此處(控制位居然有兩位是拉高的?請問

2023-12-05 07:30:47

近期在使用AD9162時,配置的模式不成功,測試時鐘CLK發(fā)現(xiàn),CLK±單端信號共模電壓接近0V,手冊上是0.6V,但測試9162-FMC-EZB參考板上的CLK也是共模電壓為0V,請問這個會有什么影響嗎?

我們現(xiàn)在測試配置JESD204B接口模式不正確,不確定是否CLK的影響?

2023-12-05 06:14:24

決。

我配置基本參數(shù)為DAC速率6G,6倍插值,JESD204B線速率5G。L=8,M=2,F=1,S=2.SYSREF=3.90625MHz.

2023-12-04 07:30:17

AD9164 JESD204B接口的傳輸層是如何對I/Q數(shù)據(jù)進行映射的

2023-12-04 07:27:34

大佬好,小弟最近在調(diào)試AD9136芯片,遇到一個問題,如下:

1.我使用的是9136模式11,單鏈路模式,使用一個JESD204+一個JESD204 PHY,我將JESD204的tx_charisk

2023-12-04 07:14:58

我在測AD9154-FMC-EBZ的時候發(fā)現(xiàn)在WIN10的環(huán)境下無法打開DPGDownloaderLite,ACE無法正檢測到AD9154-FMC-EBZ和ADS7-V2-EBZ正常鏈接,如圖

2023-12-01 08:29:59

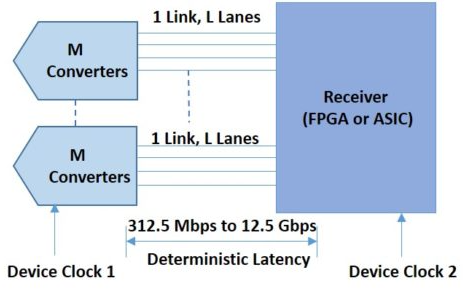

在AD9680和AD9690數(shù)據(jù)手冊上,寫著它們[size=200%]支持的最小通道線率是3125Mbps,但是在JESD204B標準手冊寫著最小通道線率是312.5Mbps。

我疑惑這是數(shù)據(jù)手冊的錯誤,還是AD9680和AD9690這兩款芯片支持的最低通道線率確實時3125Mbps

2023-12-01 07:57:58

概述 AD-FMCMotcon1-EBZ提供有效的電機控制解決方案,用于不同類型的電機中。每 個FPGA接口卡(FMC)可驅(qū)動一個步進、兩個有刷直流(BDC)、兩個無刷直流(BLDC) 或兩個永磁

2023-11-28 16:10:36 0

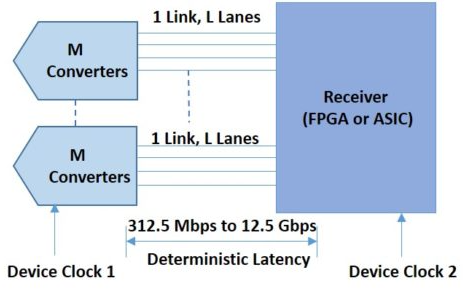

0 作者:Ian Beavers,ADI公司應(yīng)用工程師 JESD204B串行數(shù)據(jù)鏈路接口針對支持更高速轉(zhuǎn)換器不斷增長的帶寬需求而開發(fā)。作為第三代標準,它提供更高的通道速率最大值(每通道高達12.5

2023-11-28 14:24:47 0

0 電子發(fā)燒友網(wǎng)站提供《JESD204B規(guī)范的傳輸層介紹.pdf》資料免費下載

2023-11-28 10:43:31 0

0 、TSW14J57EVM 產(chǎn)品描述1.產(chǎn)品特性TI TSW14J57 評估模塊 (EVM) 是下一代數(shù)據(jù)采集卡,用于評估全新 TI JESD204B 系列高速模數(shù)轉(zhuǎn)換器 (ADC

2023-11-21 15:05:23

前言以下是本篇文章正文內(nèi)容,下面案例可供參考一、AD9154-FMC-EBZ 產(chǎn)品描述1.AD9154-FMC-EBZ 產(chǎn)品特性PRODUCT HIGHLIGHTS1. Ultrawide

2023-11-09 11:07:54

1.3Gsps 14-bit JESD204B 64-Pin LFCSP EP TrayProduct Technical SpecificationsECCN (US)3A

2023-11-07 19:19:38

電子發(fā)燒友網(wǎng)為你提供ADI(ADI)AD9094: 8-Bit, 1 GSPS, JESD204B, Quad Analog-to-Digital Converter Data Sheet相關(guān)產(chǎn)品

2023-10-17 19:13:59

電子發(fā)燒友網(wǎng)為你提供ADI(ADI)AD9207: 12-Bit, 6 GSPS, JESD204B/JESD204C Dual ADC Data Sheet相關(guān)產(chǎn)品參數(shù)、數(shù)據(jù)手冊,更有AD9207

2023-10-16 19:02:55

容量

?FPGA 外掛2組FMC HPC 連接器;

?FPGA 引出1路QSPF+,數(shù)據(jù)速率25GbpsX4/s;

?FPGA與DSP之間通過RapidIO互聯(lián) 。

?VPX 連接器上外接FPGA

2023-10-16 11:12:06

LogiCORE IP JESD204內(nèi)核實現(xiàn)了一個JESD204B接口,使用GTX、GTH、GTP或GTY(僅限UltraScale和UltraScale+)收發(fā)器在1至8個通道上支持1至12.5

2023-10-16 10:57:17 358

358

電子發(fā)燒友網(wǎng)為你提供ADI(ADI)AD9694-EP: 14比特、500 MSPS、JESD204B、“四向數(shù)字轉(zhuǎn)換器”強化產(chǎn)品數(shù)據(jù)表相關(guān)產(chǎn)品參數(shù)、數(shù)據(jù)手冊,更有AD9694-EP: 14比特

2023-10-09 19:12:15

電子發(fā)燒友網(wǎng)為你提供ADI(ADI)AD9694S: 14-Bit, 500 MSPS, JESD 204B, 二次對數(shù)字轉(zhuǎn)換器數(shù)據(jù)表相關(guān)產(chǎn)品參數(shù)、數(shù)據(jù)手冊,更有AD9694S: 14-Bit

2023-10-08 16:48:36

STM32的FSMC和FMC有什么區(qū)別呢?

有的系列,比如F103是FSMC,有的系列,M4就是FMC了。這兩者有什么區(qū)別呢?

2023-09-26 06:17:01

電子發(fā)燒友網(wǎng)站提供《一種基于JESD204B的射頻信號高速采集系統(tǒng).pdf》資料免費下載

2023-09-14 11:14:07 1

1 AD9144是一款支持jesd204b協(xié)議高速DAC芯片。AD9144-FMC-EBZ是基于AD9144的評估板(Evaluation Board),它是主要由AD9144,AD9516,與PIC16F單片機組成的系統(tǒng)。

2023-09-13 09:20:22 997

997

輸入帶寬可達9GHz。QT7331A為3GSPS采樣率,QT7331B為2.6GSPS采樣率,QT7331C為2GSPS采樣率。本板卡支持觸發(fā)輸入或者輸出;內(nèi)參考、外參考、外時鐘三種時鐘方式,可通過SPI總線實現(xiàn)時鐘源選擇。通過參考時鐘可實現(xiàn)多個板卡的同步。

2023-09-09 19:28:57 430

430

x8,LA、HA、HB接口。

單組GTH引腳分布不要跨越FPGA Bank。

在板卡布局時建議分散布局,更容易適配子卡。

2)FPGA 外接2 QSFP+接口。

3)FPGA 外接1個

2023-09-08 15:07:12

APROM了?

2.P356頁流程圖D入口右邊,Page 0 is mapping to LDROM.與P348表格CBS=00時不符.

3.CBS=11或01與CBS=10或00時的區(qū)別。P355流程圖

2023-08-25 06:30:17

、JESD204B、Serial Rapid I/O*、通用公共射頻接口 (CPRI) 和 IEEE 1588 等協(xié)議。

2023-07-29 10:41:27 823

823

· ADC采用TI的ADS62P49,2通道250M,14bit,共1片;

· DAC采用ADI的AD9122,2通道,16bit,可達1.2G,共1片;

· 時鐘采用AD9516,支持板上時鐘和外接時鐘;

· 共6個SSMB接口,1個FMC/LPC接口

2023-07-28 14:33:27 403

403

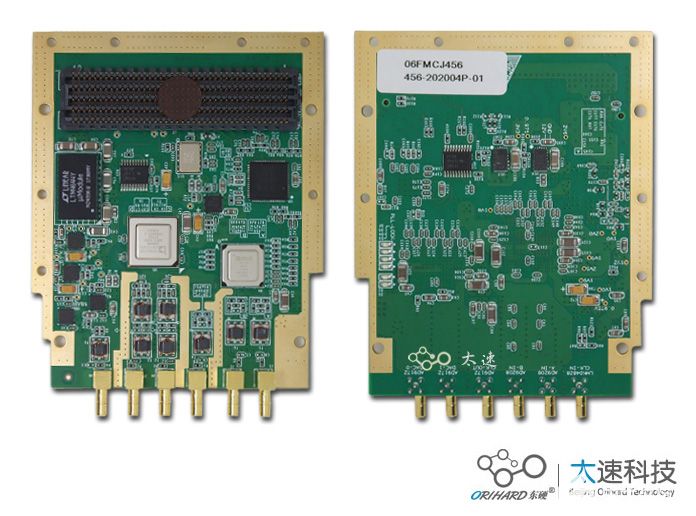

板卡為標準FMC接口子卡, ADC采用兩片TI的ADS54J60, 4通道1Gsps,16bit, DAC采用2片 TI的DAC39J84 ,4通道 16bit 1.25Gsps 時鐘采用HMC7044,支持板上時鐘和外接時鐘; 共10個SSMB接口,1個FMC/HPC接口。

2023-07-14 11:01:54 454

454

本文旨在提供發(fā)生 JESD204B 鏈路中斷情況下的調(diào)試技巧簡介

2023-07-10 16:32:03 802

802

ADRV9009是一款高集成度射頻(RF)、捷變收發(fā)器,提供雙通道發(fā)射器和接收器、集成式頻率合成器以及數(shù)字信號處理功能。這款I(lǐng)C具備多樣化的高性能和低功耗組合,FMC子卡為2路輸入,2路輸出的射頻收發(fā)卡,配合FPGA工作滿足3G、4G和5G宏蜂窩時分雙工(TDD)基站應(yīng)用要求。

2023-07-05 15:51:25 581

581

請問大家,為什么FMC_Erase返回總是-1,主函數(shù)中PE0,PE1,PE2是我的三個按鍵,我主要是想實驗對flash的擦寫,將數(shù)據(jù)存到flash中,實現(xiàn)掉電數(shù)據(jù)不丟失,但現(xiàn)在一個插除頁都是失敗

2023-06-27 06:56:47

FMC-1AD2DA是我司自主研發(fā)的一款1路1G AD采集、1路2.5G DA回放的FMC子卡。板卡采用標準FMC子卡架構(gòu),可方便的與其他FMC板卡實現(xiàn)高速互聯(lián),可廣泛用于高頻模擬信號采集、雷達系統(tǒng)測試等場合。

2023-06-25 14:45:05 369

369

該芯片是高性能時鐘調(diào)節(jié)器,支持JEDEC JESD204B。當使用設(shè)備和 SYSREF 時鐘時,PLL2 的 14 個時鐘輸出可配置去驅(qū)動 7 個JESD204B 轉(zhuǎn)換器或其他邏輯設(shè)備。

2023-06-25 10:13:46 848

848 SC6301是高性能時鐘調(diào)節(jié)器,支持JEDEC JESD204B。當使用設(shè)備和SYSREF時鐘時,PLL2的14個時鐘輸出可配置去驅(qū)動7個JESD204B轉(zhuǎn)換器或其他邏輯設(shè)備。

2023-06-21 15:11:14 508

508

SC6301是高性能時鐘調(diào)節(jié)器,支持JEDEC JESD204B。當使用設(shè)備和SYSREF時鐘時,PLL2的14個時鐘輸出可配置去驅(qū)動7個JESD204B轉(zhuǎn)換器或其他邏輯設(shè)備。SYSREF可以使用直流和交流耦合來提供。不僅限于JESD204B應(yīng)用,14個輸出均可單獨配置為傳統(tǒng)高性能時鐘系統(tǒng)輸出。

2023-06-21 15:10:58 608

608

BOARD EVAL W/FMC CONN FPGA DEV

2023-06-19 13:48:33

生效。

示范程序如下:

uint32_tau32Config[2];

SYS_UnlockReg();

FMC_Open();

FMC_ReadConfig(au32Config, 2

2023-06-19 07:03:23

SYSREF計時校準▲樣片標記時間戳■JESD204B串行數(shù)據(jù)接口:▲支持子類0和1▲最大通道速率:12.8Gbps▲多達16個通道可降低通道速率■雙通道模式下的數(shù)字下變頻器:▲實際輸出:DDC旁路或

2023-06-16 14:37:21

您的PCB可以處理高達12.5Gbps的速度嗎,感到驚訝,對嗎?JESD204B標準為串行接口提供高達12.5Gbps的比特率。這種升級允許設(shè)計人員在FPGA/ASIC上使用更少的收發(fā)器,從而減少

2023-05-26 14:50:57 608

608

JESD204B規(guī)范是JEDEC標準發(fā)布的較新版本,適用于數(shù)據(jù)轉(zhuǎn)換器和邏輯器件。如果您正在使用FPGA進行高速數(shù)據(jù)采集設(shè)計,您會聽到新的流行詞“JESD204B”。與LVDS和CMOS接口相比,這一較新的版本具有顯著的優(yōu)勢,因為它包括更簡單的布局和更少的引腳數(shù)。

2023-05-26 14:49:31 361

361

口,支持PCIe X 16 ReV3.0以及 FMC+ 擴展接口。板卡提供一路標準 FMC+ 接口,該接口符合 ANSI/VITA 57.4 標準,可以根據(jù)應(yīng)用需求靈活地選擇 FMC+ 或者FMC 子卡,比如 ADC 子卡、DAC 子卡以及光纖子卡等。同時可支持 Windows,Linux 上位機驅(qū)動。

2023-05-24 17:58:00 651

651

互聯(lián),可適配各種FMC AD/DA卡,可適配國內(nèi)外標準的各種FMC或FMC+子卡n 板卡采用QSFP+連接器互聯(lián),帶寬≥5GB/sn 單電源+6V~+12V供電,支持插入標準服務(wù)器或單獨千兆、萬兆網(wǎng)口

2023-05-21 18:27:41

大部分的ADC和DAC都支持子類1,JESD204B標準協(xié)議中子類1包括:傳輸層,鏈路層,物理層。在少部分資料中也會介紹含有應(yīng)用層,應(yīng)用層是對JESD204B進行配置的接口,在標準協(xié)議中是不含此層,只是為了便于理解,添加的一個層。

2023-05-10 15:52:55 1376

1376

的K7-325T或K7-410T FPGA,DDR3的存儲容量可選配2GByte或4GByte。板載有1個FMC-HPC全互聯(lián)的接口,可以適配大多數(shù)ADC/DAC FMC子卡。

應(yīng)用行業(yè)1)無線電監(jiān)測與測向定位

2023-05-09 20:07:51

Cadence Allegro 之一。

4,具有高速數(shù)據(jù)傳輸及模數(shù)轉(zhuǎn)換設(shè)計和經(jīng)驗者優(yōu)先,包括基于LVDS或JESD204B 接口的高速ADC/DAC 、DDR3\\4 和千兆以太網(wǎng)等模塊的設(shè)計與布線。

5

2023-04-28 09:38:20

KAD-FMC-EVALZ 用戶指南

2023-04-27 18:48:28 0

0 LMK04821系列器件為該話題提供了很好的范例研究素材,因為它們是高性能的雙環(huán)路抖動清除器,可在具有器件和SYSREF時鐘的子類1時鐘方案里驅(qū)動多達七個JESD204B轉(zhuǎn)換器或邏輯器件。圖1是典型JESD204B系統(tǒng)(以LMK04821系列器件作為時鐘解決方案)的高級方框圖。

2023-04-18 09:25:30 919

919

2 組 64bit 的DDR4 SDRAM,每組容量2GB,可穩(wěn)定運行在2400MT/s。支持PCIE Gen3 x8模式及一路FMC HPC接口。同時可提供 Windows,Linux 上位機驅(qū)動

2023-04-13 15:56:21

, 0 ), /* fm0 */ FMC_APPLY_ORDER( 1, FMCPortStart , 0 ), /* fm0/port/MAC/3 */ FMC_APPLY_ORDER( 2

2023-04-11 07:10:25

BOARD DEMO FMC

2023-03-30 12:04:42

Xilinx FMC-Supported Boards - Adapter Board

2023-03-30 12:04:39

BOARD INTERPOSER ADC FMC HS

2023-03-30 12:04:39

AD9135 EVALUATION BOARD W/ FMC C

2023-03-30 11:50:32

AD9136 EVALUATION BOARD W/ FMC C

2023-03-30 11:50:28

EVAL BOARD FOR AD9154-FMC

2023-03-30 11:50:27

KIT DEV FOR Z8 ENCORE Z8FMC16100

2023-03-30 11:41:48

KIT DEV FOR ZNEO Z16FMC

2023-03-29 22:53:25

KIT DEV FOR Z8 ENCORE Z8FMC16100

2023-03-29 22:53:25

EMULATOR ICE FOR Z8FMC16100

2023-03-29 22:45:56

AD9174-FMC-EBZ

2023-03-29 21:50:41

電子發(fā)燒友App

電子發(fā)燒友App

評論